Содержание

- 2. При рассмотрении запоминающих устройств учитывают следующие характеристики: - место расположения; - емкость; - единица пересылки; -

- 3. По месту расположения ЗУ разделяют на: - процессорные, - внутренние - внешние. Наиболее скоростные виды памяти

- 4. Емкость ЗУ характеризуют числом битов или байтов, которое может храниться в запоминающем устройстве. Важной характеристикой ЗУ

- 5. Различают четыре основных метода доступа: - последовательный доступ, при котором ЗУ ориентировано на хранение информации в

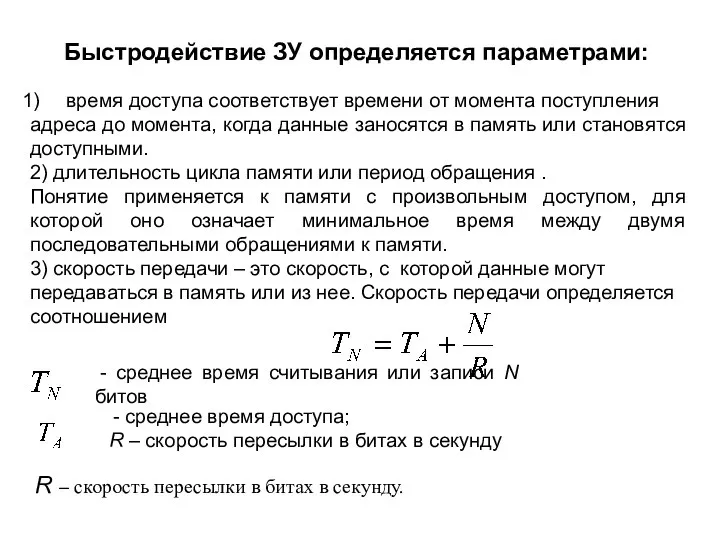

- 6. Быстродействие ЗУ определяется параметрами: время доступа соответствует времени от момента поступления адреса до момента, когда данные

- 7. Физический тип ЗУ определяется технологией изготовления. Применяются три наиболее распространенных технологии: полупроводниковая память, память с магнитным

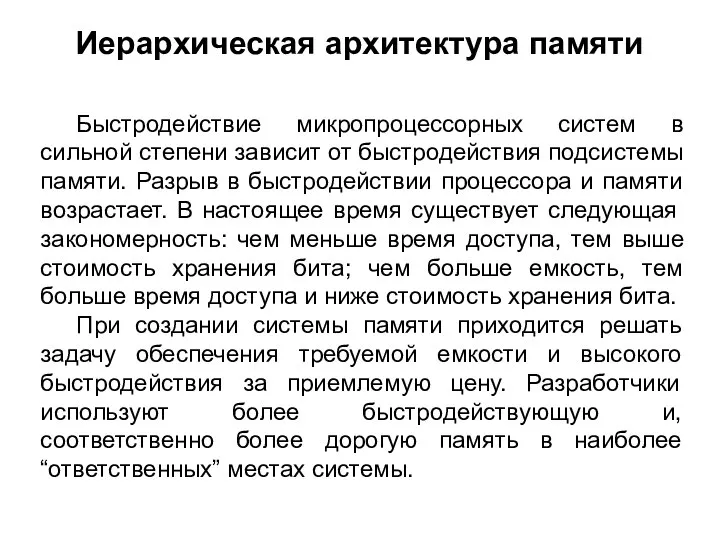

- 8. Быстродействие микропроцессорных систем в сильной степени зависит от быстродействия подсистемы памяти. Разрыв в быстродействии процессора и

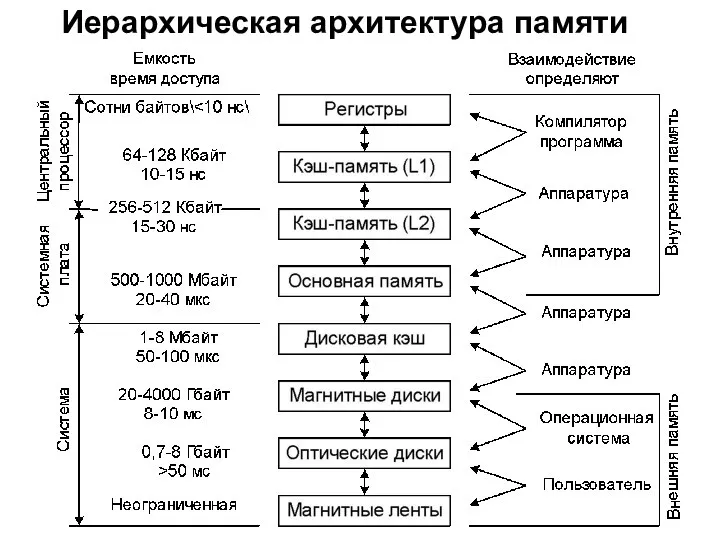

- 9. Иерархическая архитектура памяти

- 10. Иерархическая архитектура состоит из запоминающих устройств различного типа, которые, в зависимости от характеристик, относят к определенному

- 11. По мере движения вниз по иерархической структуре: - возрастает емкость - возрастает время доступа - уменьшается

- 12. Основная память, значительно большей емкости, располагается несколькими уровнями ниже. Между регистрами ЦП и основной памятью размещают

- 13. Иерархия может быть дополнена и другими видами памяти. Некоторые модели вычислительных машин включают так называемую расширенную

- 14. Основная память Основная память представляет собой единственный вид памяти, к которой ЦП может обращаться непосредственно. Информация,

- 15. Большую часть основной памяти составляет оперативная память, называемая так, потому что ОЗУ допускает как запись, так

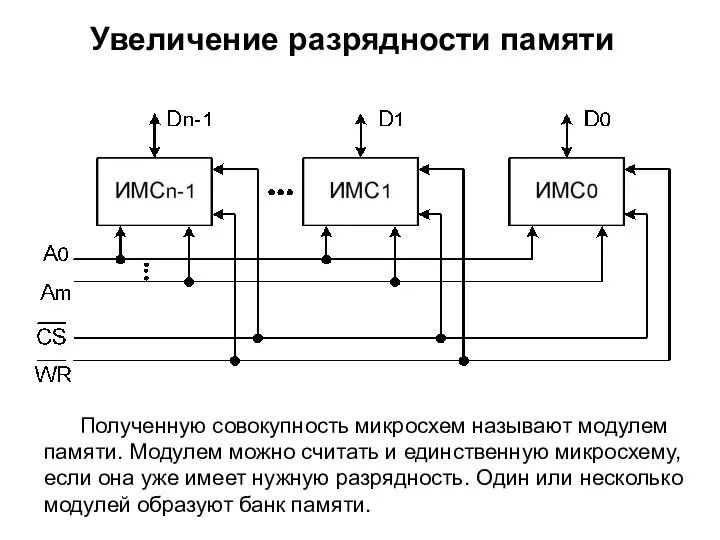

- 16. Блочная организация основной памяти Для реализации основной памяти большого объема (что актуально в современных вычислительных машинах)

- 17. Увеличение разрядности памяти Полученную совокупность микросхем называют модулем памяти. Модулем можно считать и единственную микросхему, если

- 18. Для получения требуемой емкости нужно определенным образом объединить несколько банков памяти меньшей емкости. В общем случае

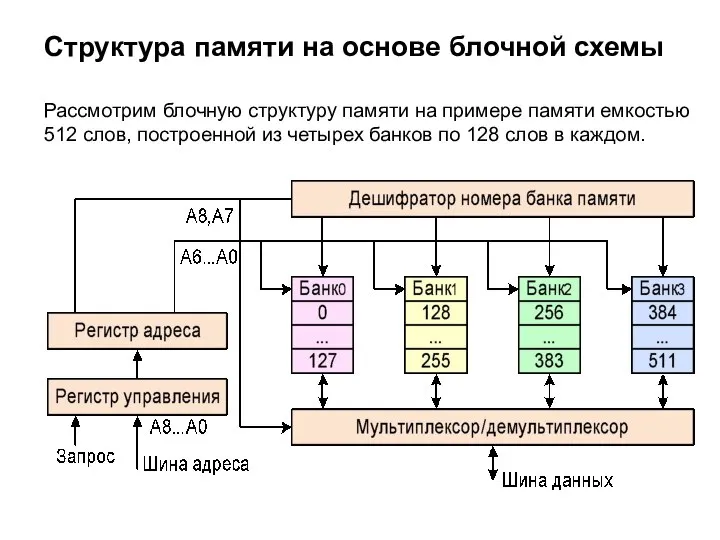

- 19. Рассмотрим блочную структуру памяти на примере памяти емкостью 512 слов, построенной из четырех банков по 128

- 20. Адресное пространство памяти разбито на группы последовательных адресов, и каждая такая группа обеспечивается отдельным банком памяти.

- 21. Расслоение памяти Блочное построение памяти позволяет не только наращивать емкость, но и сократить время доступа к

- 22. Блочная память с чередованием адресов по циклической схеме

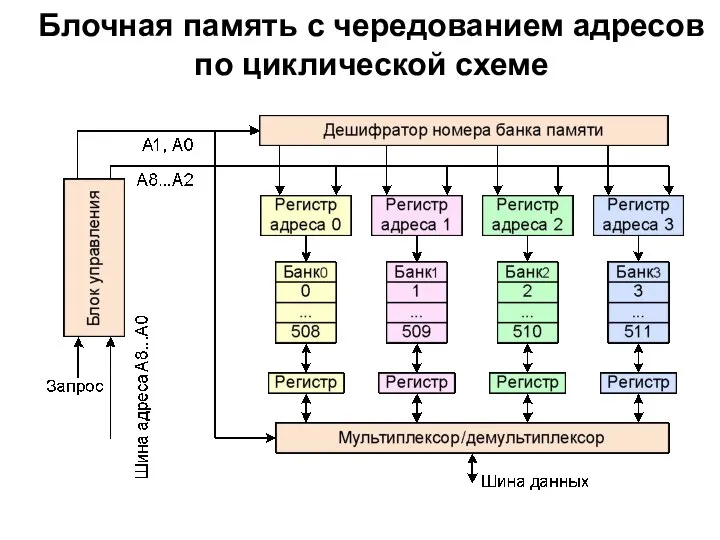

- 23. Рассмотрим пример блочной памяти с чередованием адресов по циклической схеме (рисунок 4), в котором для выбора

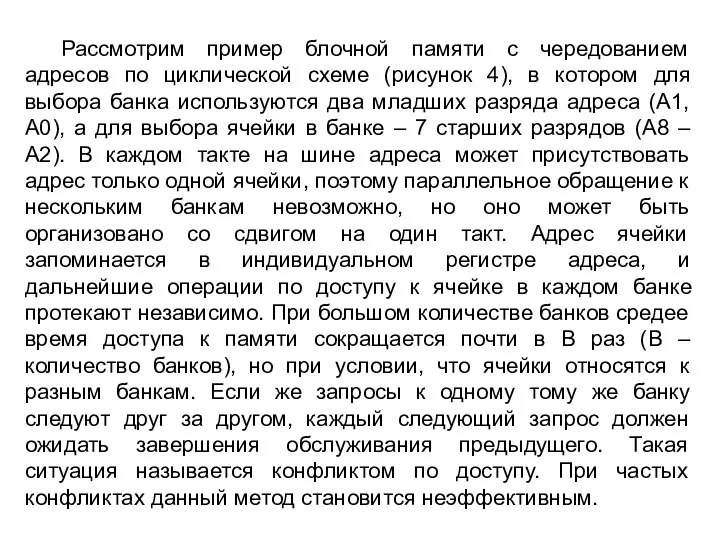

- 24. Блочно-циклическая схема расслоения памяти В блочно-циклической схеме расслоения памяти каждый банк состоит из нескольких модулей, адресуемых

- 25. Структура микросхемы памяти

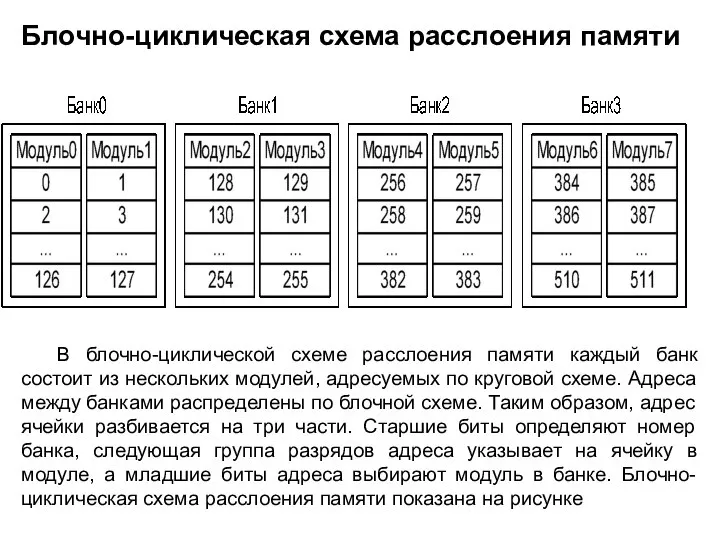

- 26. Интегральные микросхемы (ИМС) памяти организованы в виде матрицы ячеек, каждая из которых, в зависимости от разрядности

- 27. Адрес ячейки, поступающий по шине адреса, пропускается через логику выбора, где он разделяется на две составляющие:

- 28. Совокупность запоминающих элементов и логических схем, связанных с выбором строк и столбцов, называют ядром микросхемы памяти.

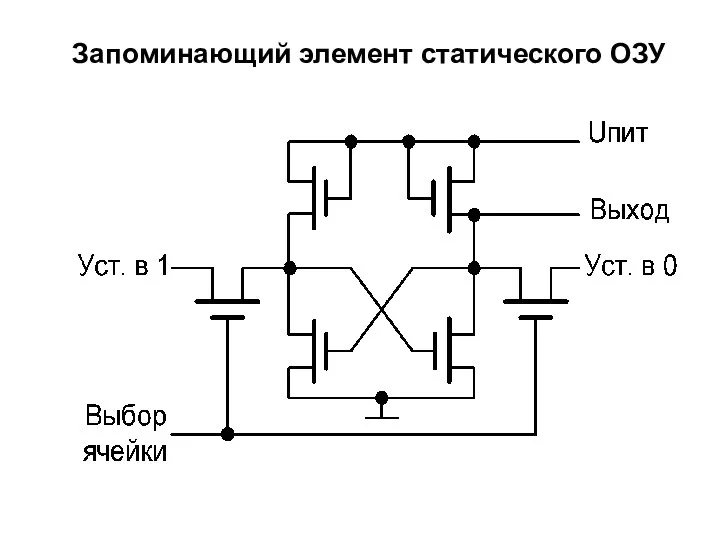

- 29. Статическая и динамическая оперативная память В статических ОЗУ запоминающий элемент может хранить записанную информацию неограниченно долго

- 30. Схема с четырьмя транзисторами обеспечивает большую емкость микросхемы, однако у такой схемы большой ток утечки, а

- 31. Запоминающий элемент статического ОЗУ

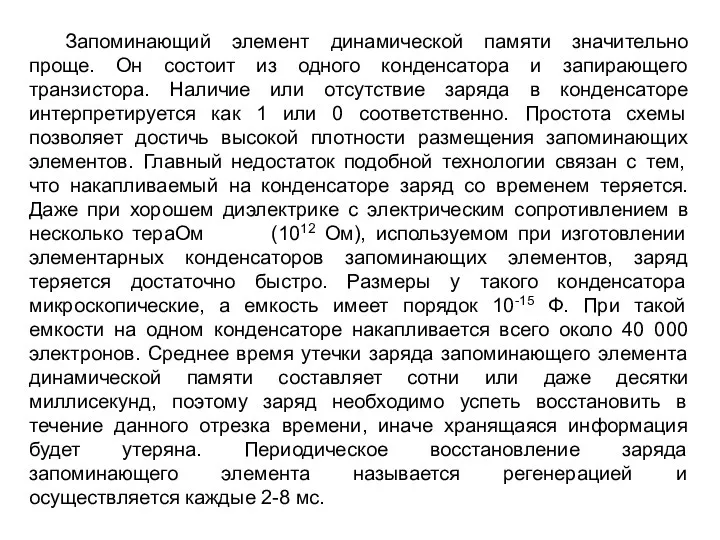

- 32. Запоминающий элемент динамической памяти значительно проще. Он состоит из одного конденсатора и запирающего транзистора. Наличие или

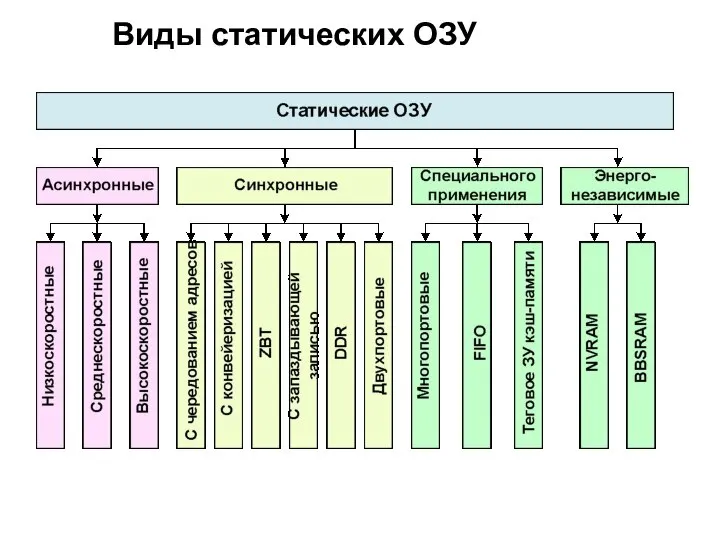

- 33. Виды статических ОЗУ

- 34. Асинхронные статические ОЗУ: время доступа составляло 15-20 нс (в лучшем случае — 12 нс) Синхронные статические

- 35. Структура двухпортового ОЗУ

- 36. Стандартное однопортовое ОЗУ имеет по одной шине адреса, данных и управления и в каждый момент времени

- 37. В двухпортовой памяти имеются два набора адресных, информационных и управляющих сигнальных шин, каждый из которых обеспечивает

- 38. Помимо возможности доступа к ячейкам с двух направлений, двухпортовая память снабжается средствами для обмена сообщениями между

- 40. Скачать презентацию

Общая характеристика ресурсной базы социально-культурной деятельности

Общая характеристика ресурсной базы социально-культурной деятельности Новая Редполитика

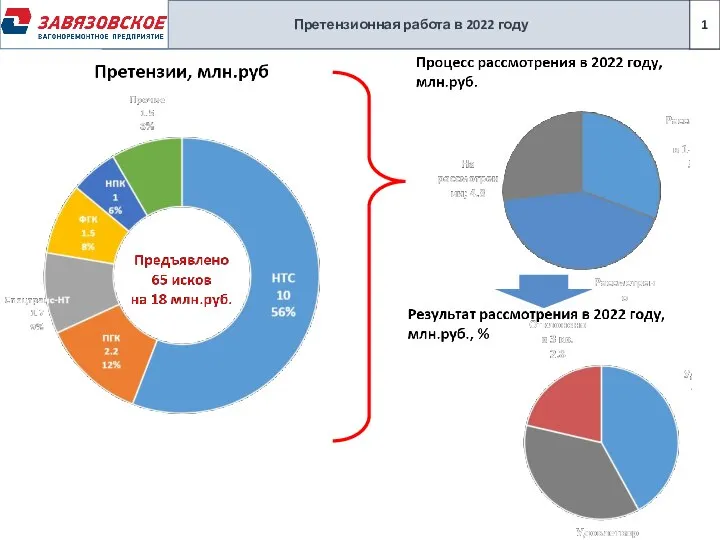

Новая Редполитика Претензии

Претензии История немецкой валюты

История немецкой валюты Современные средства оснащения образовательных учреждений

Современные средства оснащения образовательных учреждений Картинная галерея. Пейзажи

Картинная галерея. Пейзажи Александр III и его внутренняя политика

Александр III и его внутренняя политика Нумерация. Счёт предметов. Разряды

Нумерация. Счёт предметов. Разряды Дед Мороз и Снегурочка

Дед Мороз и Снегурочка Пушкинские места

Пушкинские места Традиции духовно-нравственного воспитания у народов России

Традиции духовно-нравственного воспитания у народов России Презентация на тему Разряды наречий по значению

Презентация на тему Разряды наречий по значению Времена года в творчестве А.С.Пушкина

Времена года в творчестве А.С.Пушкина Авторское право

Авторское право Ученик года-2021 6 а класс

Ученик года-2021 6 а класс От пандоры до модели…

От пандоры до модели… Применение лазерных технологий в обработке материалов в ювелирной отрасли

Применение лазерных технологий в обработке материалов в ювелирной отрасли Российские программы с мировым именем!

Российские программы с мировым именем! Как не разбиться в тумане

Как не разбиться в тумане Игровая технология

Игровая технология Firmensortiment

Firmensortiment Оценка и моделирование пенсионных обязательств

Оценка и моделирование пенсионных обязательств Занятость и социальная защита населения

Занятость и социальная защита населения Помещение на ул. Греческая, д. 69, г. Таганрог

Помещение на ул. Греческая, д. 69, г. Таганрог Совместная проектная деятельность обучающихся как инструмент творческой интеграции

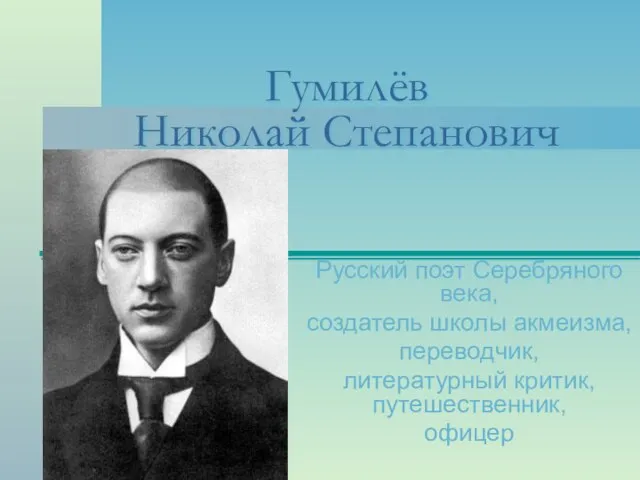

Совместная проектная деятельность обучающихся как инструмент творческой интеграции Гумилёв Николай Степанович

Гумилёв Николай Степанович Презентация на тему Что такое ноосфера

Презентация на тему Что такое ноосфера  Высокое возрождение. Леонардо да Винчи. Рафаэль Санти

Высокое возрождение. Леонардо да Винчи. Рафаэль Санти