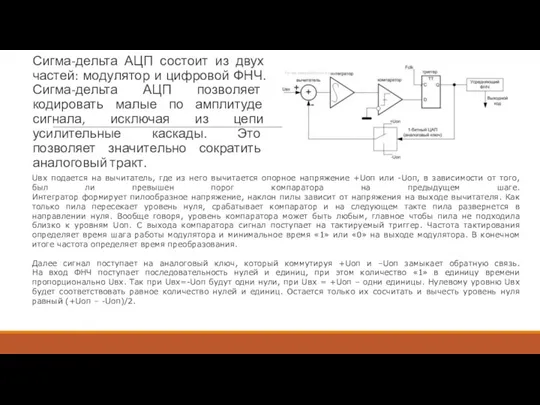

позволяет кодировать малые по амплитуде сигнала, исключая из цепи усилительные каскады. Это позволяет значительно сократить аналоговый тракт.

Uвх подается на вычитатель, где из него вычитается опорное напряжение +Uоп или -Uоп, в зависимости от того, был ли превышен порог компаратора на предыдущем шаге.

Интегратор формирует пилообразное напряжение, наклон пилы зависит от напряжения на выходе вычитателя. Как только пила пересекает уровень нуля, срабатывает компаратор и на следующем такте пила развернется в направлении нуля. Вообще говоря, уровень компаратора может быть любым, главное чтобы пила не подходила близко к уровням Uоп. С выхода компаратора сигнал поступает на тактируемый триггер. Частота тактирования определяет время шага работы модулятора и минимальное время «1» или «0» на выходе модулятора. В конечном итоге частота определяет время преобразования.

Далее сигнал поступает на аналоговый ключ, который коммутируя +Uоп и –Uоп замыкает обратную связь.

На вход ФНЧ поступает последовательность нулей и единиц, при этом количество «1» в единицу времени пропорционально Uвх. Так при Uвх=-Uоп будут одни нули, при Uвх = +Uоп – одни единицы. Нулевому уровню Uвх будет соответствовать равное количество нулей и единиц. Остается только их сосчитать и вычесть уровень нуля равный (+Uоп – -Uоп)/2.

Городки история, правила игры

Городки история, правила игры Образование XVI-XVII

Образование XVI-XVII Проектирование участка механического цеха для изготовления детали: ДИСК 153.38-22-16

Проектирование участка механического цеха для изготовления детали: ДИСК 153.38-22-16 СИТИ-FM ноябрь, 2011

СИТИ-FM ноябрь, 2011 Нестеров М.В. Картины

Нестеров М.В. Картины Среда языка программирования Pascal ABC

Среда языка программирования Pascal ABC Рекомендации для архивов бахаи Составлено Национальным архивом бахаи Национального Духовного Собрания бахаи Соединенных Штато

Рекомендации для архивов бахаи Составлено Национальным архивом бахаи Национального Духовного Собрания бахаи Соединенных Штато У каждого внимательного читателя свой Булгаков…

У каждого внимательного читателя свой Булгаков… Т-34 Клаус Ягер

Т-34 Клаус Ягер Использование проектной технологии в обучении географии

Использование проектной технологии в обучении географии Четыре замечательные точки треугольника

Четыре замечательные точки треугольника Виды ДТП: Столкновение Опрокидывание Наезд

Виды ДТП: Столкновение Опрокидывание Наезд Древний Восток_лекция04 (этно-языковая карта)

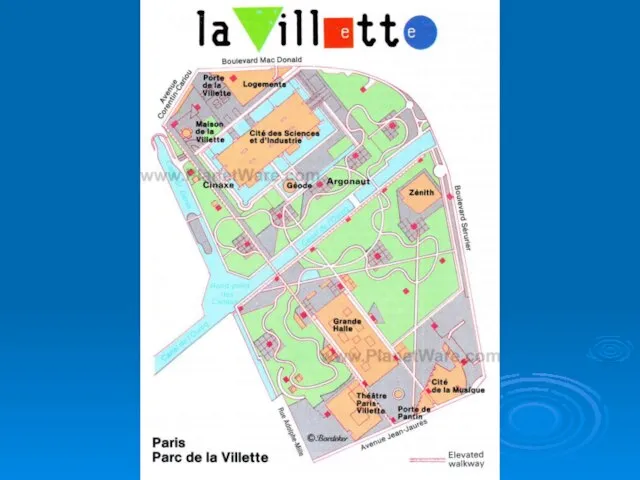

Древний Восток_лекция04 (этно-языковая карта) Является третьим по посещаемости музейным центром Парижа после Лувра и Центра Помпиду и пятым культурным учреждением Франции. Пар

Является третьим по посещаемости музейным центром Парижа после Лувра и Центра Помпиду и пятым культурным учреждением Франции. Пар Фонетика. Звуки и буквы. Фонетический анализ слова. Общие сведения

Фонетика. Звуки и буквы. Фонетический анализ слова. Общие сведения Методологическая основа ТО и Системный подход

Методологическая основа ТО и Системный подход На примере Реабилитационного Центра «Новая Жизнь» (Ленинградская область, Россия) Докладчик: Алексей Фомичев

На примере Реабилитационного Центра «Новая Жизнь» (Ленинградская область, Россия) Докладчик: Алексей Фомичев Теоретические основы маркетинга

Теоретические основы маркетинга Фирма BMW. Баварские моторные заводы

Фирма BMW. Баварские моторные заводы Презентация на тему Периодика для детей 2-3 класс

Презентация на тему Периодика для детей 2-3 класс Информационная система ВыпускникПлюс

Информационная система ВыпускникПлюс Африка растительный и животный мир

Африка растительный и животный мир Уважение к закону и обязанности гражданина

Уважение к закону и обязанности гражданина Организация работы овощного цеха

Организация работы овощного цеха Диагностическая программа в системе предшкольного образования

Диагностическая программа в системе предшкольного образования Алгоритмические основы разработки поисковой системы

Алгоритмические основы разработки поисковой системы Тра́нспорт. 2 категории транспорта

Тра́нспорт. 2 категории транспорта Программа информатизации

Программа информатизации