Содержание

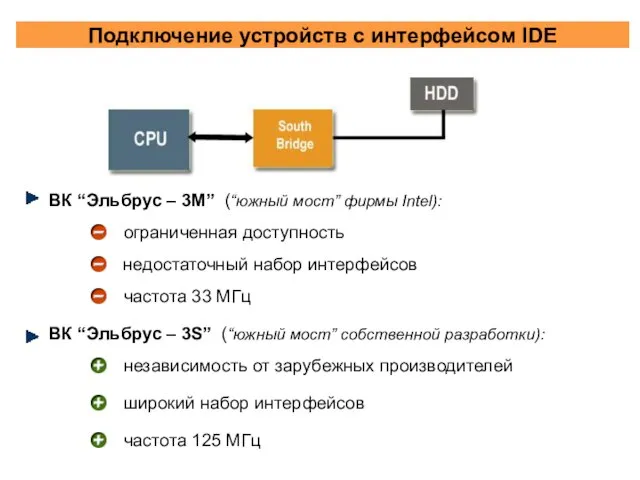

- 2. Подключение устройств с интерфейсом IDE ВК “Эльбрус – 3М” (“южный мост” фирмы Intel): ВК “Эльбрус –

- 3. Задачи разработать контроллер шины IDE, поддерживающий работу с интерфейсом IO-link разработать стенд для отладки и тестирования

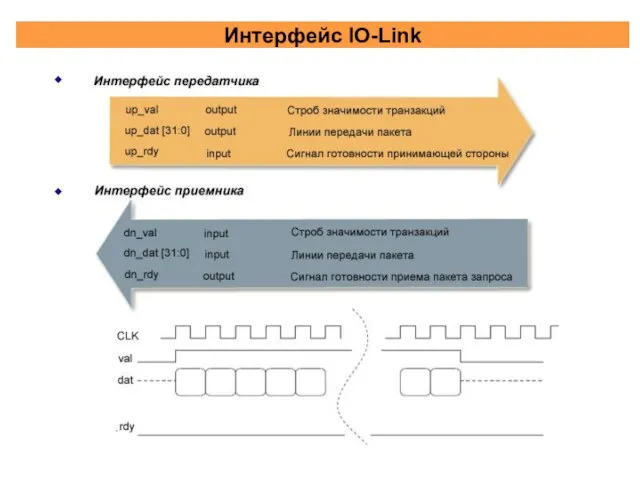

- 4. Интерфейс IO-Link

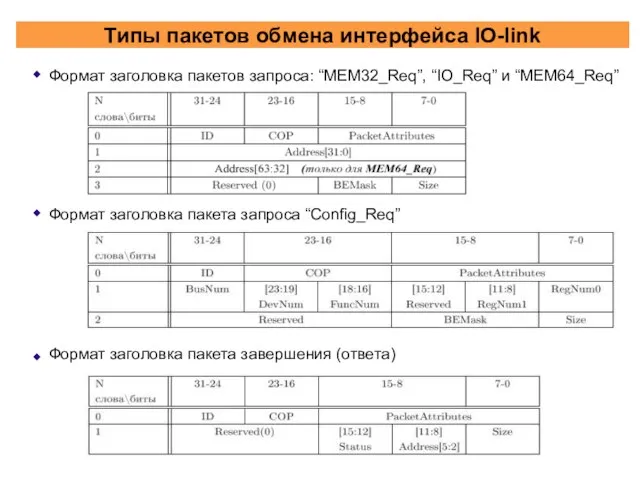

- 5. Типы пакетов обмена интерфейса IO-link Формат заголовка пакетов запроса: “MEM32_Req”, “IO_Req” и “MEM64_Req” Формат заголовка пакета

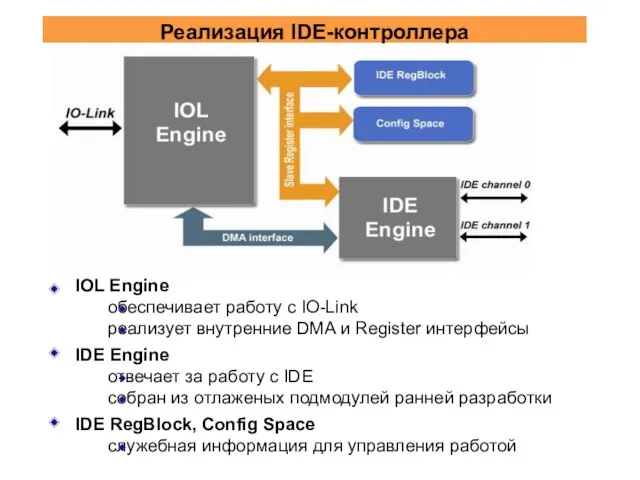

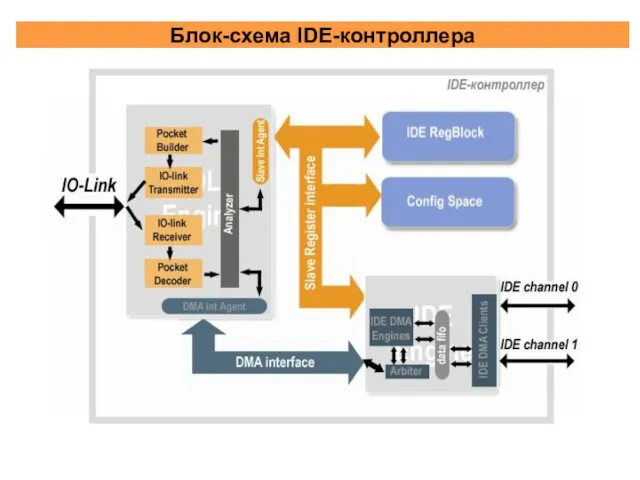

- 6. Реализация IDE-контроллера IOL Engine обеспечивает работу с IO-Link реализует внутренние DMA и Register интерфейсы IDE Engine

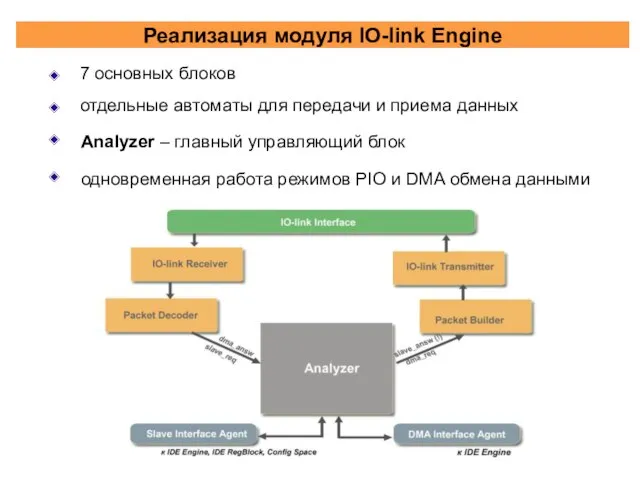

- 7. Реализация модуля IO-link Engine 7 основных блоков отдельные автоматы для передачи и приема данных Analyzer –

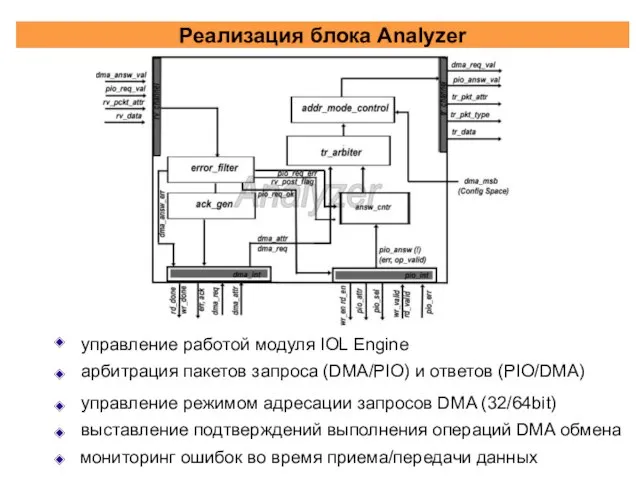

- 8. Реализация блока Analyzer управление работой модуля IOL Engine арбитрация пакетов запроса (DMA/PIO) и ответов (PIO/DMA) управление

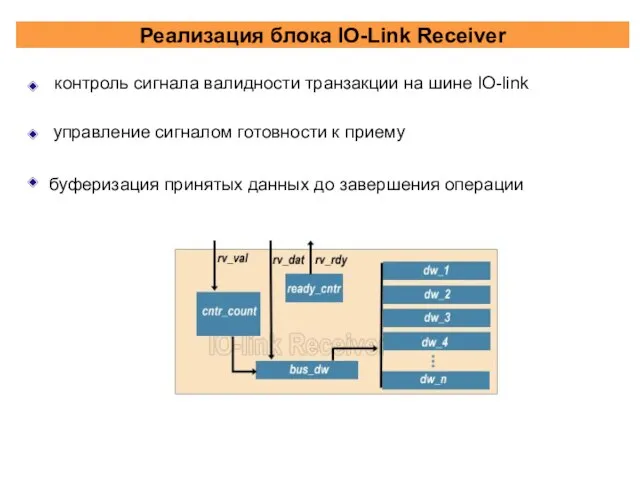

- 9. Реализация блока IO-Link Receiver контроль сигнала валидности транзакции на шине IO-link управление сигналом готовности к приему

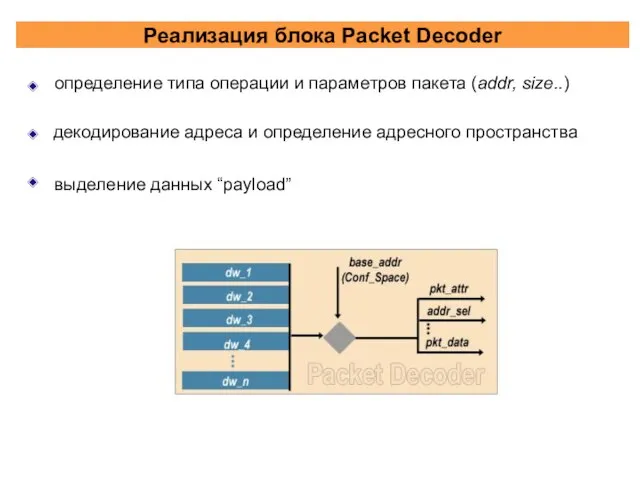

- 10. Реализация блока Packet Decoder определение типа операции и параметров пакета (addr, size..) декодирование адреса и определение

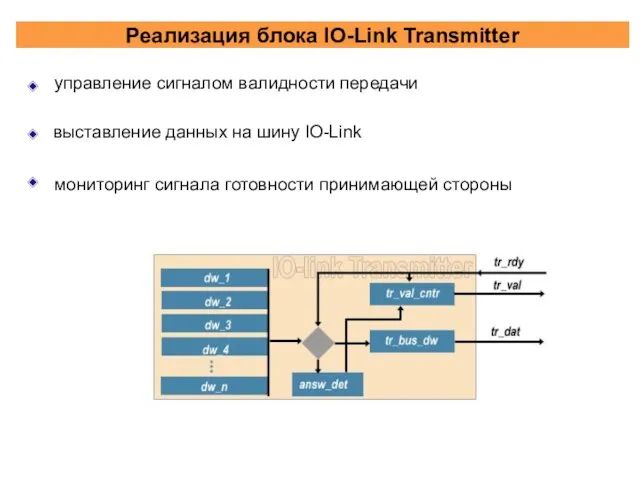

- 11. Реализация блока IO-Link Transmitter управление сигналом валидности передачи выставление данных на шину IO-Link мониторинг сигнала готовности

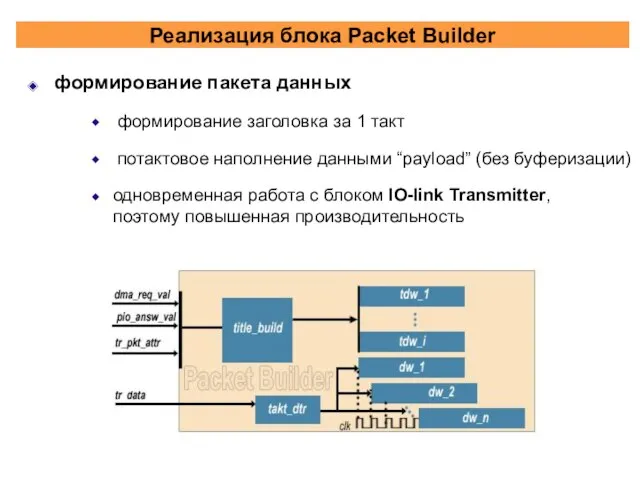

- 12. Реализация блока Packet Builder формирование пакета данных формирование заголовка за 1 такт потактовое наполнение данными “payload”

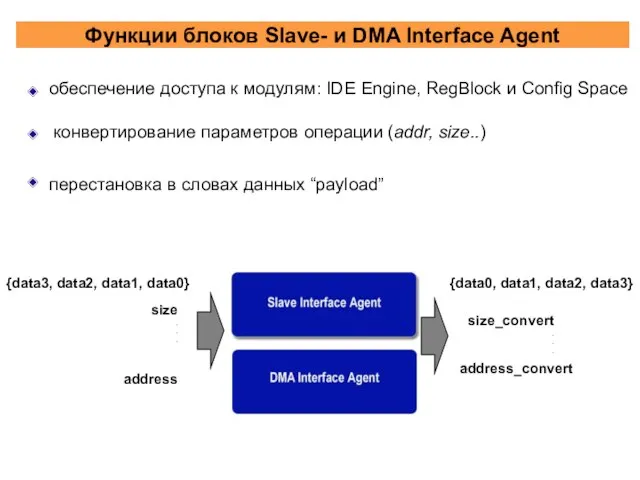

- 13. Функции блоков Slave- и DMA Interface Agent обеспечение доступа к модулям: IDE Engine, RegBlock и Config

- 14. Блок-схема IDE-контроллера

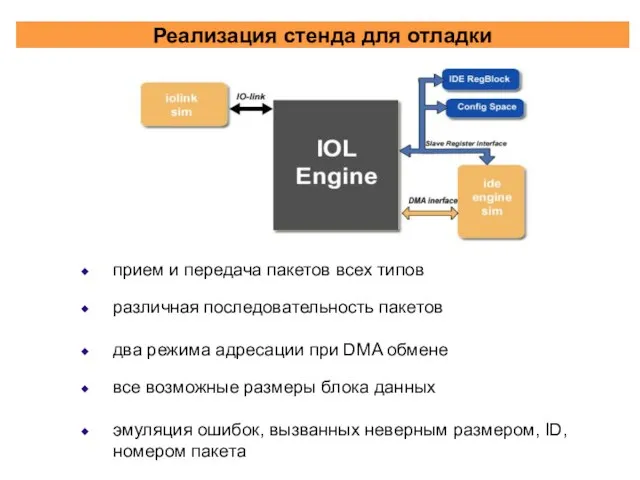

- 15. Реализация стенда для отладки прием и передача пакетов всех типов различная последовательность пакетов два режима адресации

- 17. Скачать презентацию

Встречают по одежке. Искусство самопрезентации. Бренд МногоМама

Встречают по одежке. Искусство самопрезентации. Бренд МногоМама Устройства вы́вода информации

Устройства вы́вода информации Психоаналитическая теория сновидений

Психоаналитическая теория сновидений Пустыни и полупустыни России

Пустыни и полупустыни России Лексическая сочетаемость

Лексическая сочетаемость Отец света и небесный кузнец Сварог

Отец света и небесный кузнец Сварог Марки акцизного сбора

Марки акцизного сбора Способ управления и назначение

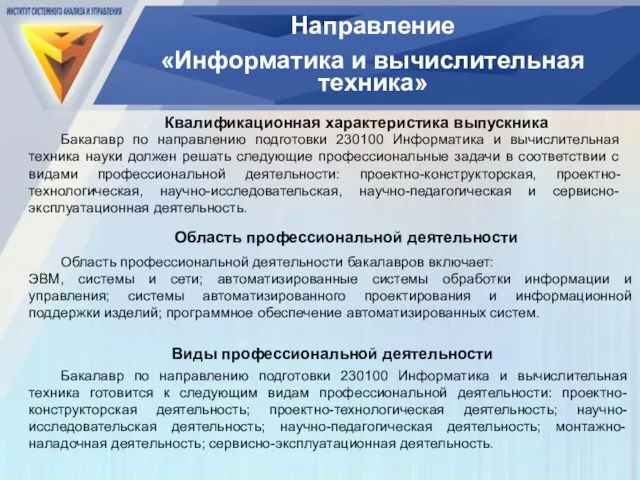

Способ управления и назначение Направление «Информатика и вычислительная техника»

Направление «Информатика и вычислительная техника» Способы получения и утраты гражданства Израиля

Способы получения и утраты гражданства Израиля Творчество В. М. Васнецова, М. А. Врубеля, М.В. Нестерова. История искусства. Часть 17

Творчество В. М. Васнецова, М. А. Врубеля, М.В. Нестерова. История искусства. Часть 17 Пленарное заседание ИСО ТК67 Сентябрь, 14-15Москва Балчуг Кемпински

Пленарное заседание ИСО ТК67 Сентябрь, 14-15Москва Балчуг Кемпински Федеративное устройство. Федеральные органы власти. 10 класс

Федеративное устройство. Федеральные органы власти. 10 класс Презентация на тему Характеристика и классификация услуг

Презентация на тему Характеристика и классификация услуг Равномерное и равноускоренное движение

Равномерное и равноускоренное движение Нарушения водно-электролитного обмена

Нарушения водно-электролитного обмена Свифт Приключения Гулливера

Свифт Приключения Гулливера Презентация на тему Составление портрета хитрого человека в художественном стиле.

Презентация на тему Составление портрета хитрого человека в художественном стиле. Комплексный маркетинг для бизнеса

Комплексный маркетинг для бизнеса Маркетинговое обоснование модели среднестатистического покупателя и ее влияния на качество обслуживания в аптечных организациях

Маркетинговое обоснование модели среднестатистического покупателя и ее влияния на качество обслуживания в аптечных организациях Guess the animal. Using the shadow

Guess the animal. Using the shadow Барокко. Краткая история

Барокко. Краткая история Особенности проектного финансирования в реальном секторе экономики

Особенности проектного финансирования в реальном секторе экономики Презентация на тему Склонение имен прилагательных мн ч

Презентация на тему Склонение имен прилагательных мн ч  Замена светильников в гарантийный период

Замена светильников в гарантийный период Презентация на тему Массаж

Презентация на тему Массаж  Роль краеведения в воспитании патриотизма

Роль краеведения в воспитании патриотизма Лабиринт знаний - презентация для начальной школы_

Лабиринт знаний - презентация для начальной школы_