Содержание

- 2. Тема Краткий обзор специфики выполнения системы команд Intel x86 Видимость результатов работы команды Модель упорядоченности (непротиворечивости)

- 3. Система команд x86/x64 Многие операции модификации памяти проводятся через регистры (за некоторыми исключениями), в несколько стадий

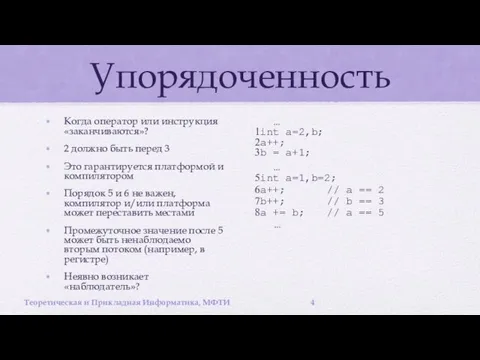

- 4. Упорядоченность Когда оператор или инструкция «заканчиваются»? 2 должно быть перед 3 Это гарантируется платформой и компилятором

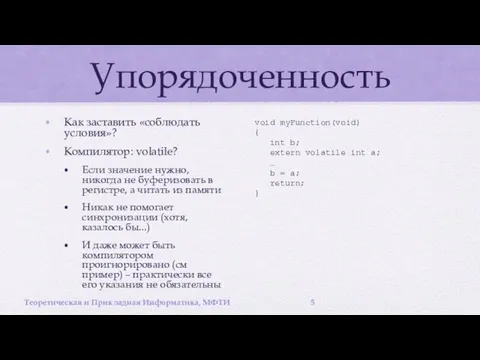

- 5. Упорядоченность Как заставить «соблюдать условия»? Компилятор: volatile? Если значение нужно, никогда не буферизовать в регистре, а

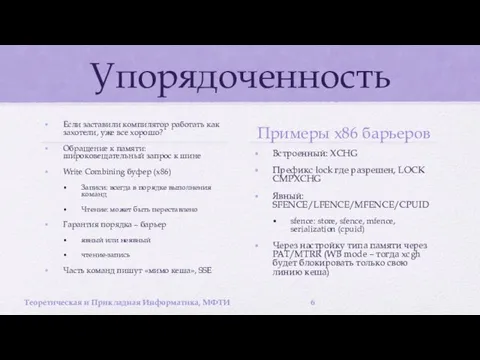

- 6. Упорядоченность Если заставили компилятор работать как захотели, уже все хорошо? Обращение к памяти: широковещательный запрос к

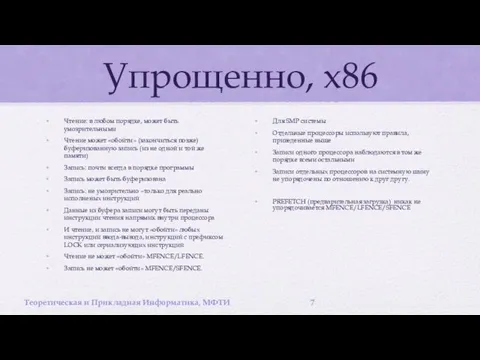

- 7. Упрощенно, x86 Чтение: в любом порядке, может быть умозрительными Чтение может «обойти» (закончиться позже) буферизованную запись

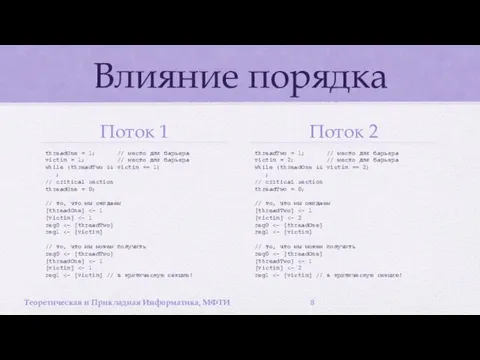

- 8. Влияние порядка Поток 1 Поток 2 Теоретическая и Прикладная Информатика, МФТИ threadTwo = 1; // место

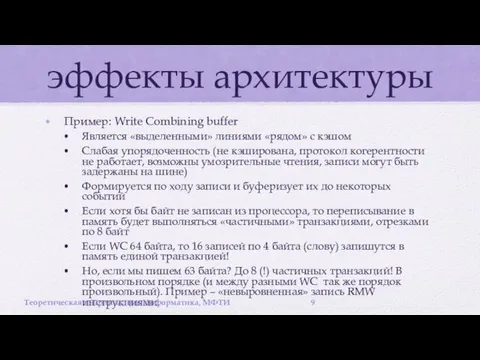

- 9. эффекты архитектуры Пример: Write Combining buffer Является «выделенными» линиями «рядом» с кэшом Слабая упорядоченность (не кэширована,

- 10. Атомарность Набор действий, которые могут комбинироваться только так, что для всех наблюдателей они представляют собой единую

- 11. Атомарность в х86 Аппаратно гарантируется атомарность ≥ 486: Чтение или запись байта Чтение или запись слова,

- 12. Атомарные примитивы Чтение и запись Mov Проверить-и-установить (test-and-set) Xchg (встроенный lock) Извлечь-и-добавить (fetch-and-add или read-modfy-write) Xadd

- 13. Скорость примитивов Если форсируют блокировку шины, то... Если форсируют упорядоченность операций (fence), то... Если используют WC

- 14. Выводы Есть много сложных понятий – упорядоченность операций, атомарность, видимость результатов для процессора и т.д. Большинство

- 16. Скачать презентацию

Фразеология – душа всякого национального языка

Фразеология – душа всякого национального языка Дидактические системы и модели обучения, факторы и цели

Дидактические системы и модели обучения, факторы и цели Египет. Уровень конституционного развития

Египет. Уровень конституционного развития Тундра

Тундра Приготовление блюда рататуй

Приготовление блюда рататуй Пророк Исайя

Пророк Исайя Атомные программы Ирана и КНДР

Атомные программы Ирана и КНДР Предложение по распространению рекламных материалов в сети магазинов «Азбука Вкуса

Предложение по распространению рекламных материалов в сети магазинов «Азбука Вкуса Табличное умножение и деление

Табличное умножение и деление Формальная логика

Формальная логика Правописание ЖИ и ШИ

Правописание ЖИ и ШИ 16631

16631 Вареники с картошкой

Вареники с картошкой Коррозия металлов

Коррозия металлов Название кейса. Шаблон

Название кейса. Шаблон Олимпийский чемпион

Олимпийский чемпион Муниципальное бюджетное дошкольное образовательное учреждение Детский сад № 23 «Чебурашка»

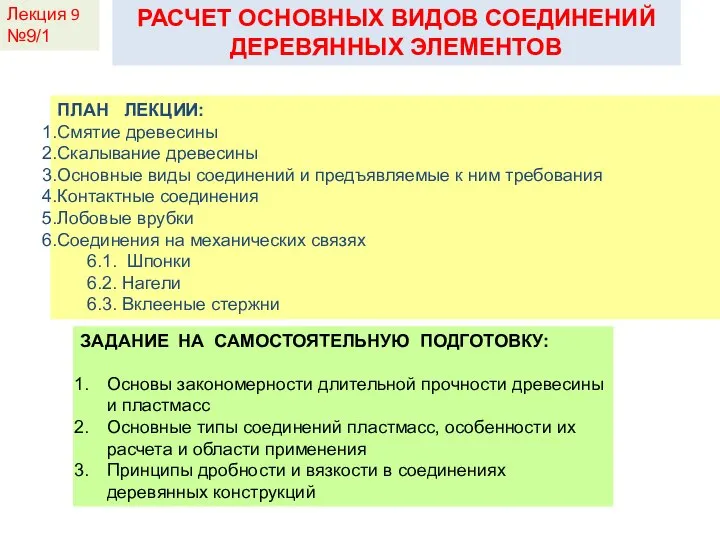

Муниципальное бюджетное дошкольное образовательное учреждение Детский сад № 23 «Чебурашка» Расчет основных видов соединений деревянных элементов. Лекция 9

Расчет основных видов соединений деревянных элементов. Лекция 9 Мясные консервы

Мясные консервы Управление знаниями: теория и практика построения системы управления знаниями

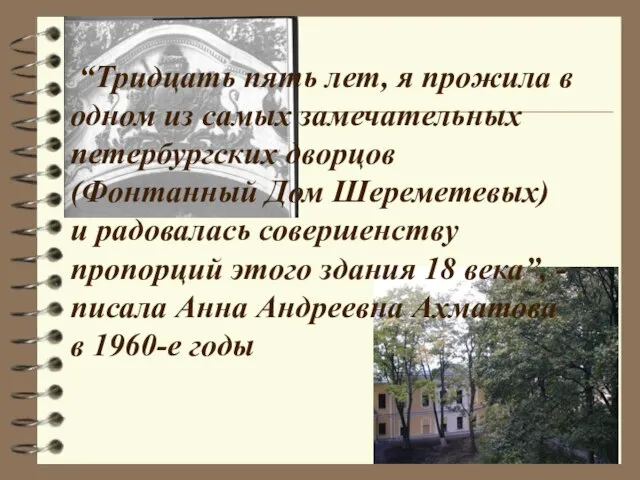

Управление знаниями: теория и практика построения системы управления знаниями “Тридцать пять лет, я прожила в одном из самых замечательных петербургских дворцов (Фонтанный Дом Шереметевых) и радовалась совер

“Тридцать пять лет, я прожила в одном из самых замечательных петербургских дворцов (Фонтанный Дом Шереметевых) и радовалась совер Загальні відомості про теорію систем і системний аналіз

Загальні відомості про теорію систем і системний аналіз Оценочные процедуры в РСОКО. Анализ опыта Чувашской Республики.

Оценочные процедуры в РСОКО. Анализ опыта Чувашской Республики. Дере́вня — сельский населённый пункт с несколькими десятками домов

Дере́вня — сельский населённый пункт с несколькими десятками домов Этапы расследования

Этапы расследования Кейс - метод

Кейс - метод Органические вещества. Белки

Органические вещества. Белки Сравнение Прайс Листов : Полюс vs Кайнар

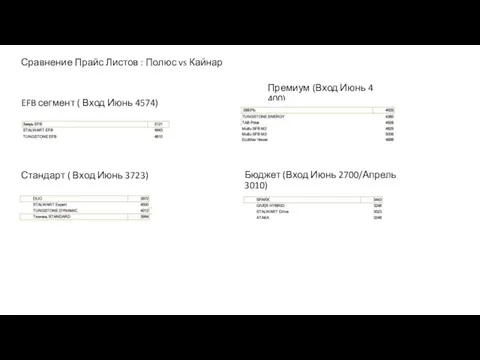

Сравнение Прайс Листов : Полюс vs Кайнар