Содержание

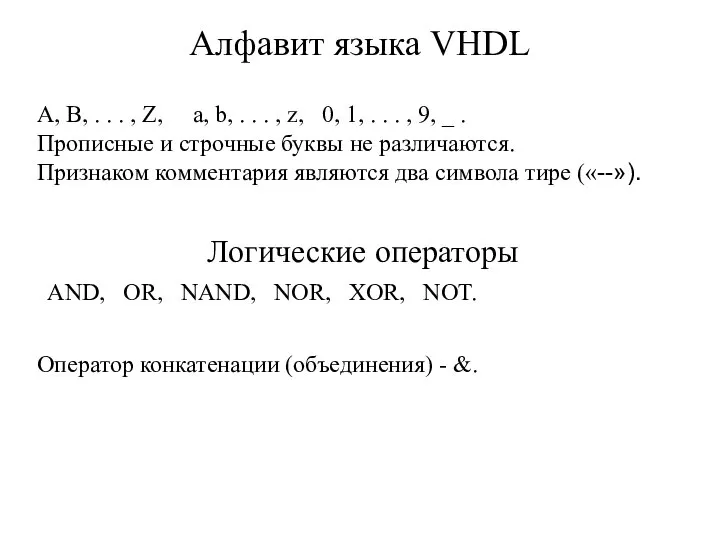

- 2. Алфавит языка VHDL A, B, . . . , Z, a, b, . . . ,

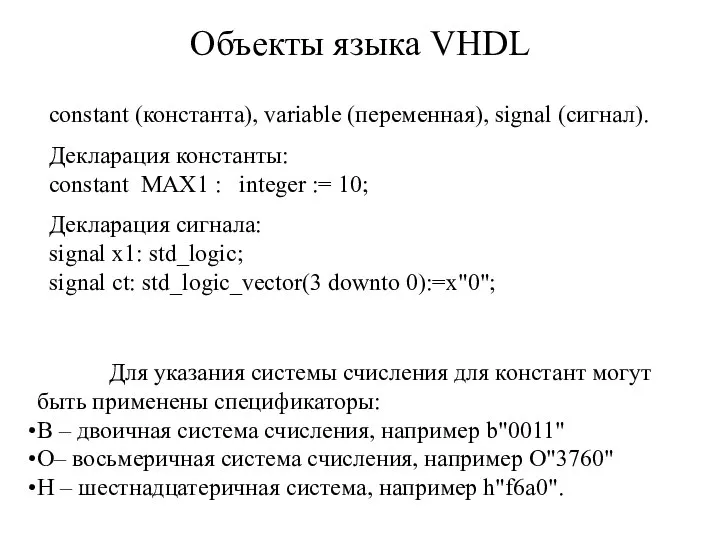

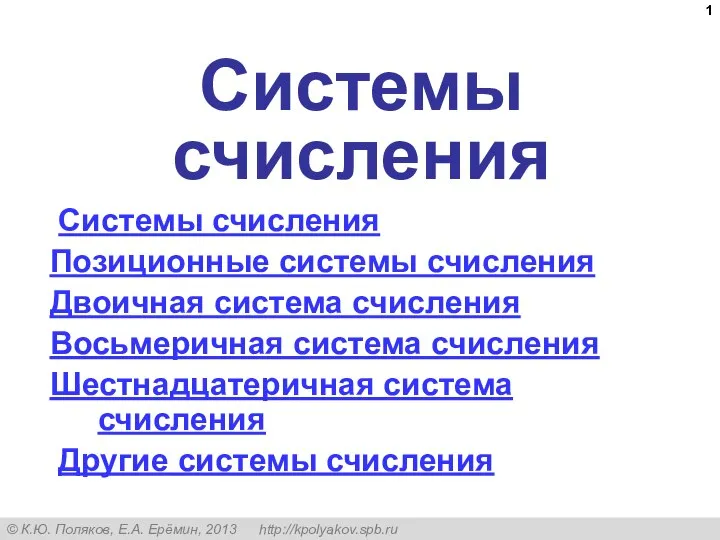

- 3. Объекты языка VHDL Для указания системы счисления для констант могут быть применены спецификаторы: B – двоичная

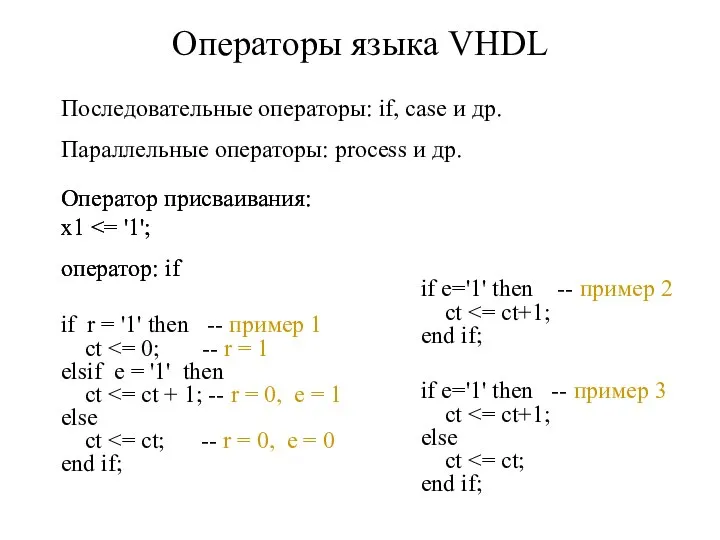

- 4. Операторы языка VHDL Oператор присваивания: x1 оператор: if if r = '1' then -- пример 1

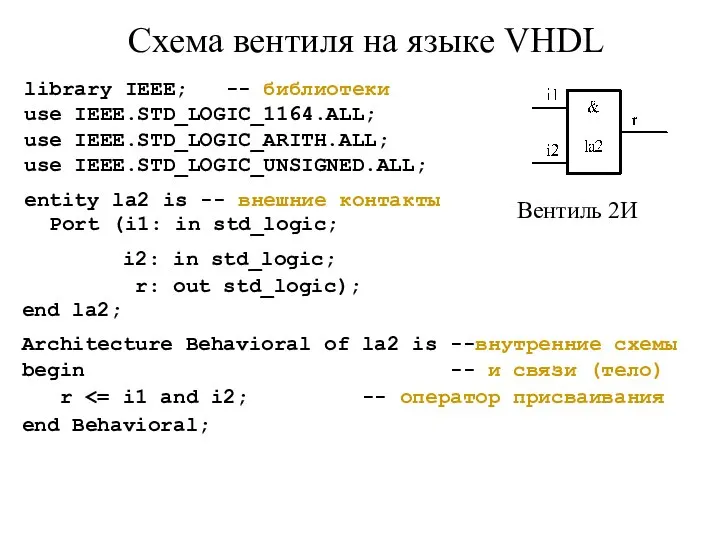

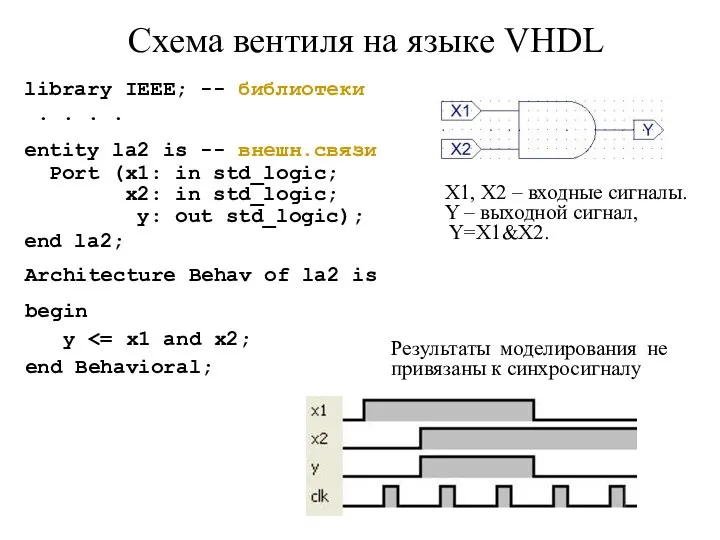

- 5. Схема вентиля на языке VHDL library IEEE; -- библиотеки use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity

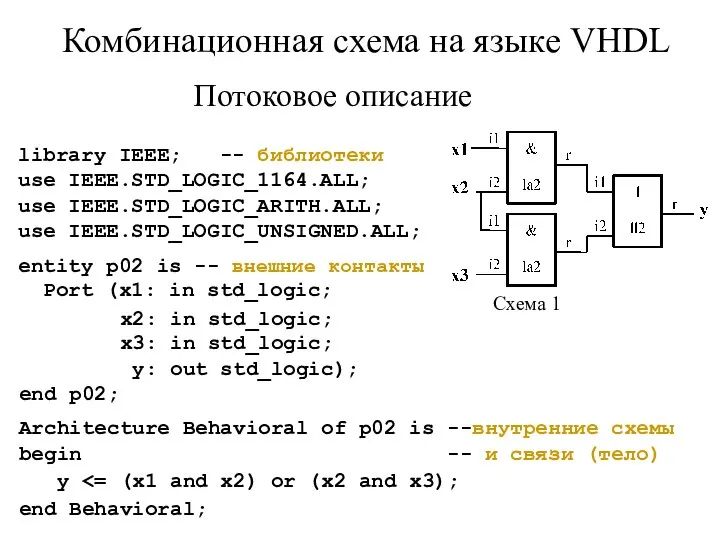

- 6. Комбинационная схема на языке VHDL library IEEE; -- библиотеки use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity

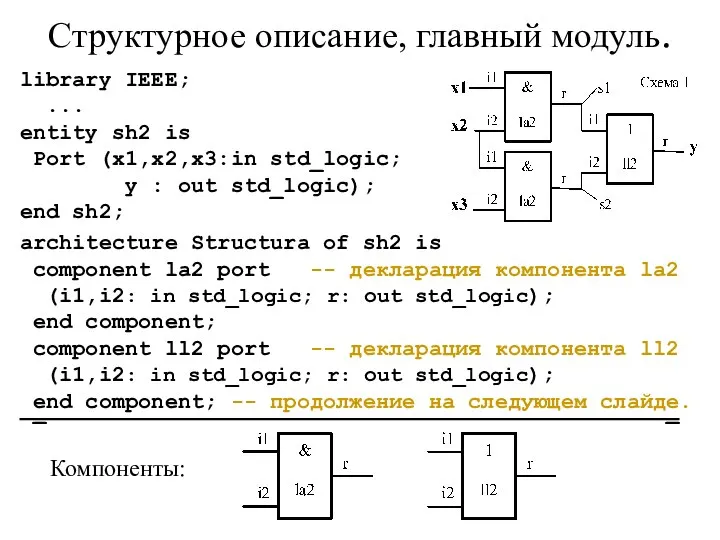

- 7. Структурное описание, главный модуль. architecture Structura of sh2 is component la2 port -- декларация компонента la2

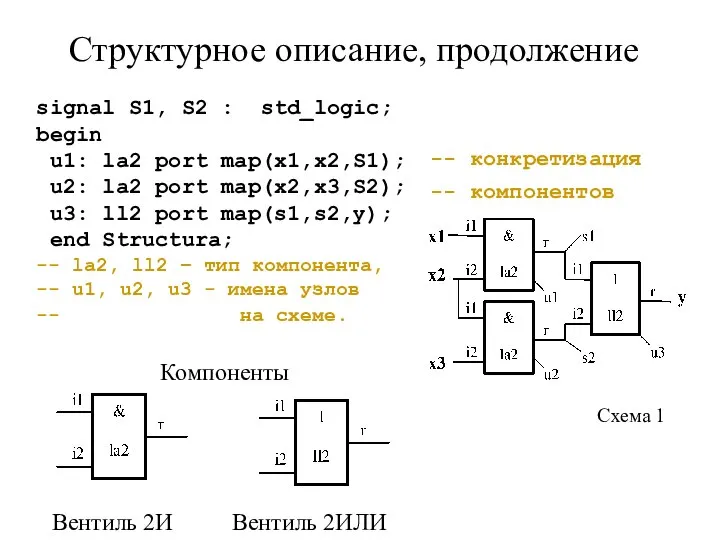

- 8. Структурное описание, продолжение signal S1, S2 : std_logic; begin u1: la2 port map(x1,x2,S1); u2: la2 port

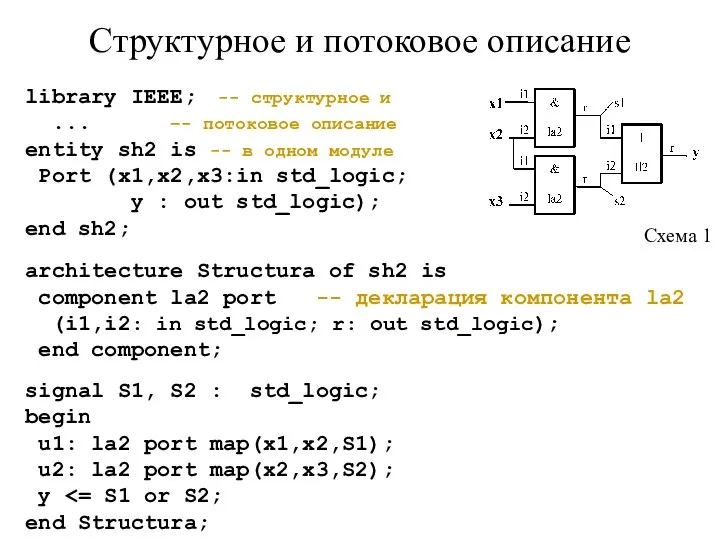

- 9. Структурное и потоковое описание architecture Structura of sh2 is component la2 port -- декларация компонента la2

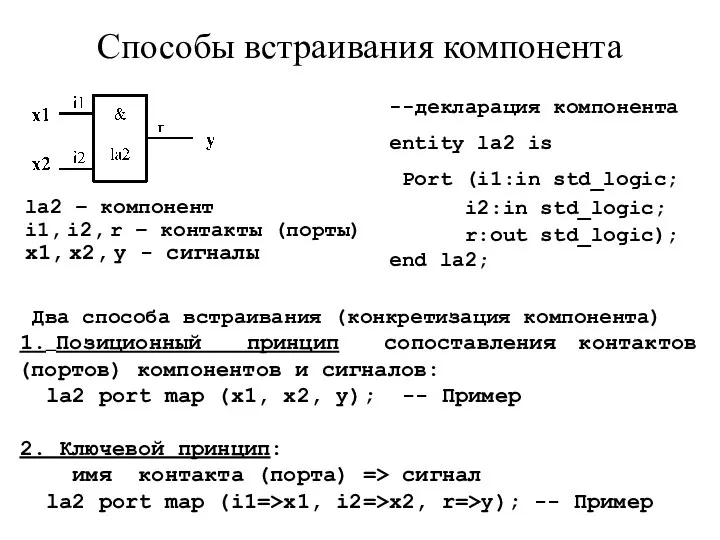

- 10. Способы встраивания компонента Два способа встраивания (конкретизация компонента) 1. Позиционный принцип сопоставления контактов (портов) компонентов и

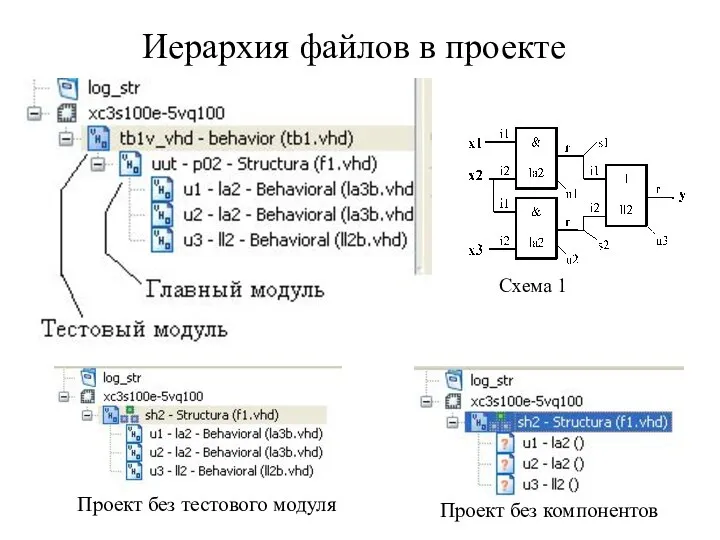

- 11. Иерархия файлов в проекте Проект без тестового модуля Проект без компонентов Схема 1

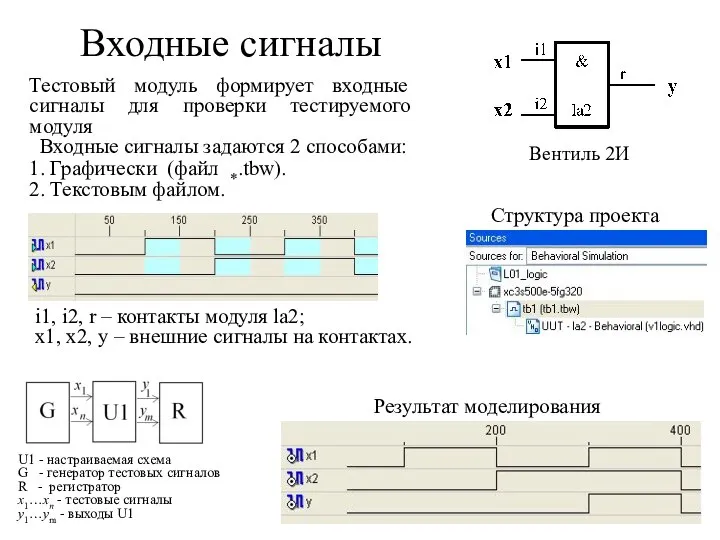

- 12. Входные сигналы Результат моделирования Структура проекта i1, i2, r – контакты модуля la2; x1, x2, y

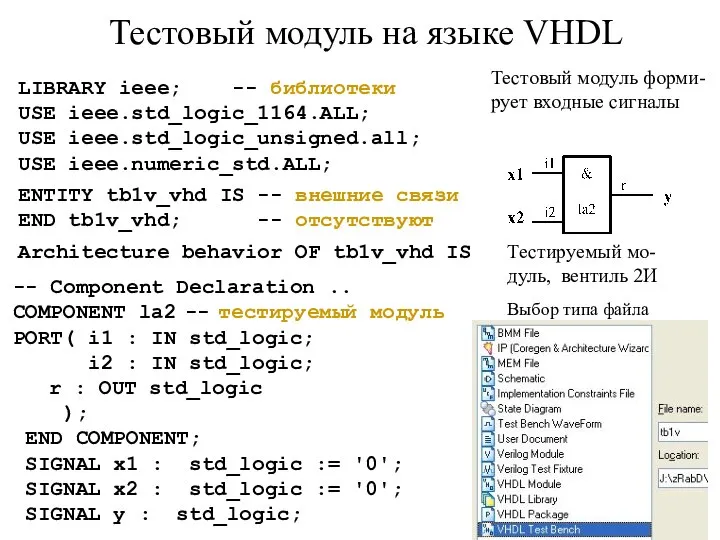

- 13. Тестовый модуль на языке VHDL LIBRARY ieee; -- библиотеки USE ieee.std_logic_1164.ALL; USE ieee.std_logic_unsigned.all; USE ieee.numeric_std.ALL; ENTITY

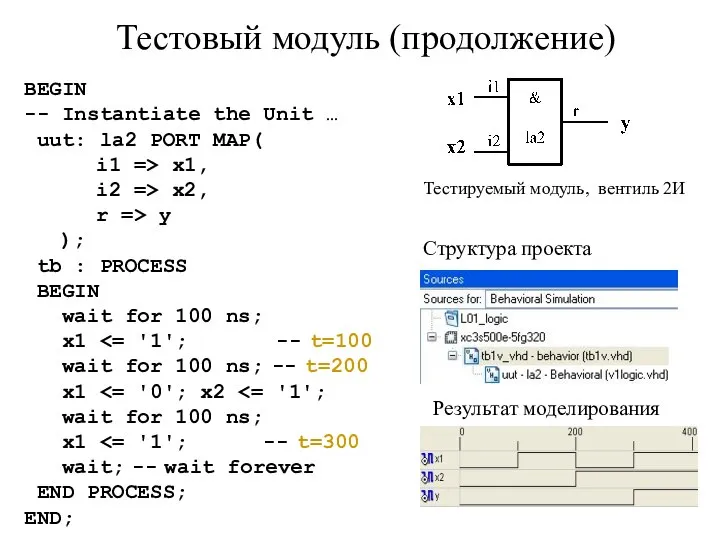

- 14. Тестовый модуль (продолжение) BEGIN -- Instantiate the Unit … uut: la2 PORT MAP( i1 => x1,

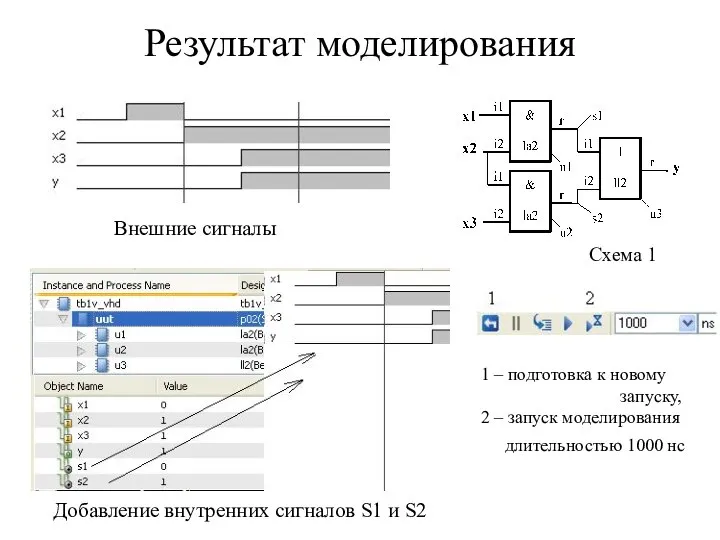

- 15. Результат моделирования Внешние сигналы Добавление внутренних сигналов S1 и S2 1 – подготовка к новому запуску,

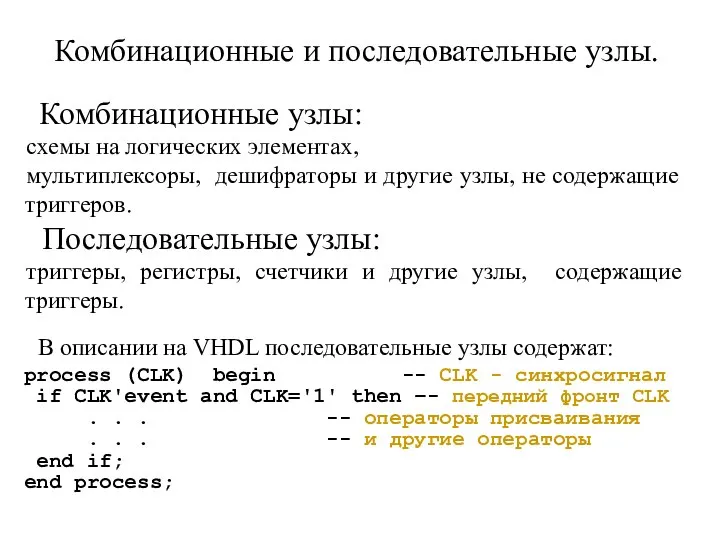

- 16. Комбинационные и последовательные узлы. Комбинационные узлы: схемы на логических элементах, мультиплексоры, дешифраторы и другие узлы, не

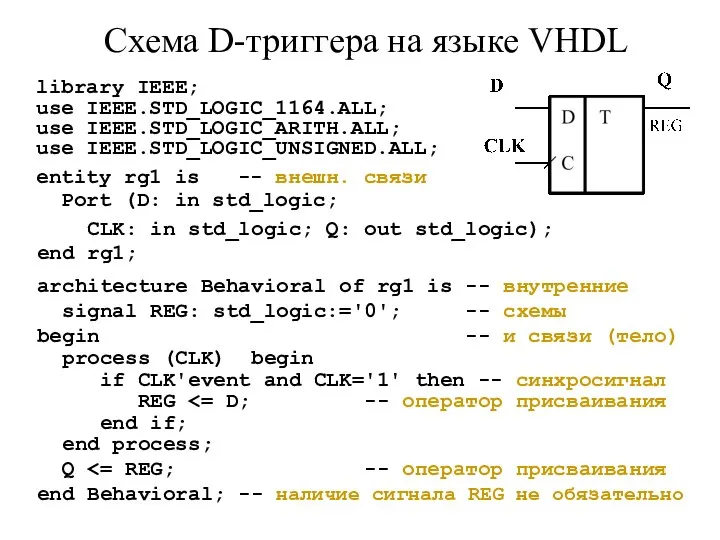

- 17. Схема D-триггера на языке VHDL library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity rg1 is

- 18. Результат работы q ? d в момент переключения clk из 0 в 1

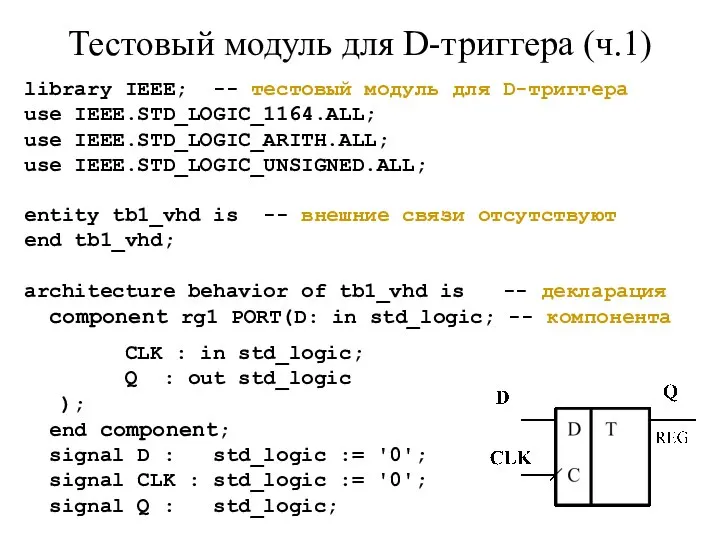

- 19. Тестовый модуль для D-триггера (ч.1) library IEEE; -- тестовый модуль для D-триггера use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL;

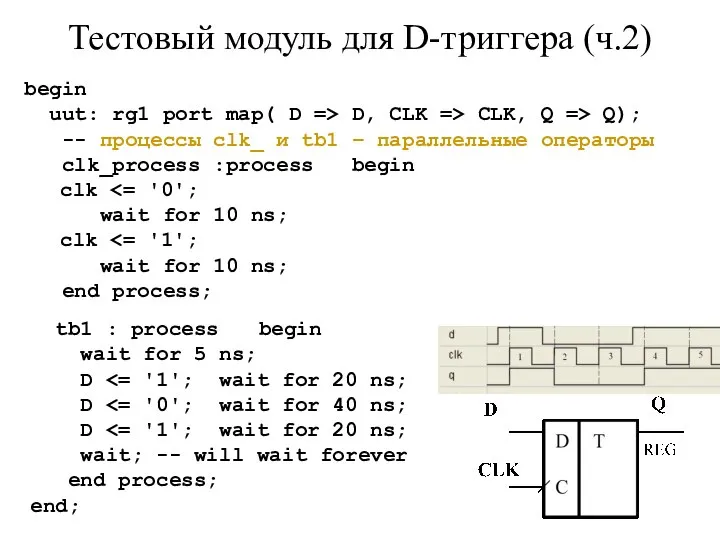

- 20. Тестовый модуль для D-триггера (ч.2) begin uut: rg1 port map( D => D, CLK => CLK,

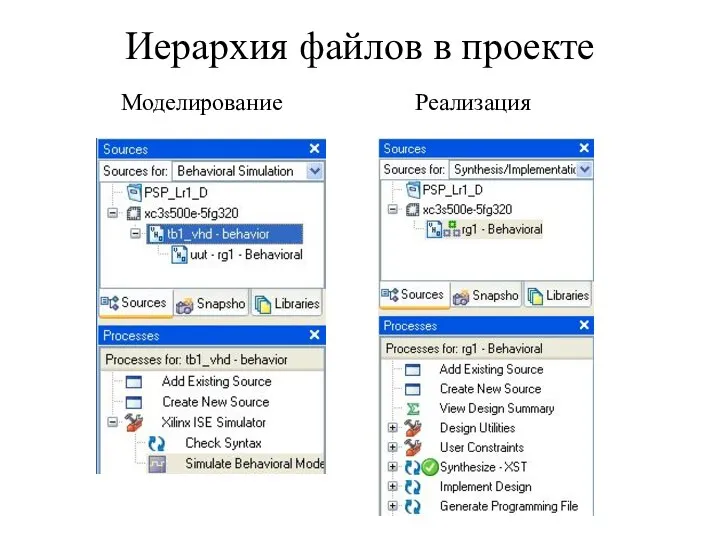

- 21. Иерархия файлов в проекте Моделирование Реализация

- 22. Схема вентиля на языке VHDL library IEEE; -- библиотеки . . . . entity la2 is

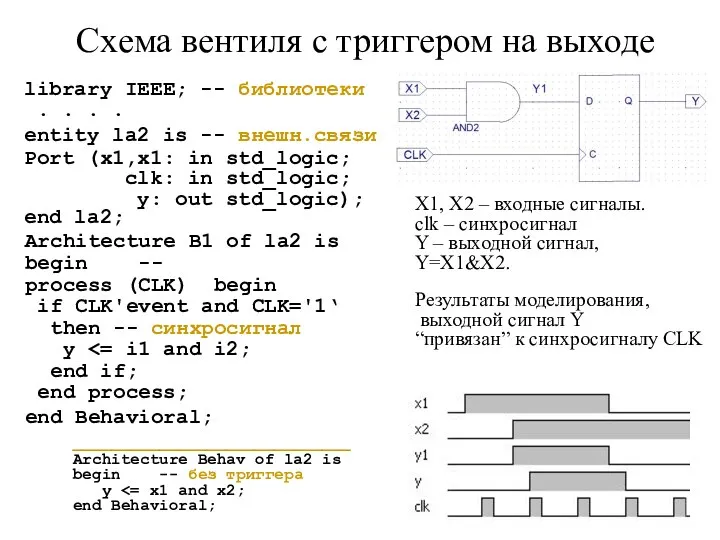

- 23. Схема вентиля c триггером на выходе library IEEE; -- библиотеки . . . . entity la2

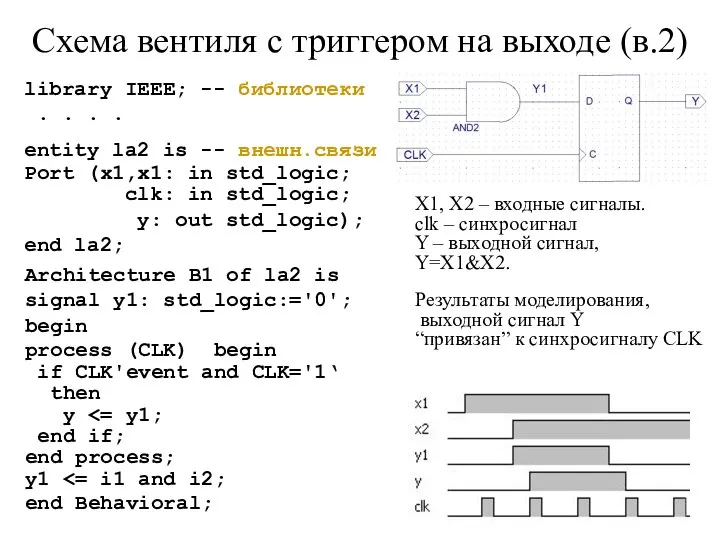

- 24. Схема вентиля c триггером на выходе (в.2) library IEEE; -- библиотеки . . . . entity

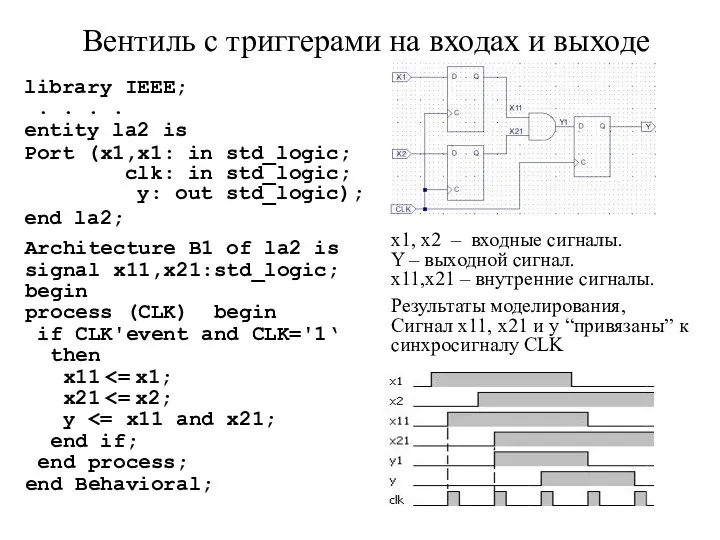

- 25. Вентиль c триггерами на входах и выходе library IEEE; . . . . entity la2 is

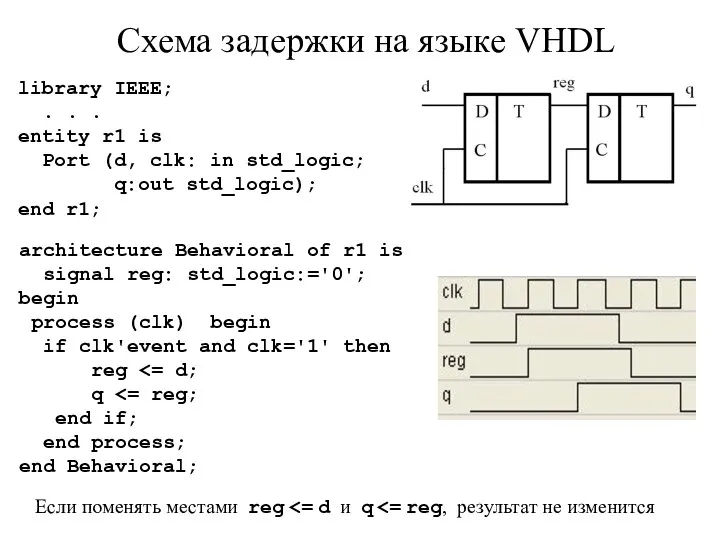

- 26. Схема задержки на языке VHDL library IEEE; . . . entity r1 is Port (d, clk:

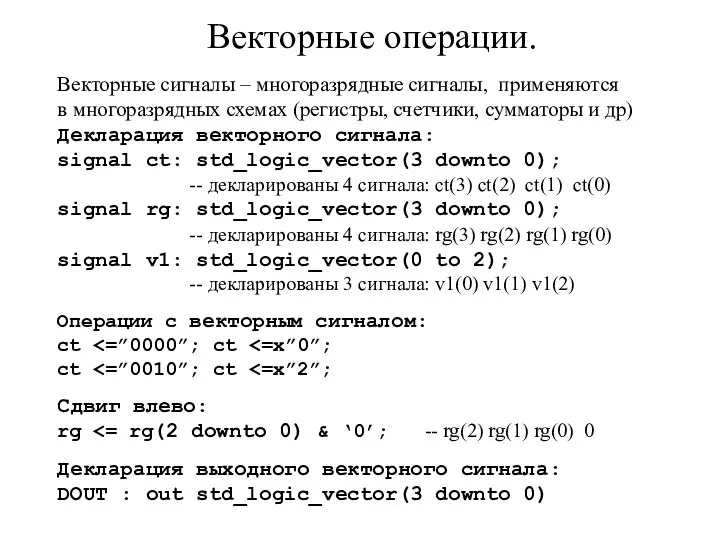

- 27. Векторные операции. Векторные сигналы – многоразрядные сигналы, применяются в многоразрядных схемах (регистры, счетчики, сумматоры и др)

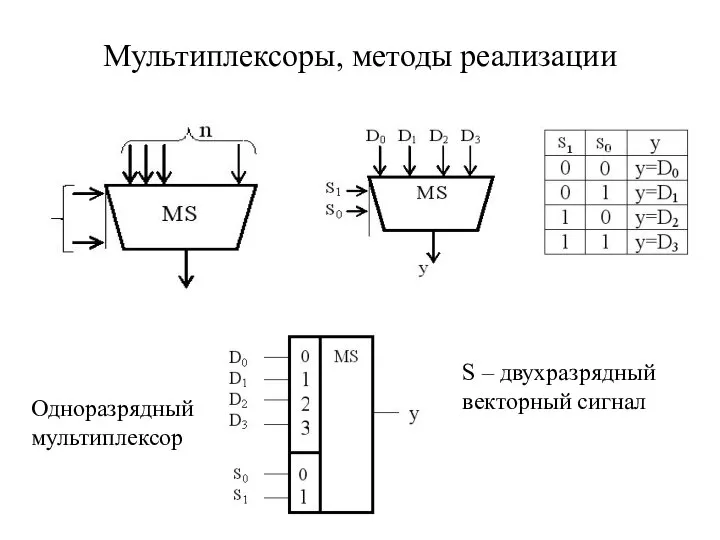

- 28. Мультиплексоры, методы реализации Одноразрядный мультиплексор S – двухразрядный векторный сигнал

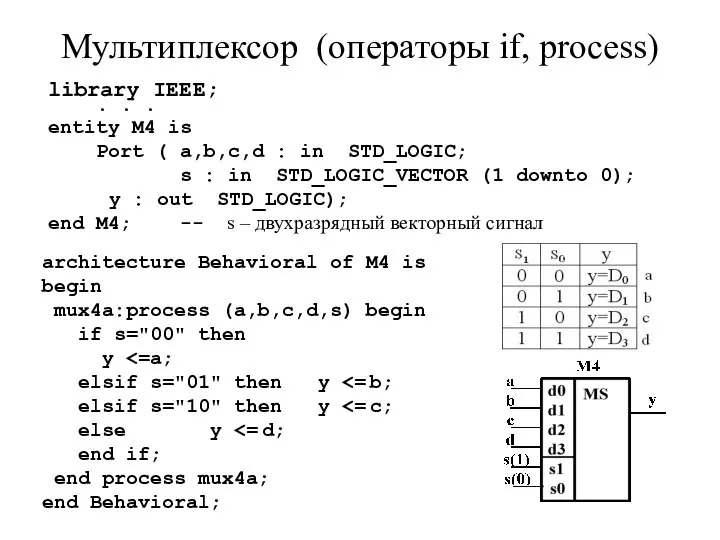

- 29. Мультиплексор (операторы if, process) library IEEE; . . . entity M4 is Port ( a,b,c,d :

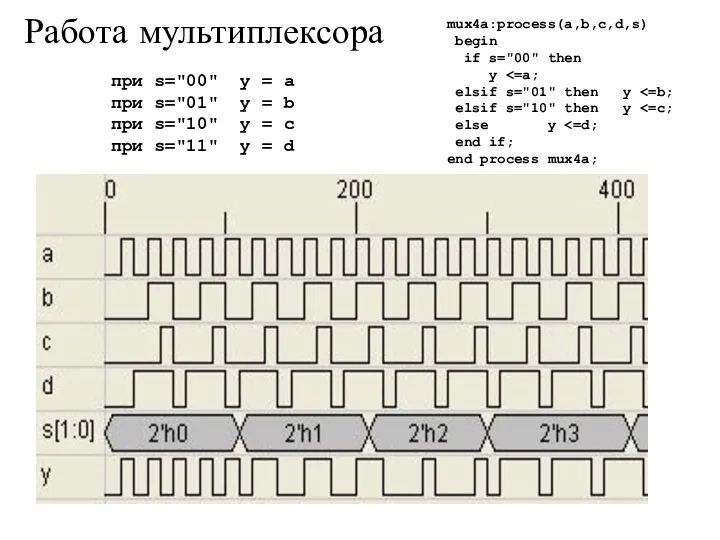

- 30. Работа мультиплексора mux4a:process(a,b,c,d,s) begin if s="00" then y elsif s="01" then y elsif s="10" then y

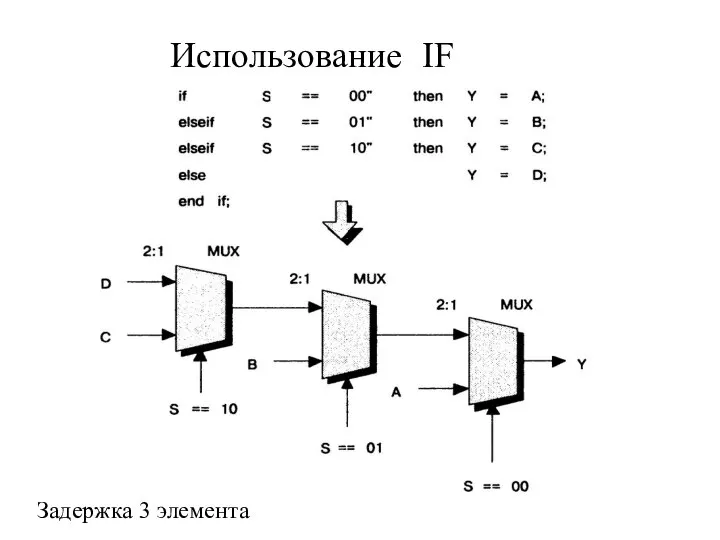

- 31. Использование IF Задержка 3 элемента

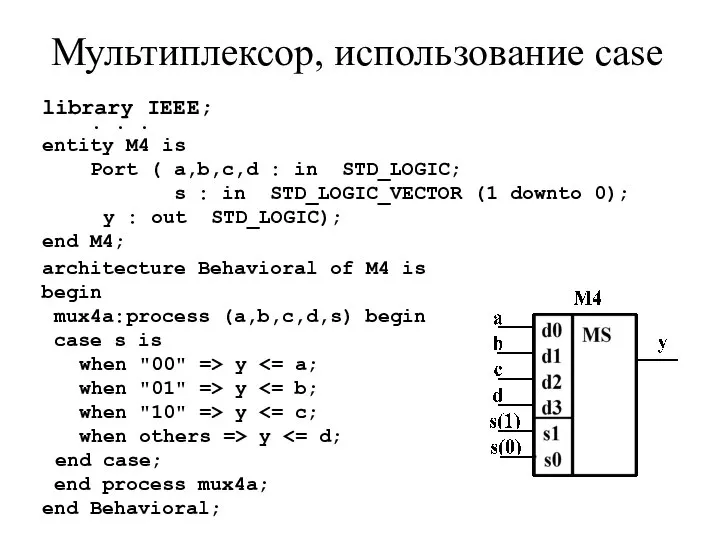

- 32. Мультиплексор, использование case library IEEE; . . . entity M4 is Port ( a,b,c,d : in

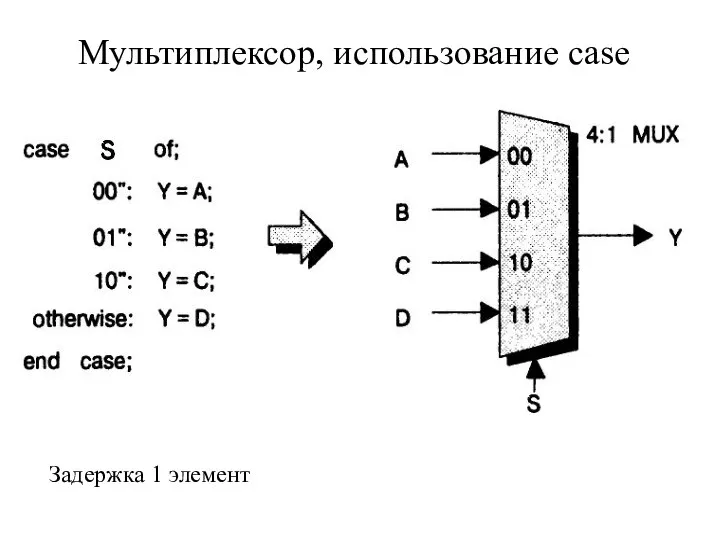

- 33. Мультиплексор, использование case Задержка 1 элемент

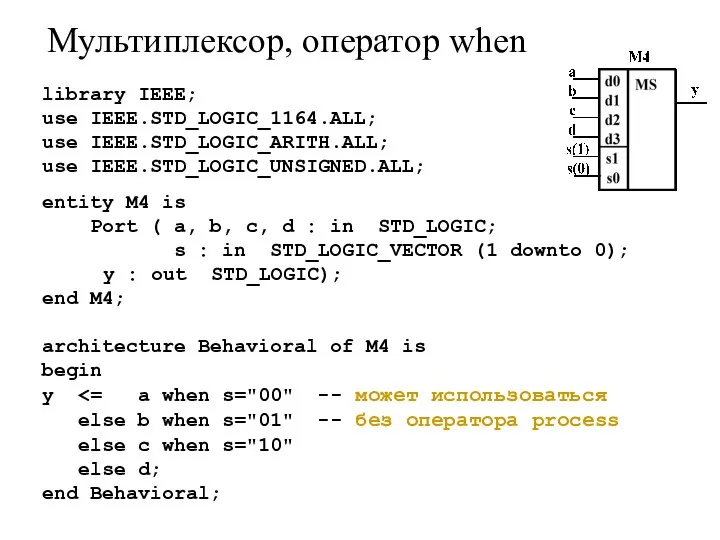

- 34. Мультиплексор, оператор when library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity M4 is Port (

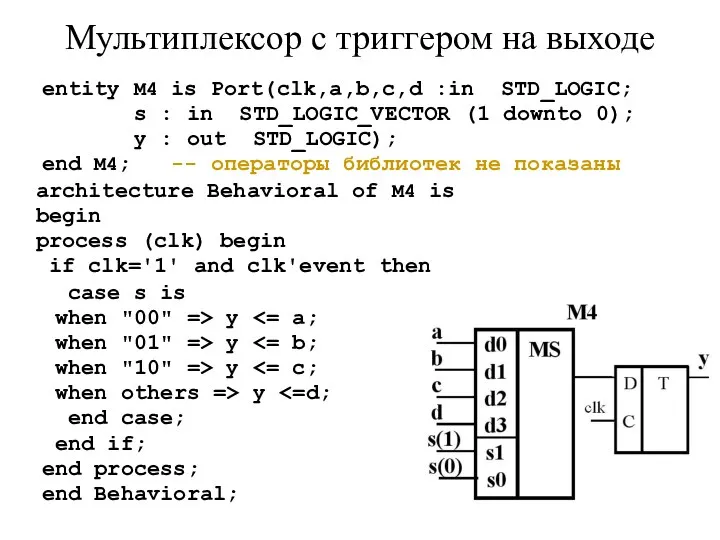

- 35. Мультиплексор с триггером на выходе entity M4 is Port(clk,a,b,c,d :in STD_LOGIC; s : in STD_LOGIC_VECTOR (1

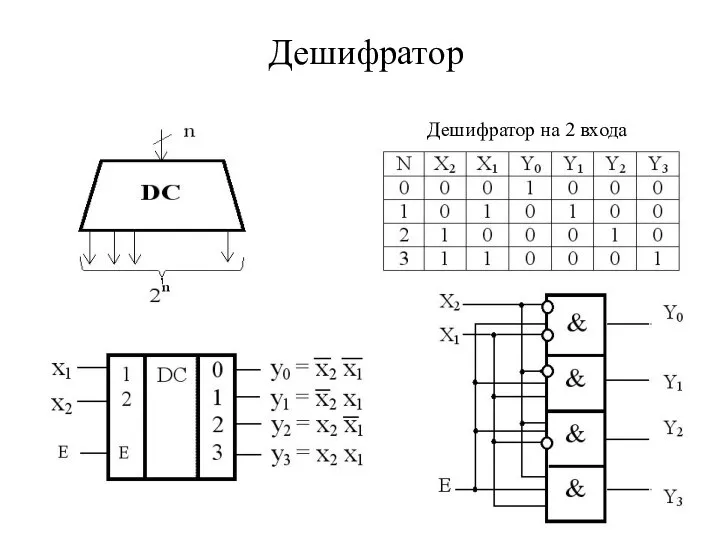

- 36. Дешифратор Дешифратор на 2 входа

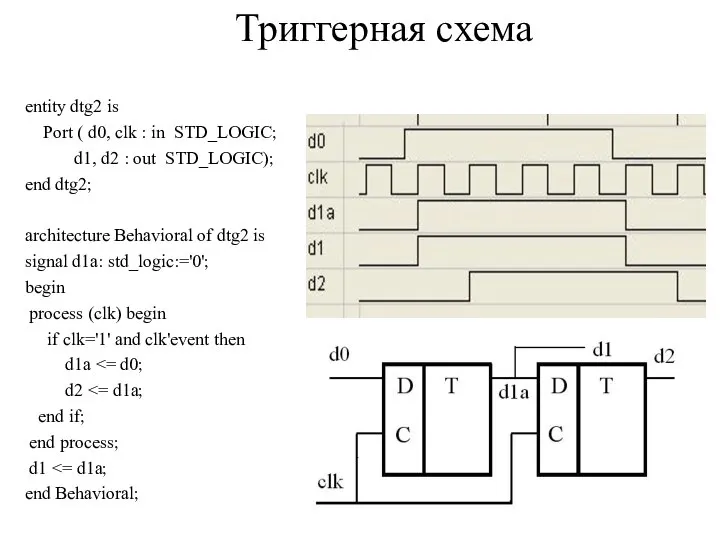

- 37. Триггерная схема entity dtg2 is Port ( d0, clk : in STD_LOGIC; d1, d2 : out

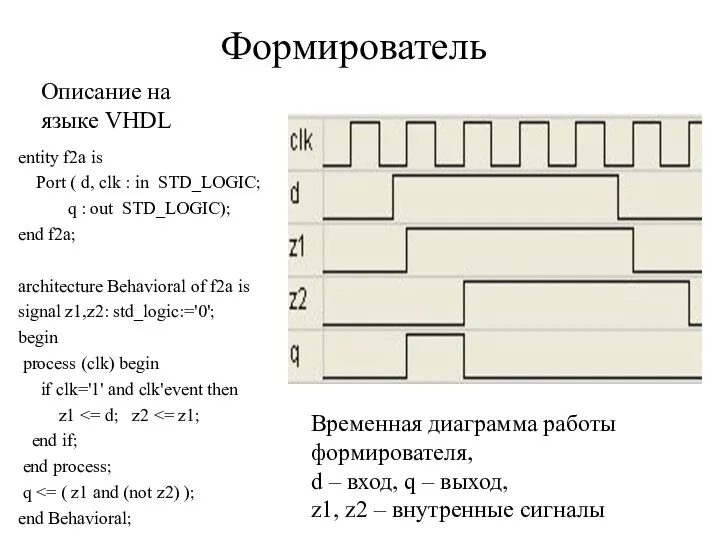

- 38. Формирователь entity f2a is Port ( d, clk : in STD_LOGIC; q : out STD_LOGIC); end

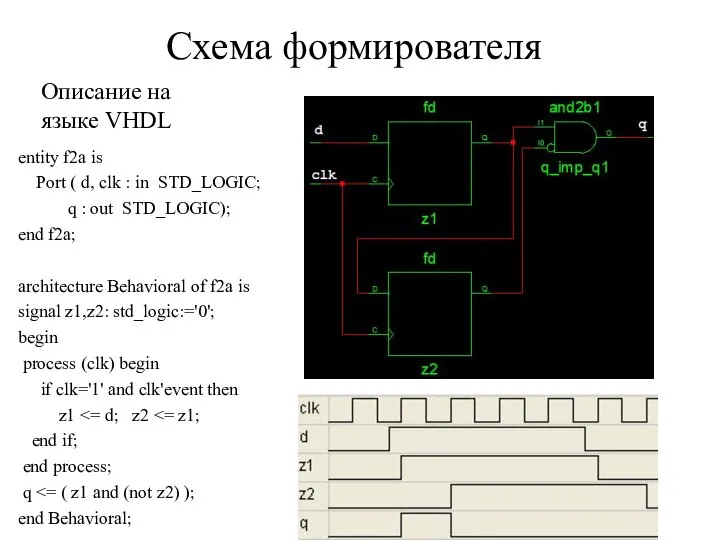

- 39. Схема формирователя entity f2a is Port ( d, clk : in STD_LOGIC; q : out STD_LOGIC);

- 41. Скачать презентацию

Понятие как форма мышления

Понятие как форма мышления Алгоритм. Свойства алгоритма

Алгоритм. Свойства алгоритма Специальность Библиотековедение

Специальность Библиотековедение Понятие цикла

Понятие цикла Форум абитуриентов ДонНУЭТ-2021 г

Форум абитуриентов ДонНУЭТ-2021 г Разработка отдельного программного модуля в информационной системе для предприятия ООО МИРС

Разработка отдельного программного модуля в информационной системе для предприятия ООО МИРС Abordări probabiliste Machin Learn

Abordări probabiliste Machin Learn Защита информации. Безопасность информации. Математический аппарат

Защита информации. Безопасность информации. Математический аппарат Библиографическое описание документа

Библиографическое описание документа Личный блог, блог компании, блог от третьего лица

Личный блог, блог компании, блог от третьего лица Системы счисления

Системы счисления Работа с документами

Работа с документами HTML. Разработка Web-сайта

HTML. Разработка Web-сайта Четвертая власть

Четвертая власть Файлы и файловые структуры

Файлы и файловые структуры Презентация _Как устроен персональный компьютер_ (7 класс)

Презентация _Как устроен персональный компьютер_ (7 класс) Практика использования специального оборудования в обучении детей с тяжелыми двигательными нарушениями

Практика использования специального оборудования в обучении детей с тяжелыми двигательными нарушениями Система управления базами данных (СУБД)

Система управления базами данных (СУБД) SiTAiRIS_LabWork1_UML_Diagramm_of_classes

SiTAiRIS_LabWork1_UML_Diagramm_of_classes Этапы создания программного обеспечения

Этапы создания программного обеспечения Автоматы с магазинной памятью

Автоматы с магазинной памятью Вычислительная сложность. Базовые структуры данных и их использование в С++

Вычислительная сложность. Базовые структуры данных и их использование в С++ Фотосушка. О проекте

Фотосушка. О проекте Микроядро Mach. ОС на его основе

Микроядро Mach. ОС на его основе ВКР: Использование новых информационных технологий в информационно документационном обеспечении управления

ВКР: Использование новых информационных технологий в информационно документационном обеспечении управления Расширенное руководство по использованию Shodan shodan-manual.com

Расширенное руководство по использованию Shodan shodan-manual.com IP-адресация

IP-адресация Реляционная модель данных

Реляционная модель данных