Содержание

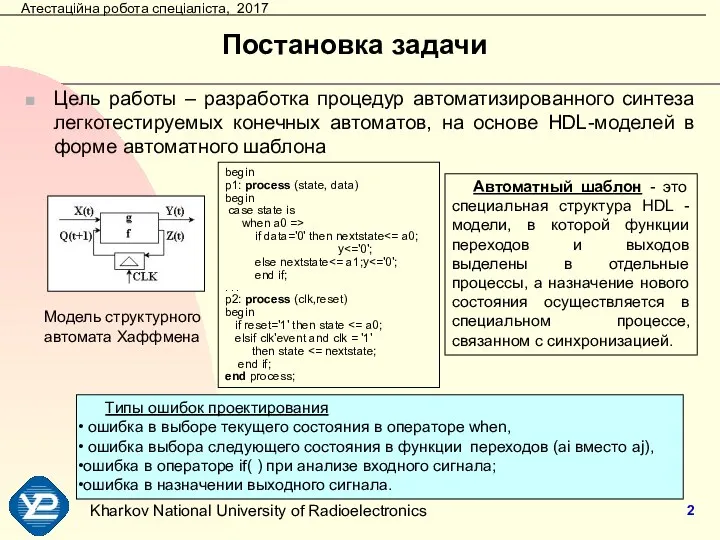

- 2. Постановка задачи Цель работы – разработка процедур автоматизированного синтеза легкотестируемых конечных автоматов, на основе HDL-моделей в

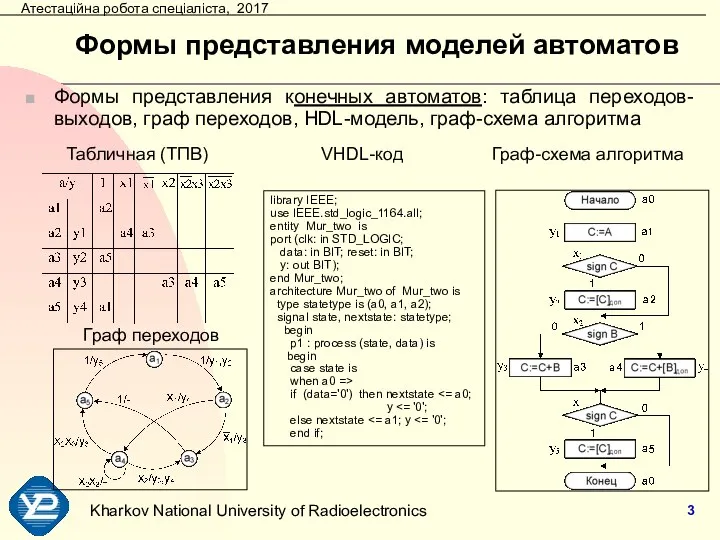

- 3. Формы представления моделей автоматов Формы представления конечных автоматов: таблица переходов-выходов, граф переходов, HDL-модель, граф-схема алгоритма library

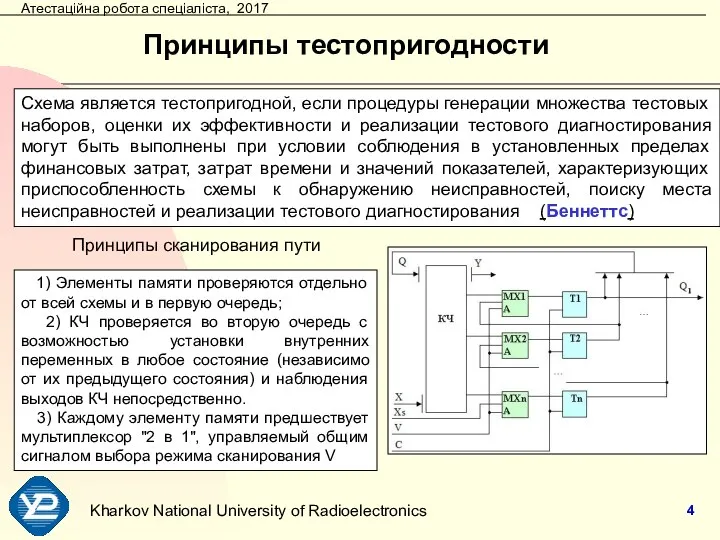

- 4. Принципы тестопригодности Схема является тестопригодной, если процедуры генерации множества тестовых наборов, оценки их эффективности и реализации

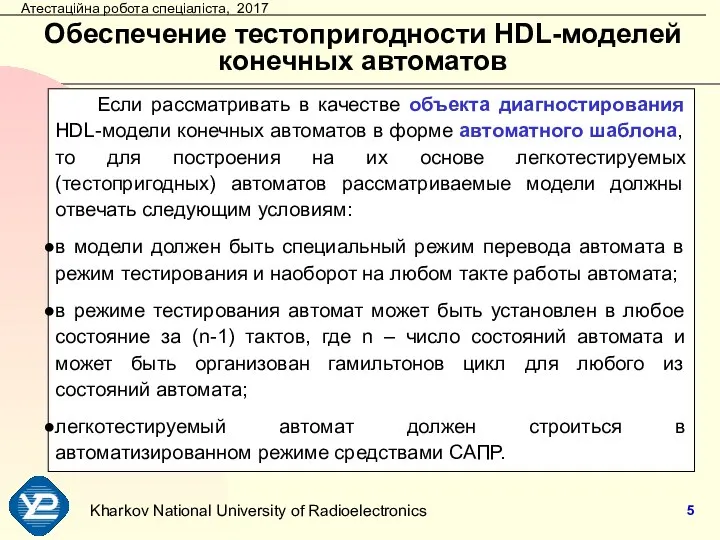

- 5. Обеспечение тестопригодности HDL-моделей конечных автоматов Если рассматривать в качестве объекта диагностирования HDL-модели конечных автоматов в форме

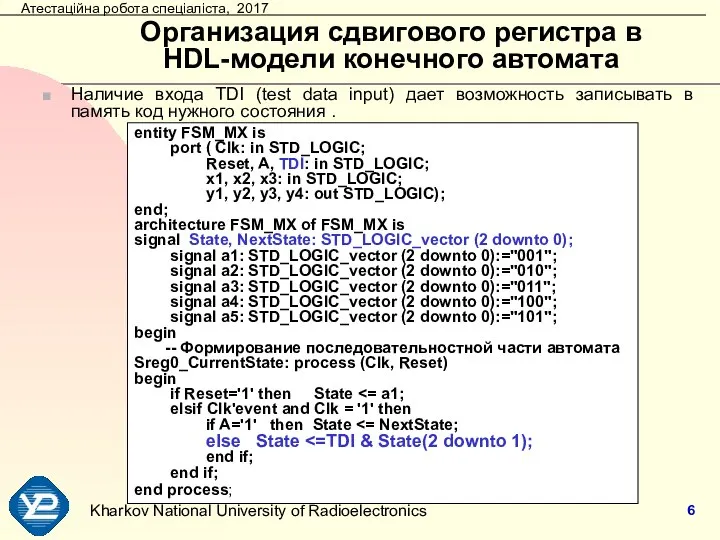

- 6. Организация сдвигового регистра в HDL-модели конечного автомата Наличие входа TDI (test data input) дает возможность записывать

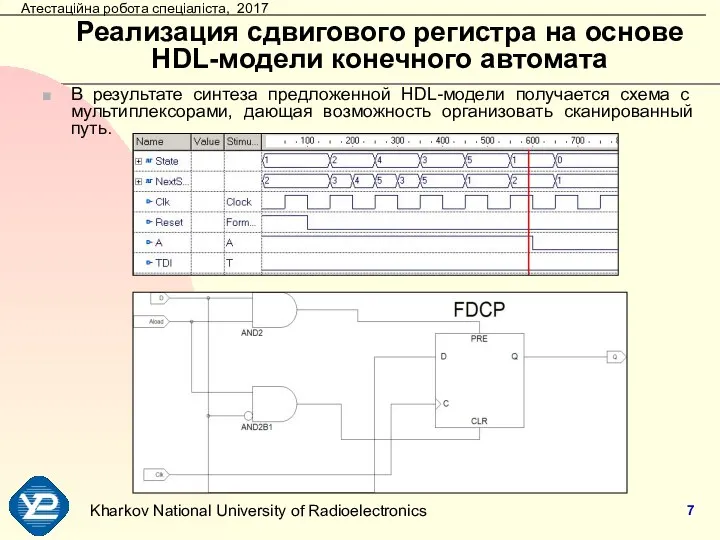

- 7. Реализация сдвигового регистра на основе HDL-модели конечного автомата В результате синтеза предложенной HDL-модели получается схема с

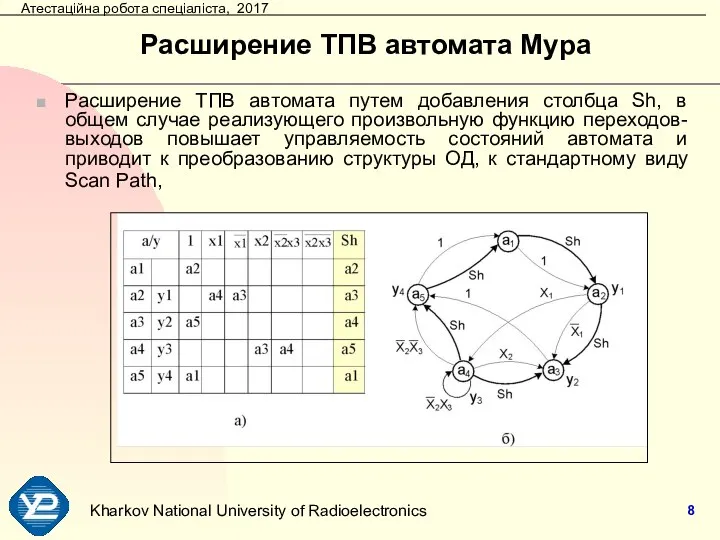

- 8. Расширение ТПВ автомата Мура Расширение TПB автомата путем добавления столбца Sh, в общем случае реализующего произвольную

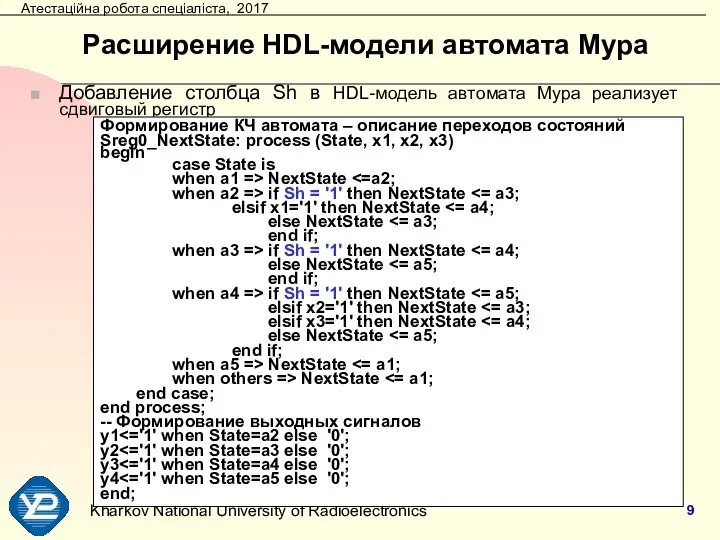

- 9. Расширение HDL-модели автомата Мура Добавление столбца Sh в HDL-модель автомата Мура реализует сдвиговый регистр Формирование КЧ

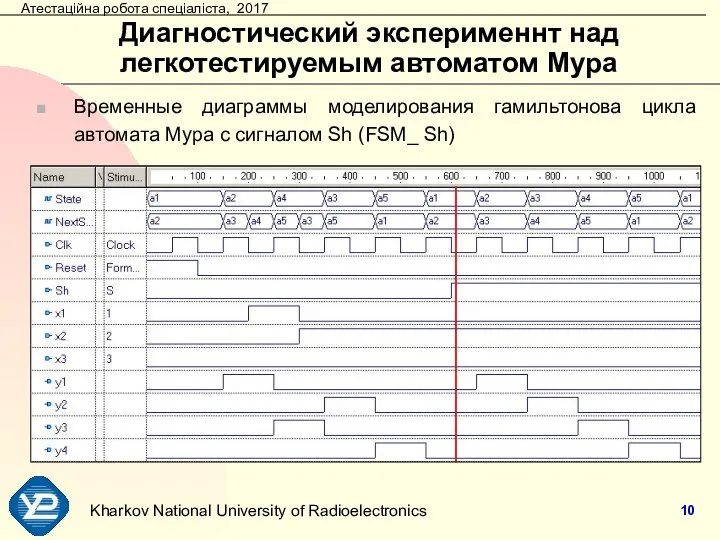

- 10. Диагностический эксперименнт над легкотестируемым автоматом Мура Временные диаграммы моделирования гамильтонова цикла автомата Мура с сигналом Sh

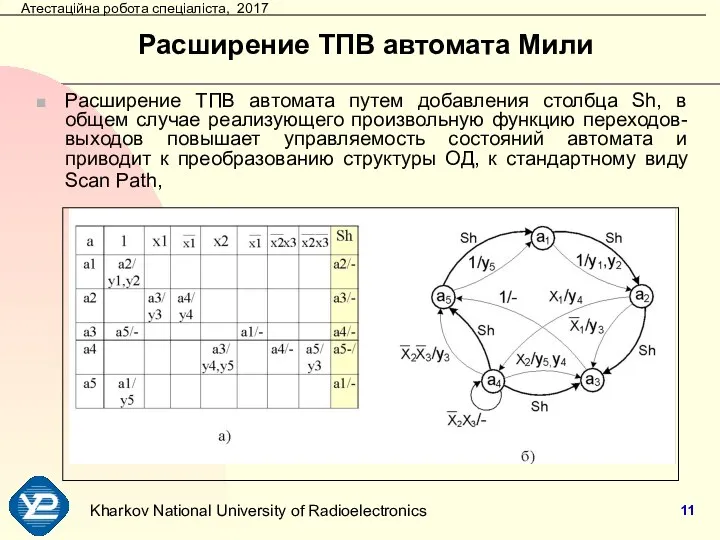

- 11. Расширение ТПВ автомата Мили Расширение TПB автомата путем добавления столбца Sh, в общем случае реализующего произвольную

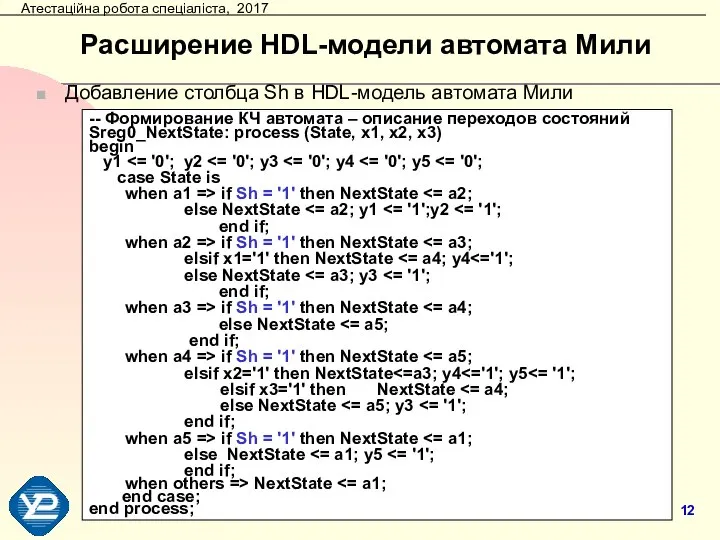

- 12. Расширение HDL-модели автомата Мили Добавление столбца Sh в HDL-модель автомата Мили -- Формирование КЧ автомата –

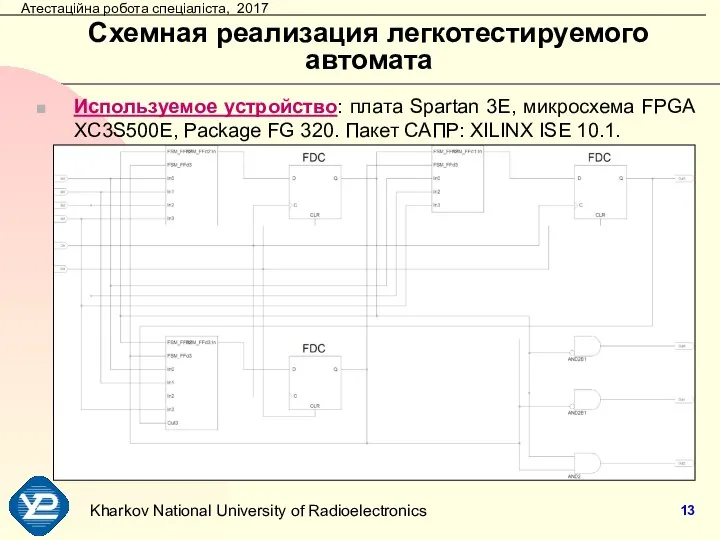

- 13. Схемная реализация легкотестируемого автомата Используемое устройство: плата Spartan 3E, микросхема FPGA XC3S500E, Package FG 320. Пакет

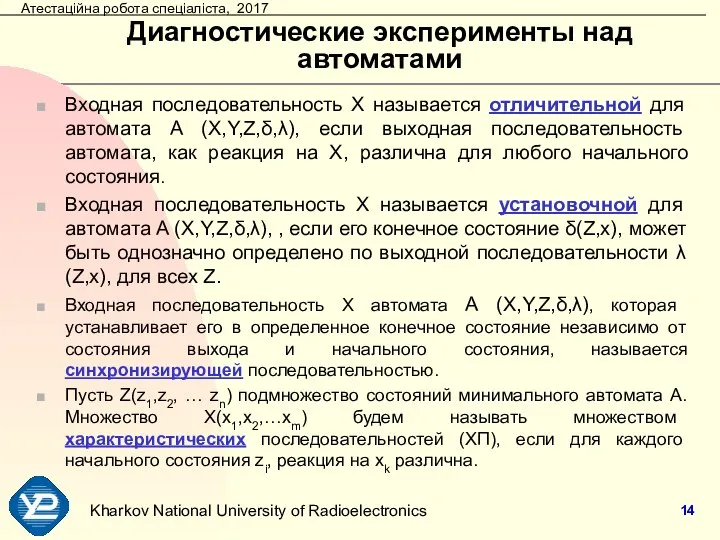

- 14. Диагностические эксперименты над автоматами Входная последовательность X называется отличительной для автомата A (X,Y,Z,δ,λ), если выходная последовательность

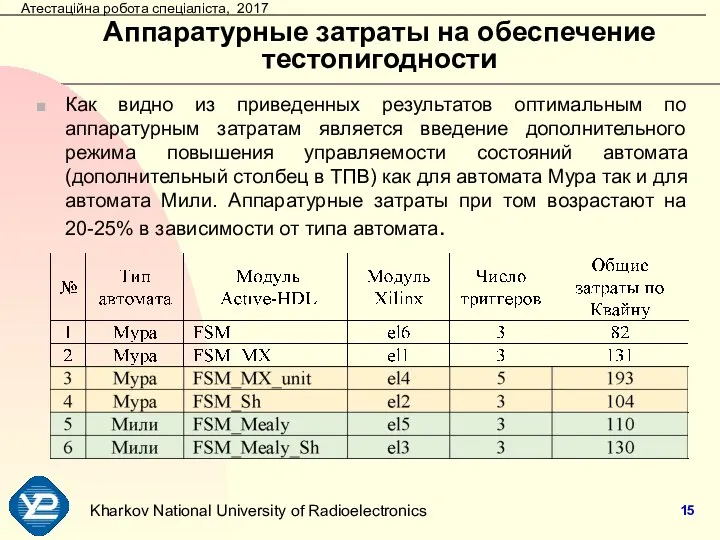

- 15. Аппаратурные затраты на обеспечение тестопигодности Как видно из приведенных результатов оптимальным по аппаратурным затратам является введение

- 17. Скачать презентацию

Проект Волшебная осень

Проект Волшебная осень Изготовление новогодней открытки 3D

Изготовление новогодней открытки 3D Отчет о проделанной работе. Лидер группы ГБОУ школы 1393

Отчет о проделанной работе. Лидер группы ГБОУ школы 1393 Играем со звуками Р и Л

Играем со звуками Р и Л Информационные технологи в образовании

Информационные технологи в образовании Произносительные трудности у детей с трудностями в обучении, обусловленные задержкой психологического развития

Произносительные трудности у детей с трудностями в обучении, обусловленные задержкой психологического развития Аттестационная работа. Проект по мотивам сказок Л. Кэрролла об Алисе

Аттестационная работа. Проект по мотивам сказок Л. Кэрролла об Алисе Ветер. Виды ветра

Ветер. Виды ветра Владимирский социально-реабилитационный центр для несовершеннолетних

Владимирский социально-реабилитационный центр для несовершеннолетних Я - за ученическое самоуправление

Я - за ученическое самоуправление Учебная практика (шаблон)

Учебная практика (шаблон) Слова для мамы

Слова для мамы Ответы к заданиям технологического путешествия

Ответы к заданиям технологического путешествия Домашние животные. Словарь

Домашние животные. Словарь Что такое квантум АЭРО. Мастер-класс

Что такое квантум АЭРО. Мастер-класс Маршрутные листы

Маршрутные листы Профориентация старшеклассников

Профориентация старшеклассников Современные формы и приемы работы в рамках системно-деятельностного подхода

Современные формы и приемы работы в рамках системно-деятельностного подхода Декорирование аквариума яванским мхом

Декорирование аквариума яванским мхом התחביבים שלי

התחביבים שלי Команда Британский Парламент

Команда Британский Парламент Мои цели

Мои цели Книжка-малышка. Технология изготовления

Книжка-малышка. Технология изготовления Презентация на тему Музыкальные физминутки

Презентация на тему Музыкальные физминутки  Бобры - какие они. Для подготовительной группы

Бобры - какие они. Для подготовительной группы Вовлеченность родителей в систему краткосрочных образовательных практик в детском саду

Вовлеченность родителей в систему краткосрочных образовательных практик в детском саду Игра Четвертый лишний

Игра Четвертый лишний Дидактическая игра “Кому что нужно?“

Дидактическая игра “Кому что нужно?“