Содержание

- 2. Базовые логические элементы Компьютер выполняет арифметические и логические операции при помощи т.н. базовых логических элементов, которые

- 3. Составные элементы Любая логическая операция может быть представлена через конъюнкцию, дизъюнкцию и инверсию Любой сколь угодно

- 4. Сигналы-аргументы и сигналы-функции Вентили оперируют с электрическими импульсами: Импульс имеется – логический смысл сигнала «1» Импульса

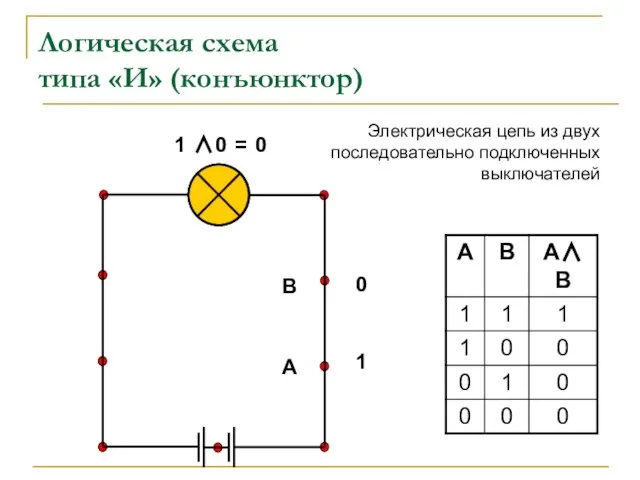

- 5. Логическая схема типа «И» (конъюнктор) 1 ∧ 0 = 0 1 0 A В Электрическая цепь

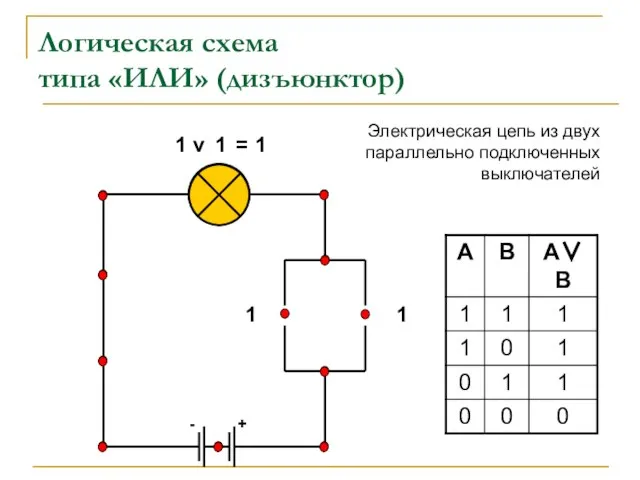

- 6. + - Логическая схема типа «ИЛИ» (дизъюнктор) 1 1 1 v 1 = 1 Электрическая цепь

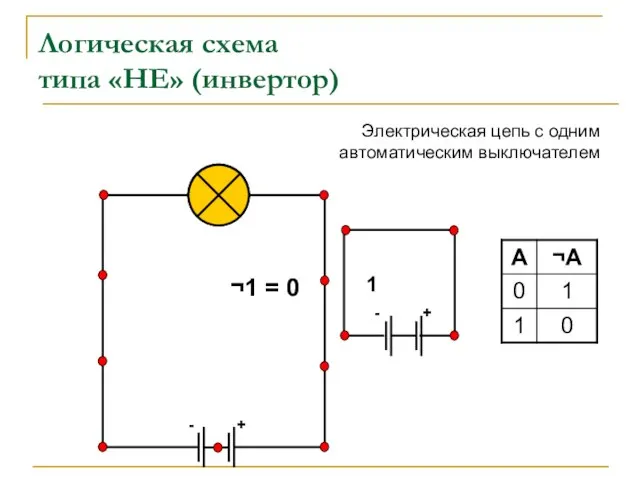

- 7. + - Логическая схема типа «НЕ» (инвертор) + - ¬1 = 0 1 Электрическая цепь с

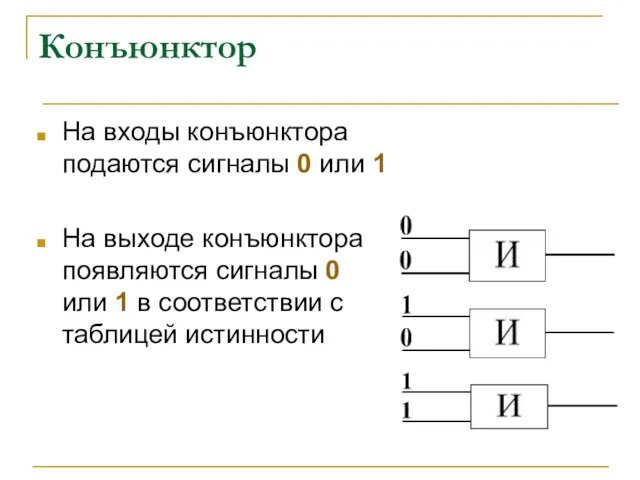

- 8. Конъюнктор На входы конъюнктора подаются сигналы 0 или 1 На выходе конъюнктора появляются сигналы 0 или

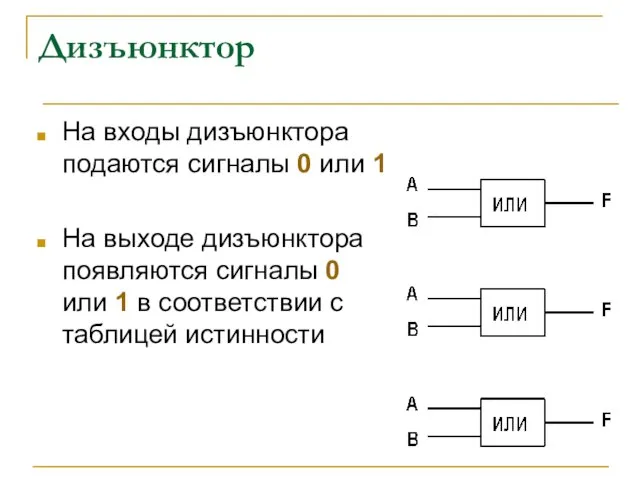

- 9. Дизъюнктор На входы дизъюнктора подаются сигналы 0 или 1 На выходе дизъюнктора появляются сигналы 0 или

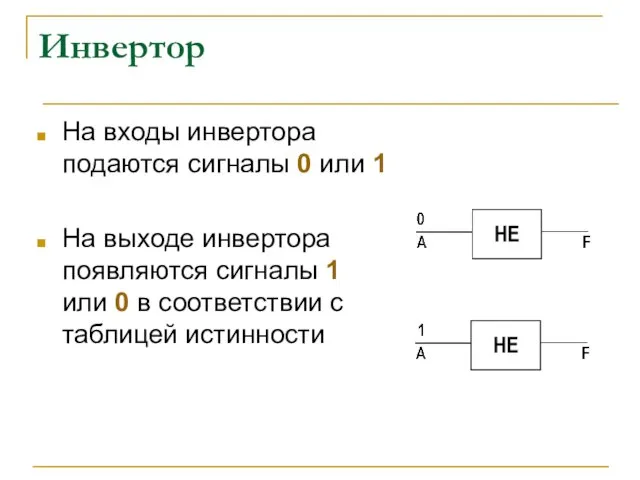

- 10. Инвеpтор На входы инвертора подаются сигналы 0 или 1 На выходе инвертора появляются сигналы 1 или

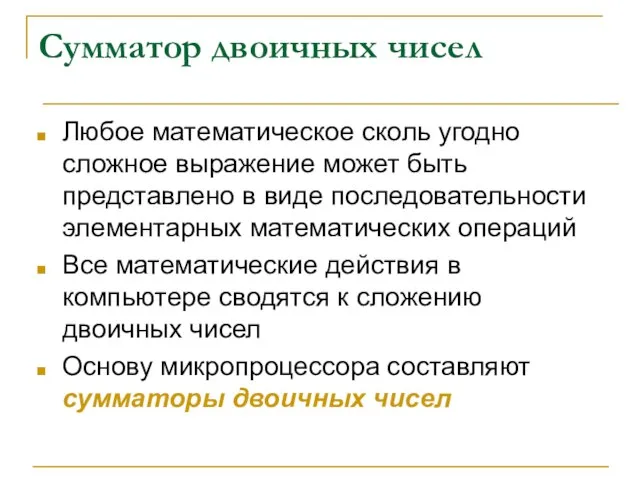

- 11. Сумматор двоичных чисел Любое математическое сколь угодно сложное выражение может быть представлено в виде последовательности элементарных

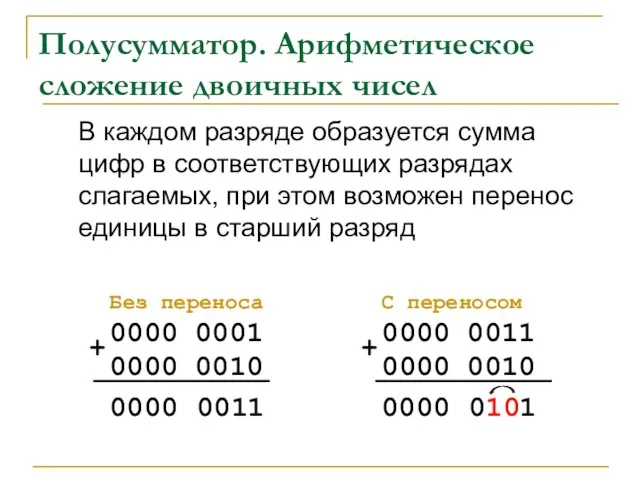

- 12. Полусумматор. Арифметическое сложение двоичных чисел В каждом разряде образуется сумма цифр в соответствующих разрядах слагаемых, при

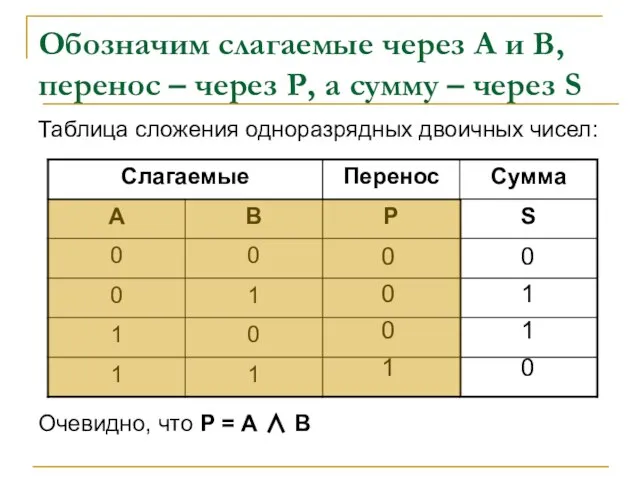

- 13. Обозначим слагаемые через А и В, перенос – через Р, а сумму – через S Таблица

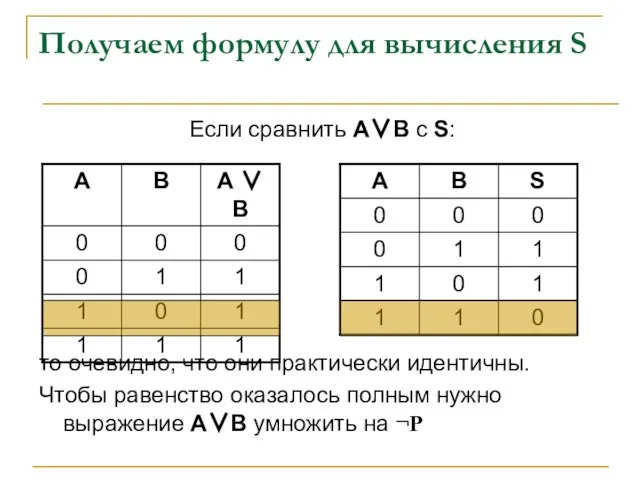

- 14. Получаем формулу для вычисления S Если сравнить А∨В c S: то очевидно, что они практически идентичны.

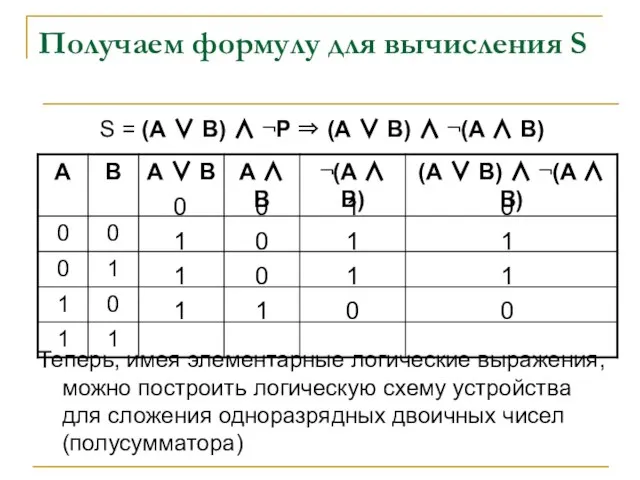

- 15. Получаем формулу для вычисления S S = (А ∨ В) ∧ ¬P ⇒ (А ∨ В)

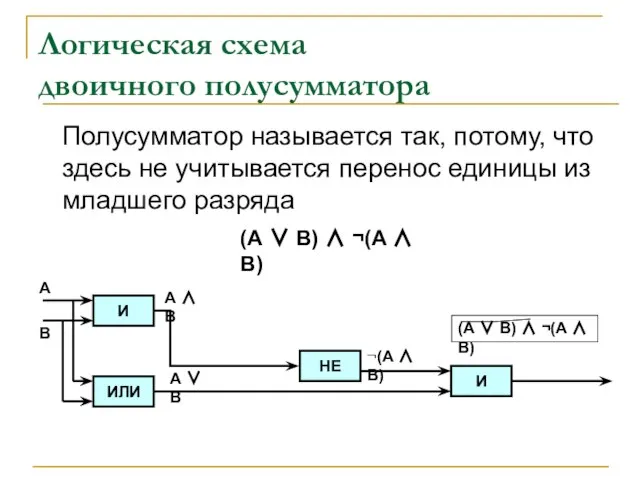

- 16. Логическая схема двоичного полусумматора Полусумматор называется так, потому, что здесь не учитывается перенос единицы из младшего

- 17. Полный одноразрядный сумматор Должен иметь три входа (А, В и Р0) и два выхода (S и

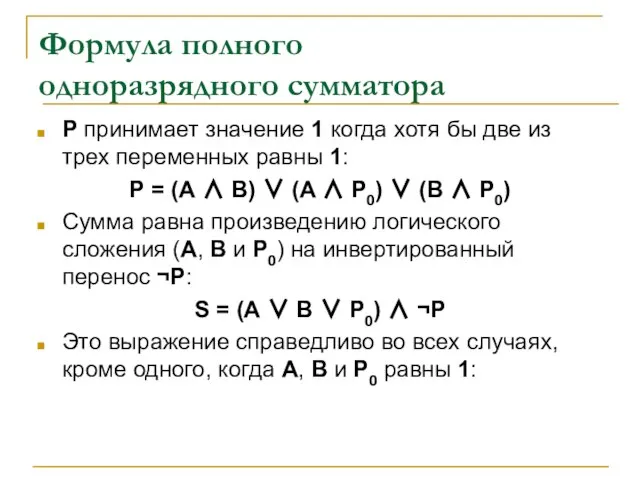

- 18. Формула полного одноразрядного сумматора Р принимает значение 1 когда хотя бы две из трех переменных равны

- 19. Формула полного одноразрядного сумматора Правильное значение суммы – 1. Для ее получения необходимо полученное выражение сложить

- 20. Многоразрядный сумматор Построен на основе полных одноразрядных сумматоров (по одному на каждый разряд), причем таким образом,

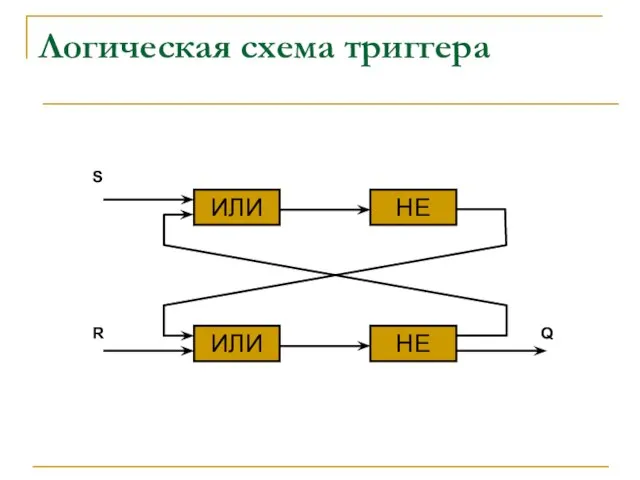

- 21. Триггер Важнейшая структурная единица оперативной памяти и регистров процессора Состоит из двух логических элементов «ИЛИ» и

- 22. Логическая схема триггера ИЛИ ИЛИ НЕ НЕ S R Q

- 24. Скачать презентацию

Вселенная, или космос 1 класс

Вселенная, или космос 1 класс Технология выполнения штукатурных работ Выполнил мастер п/о Гордеюк А.Л.

Технология выполнения штукатурных работ Выполнил мастер п/о Гордеюк А.Л. Метод сокращенных таблицдля генерации автоматовс большим числом входных воздействий

Метод сокращенных таблицдля генерации автоматовс большим числом входных воздействий Депрессия и стресс

Депрессия и стресс Модернизация страхового рынка в России и роль ОЭСР в этом процессе

Модернизация страхового рынка в России и роль ОЭСР в этом процессе Муниципальное образовательное учреждение «Пежемскаяобщеобразовательная средняя школа №14»

Муниципальное образовательное учреждение «Пежемскаяобщеобразовательная средняя школа №14» В чём секрет русской орфографии

В чём секрет русской орфографии Метание малого мяча

Метание малого мяча SMO

SMO Рычаг Архимеда

Рычаг Архимеда Экономика России 2-й половины XVIII века

Экономика России 2-й половины XVIII века Цикл жизни IT-специалиста в современной компании. IT и HR: взаимодействие

Цикл жизни IT-специалиста в современной компании. IT и HR: взаимодействие Proyecto en Lengua Española

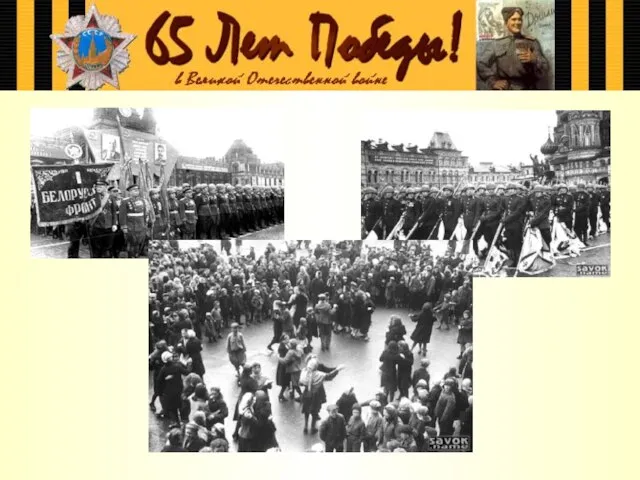

Proyecto en Lengua Española Вторжение на советскую землю началось На улицах осажденного Ленинграда.

Вторжение на советскую землю началось На улицах осажденного Ленинграда. Ферма Пьер

Ферма Пьер Презентация на тему Сочинение-описание помещения (6 класс)

Презентация на тему Сочинение-описание помещения (6 класс) Концепция духовно-нравственного развития и воспитания личности гражданина России

Концепция духовно-нравственного развития и воспитания личности гражданина России Презентация на тему создатель толкового словаряживого великорусского языка

Презентация на тему создатель толкового словаряживого великорусского языка Тема 10. ПРОФЕССИОНАЛЬНО-ПРИКЛАДНАЯ ФИЗИЧЕСКАЯ ПОДГОТОВКА СТУДЕНТОВ

Тема 10. ПРОФЕССИОНАЛЬНО-ПРИКЛАДНАЯ ФИЗИЧЕСКАЯ ПОДГОТОВКА СТУДЕНТОВ Seoul

Seoul Отчет Совета старшеклассников

Отчет Совета старшеклассников 7кл технические открытия

7кл технические открытия Лекция по дисциплине «Внешнеторговая документация» ТЕМА 1.1. Международная классификация внешнеторговых документов Принципы к

Лекция по дисциплине «Внешнеторговая документация» ТЕМА 1.1. Международная классификация внешнеторговых документов Принципы к Темперамент человека и мотивация

Темперамент человека и мотивация Давай поговорим поподробнее о зиме

Давай поговорим поподробнее о зиме Орфоэпические нормы

Орфоэпические нормы Презентация на тему Первые люди

Презентация на тему Первые люди  Надпредметная программа как способ приобщения школьников к чтению Ирина Евгеньевна Козлова, учитель русского языка и литератур

Надпредметная программа как способ приобщения школьников к чтению Ирина Евгеньевна Козлова, учитель русского языка и литератур