Слайд 2Архитектура простой эвм

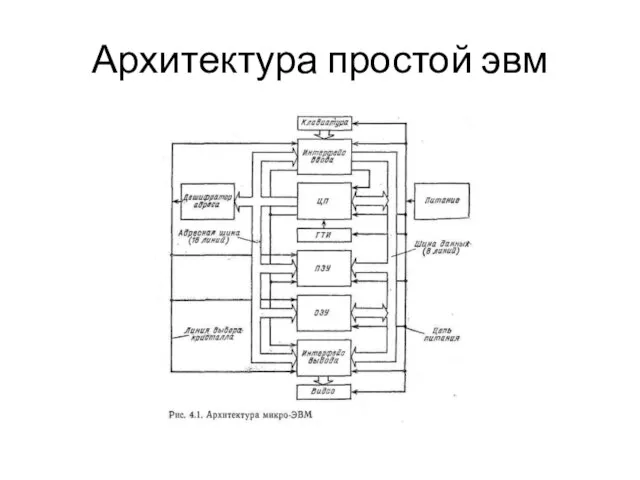

На рис. 4.1 приведена архитектура простой микро-ЭВМ. Микропроцессор является центром

всех операций. Ему необходимы питание и тактовые импульсы. Генератор тактовых импульсов может быть отдельным устройством или входить в состав кристалла МП. Типовой МП может содержать 16 адресных линий, которые составляют однонаправленную шину адресов, а также обычно восемь линий, которые составляют двунаправленную шину данных.

Архитектура, представленная на рис. 4.1, различает два типа полупроводниковой памяти, используемой системой. Постоянное запоминающее устройство ПЗУ представляет собой постоянную память, которая содержит программу-монитор системы. Оно содержит адресные входы, а также входы активизации только чтения и выбора кристалла, а также тристабильные выходы, подсоединяемые на шины. Очевидно, ПЗУ имеет также подсоединение питания, которое на схемах обычно не показывается.

Слайд 4Архитектура простой эвм

Архитектура на рис. 4.1 содержит ОЗУ, т. е. устройство временного

размещения данных. В него входят адресные входы, а также входы выбора кристалла и активизации чтения/записи. Это ОЗУ имеет восемь выходов с тремя состояниями, подсоединенных к шине данных. Здесь показан также источник питания.

Приведенная система микро-ЭВМ использует клавишное устройство ввода. На этой схеме показаны цепи питания, а также соответствующие линии данных, связанные со специальными ИС — интерфейсом ввода с клавиатуры.

В задачу интерфейса входит размещение данных и управление их вводом с клавиатуры. В нужный момент интерфейс клавиатуры прерывает МП по специальной линии прерывания.

Слайд 5Интерфейс ввода с клавиатуры

Сигнал прерывания заставляет МП:

1) закончить выполнение текущей команды;

2) поддерживать свою нормальную работоспособность;

3) перейти к выполнению специальной группы команд в своем мониторе, по которым ведется управление вводом данных, исходящих с клавишного устройства.

Система интерфейса с клавиатурой снабжена

адресными входами,

линиями выбора кристалла и команд

активизации устройства.

Активизированное один раз устройство интерфейса с клавиатурой передает данные, поступающие с клавишного устройства на шину данных, микропроцессор их принимает. Если тристабильные выходы интерфейса не активизированы, они возвращаются в свое состояние высокого сопротивления.

Слайд 6Интерфейс вывода

Приведенная на рис. 4.1 микро-ЭВМ имеет в качестве выхода группу семисегментных

индикаторов.

Индикаторы запитаны от источника, показанного на схеме справа.

Система или специальная ИС интерфейса вывода на индикаторы служит для размещения данных и управления состоянием индикаторов.

При активизации этого интерфейса по адресной шине, линиям выбора кристалла и активизации он принимает данные, поступающие с шины данных, и размещает их, а также управляет индикатором, на котором размещенные данные высвечиваются.

Слайд 7Интерфейс вывода

Адресная линия содержит 65 536 различных сочетаний О и 1 (216).

Линии адресной шины могут быть подсоединены ко многим устройствам, таким, как ОЗУ, ПЗУ, другие интерфейсы. Для того чтобы активизировать (включить в работу) требуемое устройство, дешифратор адреса считывает данные с адресной шины. Комбинационной логикой дешифратора адреса активизируется линия выбора соответствующего кристалла, активизируя, таким образом, выбранное устройство. Заметим, что для упрощения схемы все 16 линий адресной шины не показываются.

Слайд 8Структура простейшей памяти

Запись в память или считывание из нее происходит при наличии

доступа в память. Обычно память выполняется с последовательным или произвольным доступом.

Последовательный доступ означает, что к требуемым данным нужно последовательно пройти через всю память, расположенную до размещения искомых данных.

В случае произвольного доступа данные могут быть записаны в любую ячейку памяти или считаны из нее за определенное фиксированное время, называемое временем доступа в память.

Оперативные и постоянные запоминающие устройства микро-ЭВМ являются устройствами памяти с произвольным доступом, существенно более быстродействующими, чем устройства с последовательным доступом.

Слайд 9Структура простейшей памяти

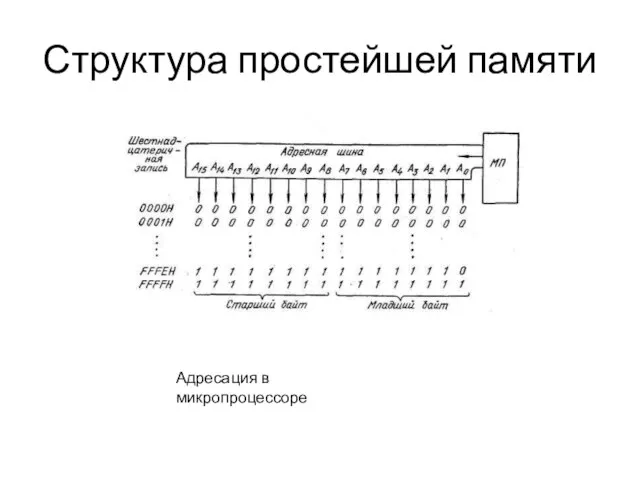

Изучаемый тип микро-ЭВМ обладает адресной шиной из 16 линий, которые

могут обеспечить 65536 (216) различных комбинаций 0 и 1. На рис. 4.2 приведено множество двоичных комбинаций. Обычно принято двоичный адрес представлять в шестнадцатеричной форме. Как видно из рис. 4.2, 0000 0000 0000 00002 = ООООН (000010).

Напомним, что здесь Н указывает на то, что речь идет о шестнадцатеричной системе счисления (Н-код). Наиболее значимым адресом на рис. 4.2 будет 1111 1111 1111 11112 или FFFFH.

Слайд 10Структура простейшей памяти

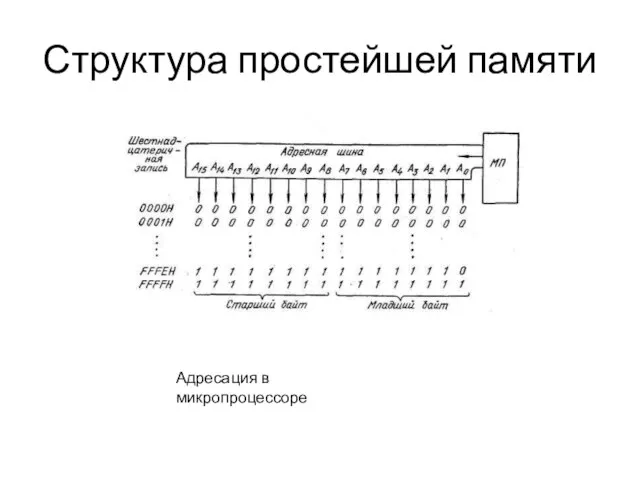

Адресация в микропроцессоре

Слайд 12Структура простейшей памяти

Схема на рис. 4.3 представляет собой воображаемую память микро-ЭВМ. Адресная

шина микропроцессора 16-разрядная, она может сформировать 65 536 (0000—FFFFH) индивидуальных адресов (некоторые из них представлены в шестнадцатеричной записи слева на рис. 4.3).

В случае этой специальной микро-ЭВМ первые 256 (00—FFH) ячеек памяти являются содержимым ПЗУ с объемом памяти 256x8 бит (т. е. 256 слов по 8 бит).

Если адресная шина формирует адрес ООООН, ПЗУ передает программированную комбинацию из 0 и 1, содержащуюся в постоянной памяти (слово 1100 ООН).

Слайд 13Структура простейшей памяти

Для людей, начинающих работать в области микропроцессорной техники, удобно, когда

256 (00—FFH) первых бит или слов данных в ПЗУ помещены на странице ООН.

Заметим, что номер страницы равен представлению в шестнадцатеричном коде старшего байта адреса (рис. 4.3).

При этих условиях, манипулируя данными на странице ООН, рассматриваются только две шестнадцатеричные цифры младшего разряда адреса.

Некоторые микропроцессоры используют упрощенные команды для доступа к ячейкам памяти первой страницы памяти

Слайд 14Структура простейшей памяти

Воображаемая элементарная память на рис. 4.3 показывает, что страницы от

01Н до 1FH (адреса от 0100Н до 1FFFH) в этом отдельном случае не содержат данных в памяти.

Получение доступа в эту открытую зону повлечет непредвиденный результат, поскольку она не содержит ни определенных данных, ни программы.

Оперативная память для чтения-записи расположена на странице 20Н (рис, 4.3). Устройство размещения данных это ОЗУ 256x8 бит,

Составители этой системы могли бы расположить это ОЗУ на любой другой странице.

Доступ к страницам 21Н—FFH в этом случае вызовет появление непредвиденного результата по мере вхождения в эту зону, здесь не существует никакой определенной информации.

Слайд 15Структура простейшей памяти

Если понадобится записать данные в ячейку памяти 2000Н (рис. 4.3),

восемь элементарных ячеек памяти в начале ОЗУ будут заполнены сочетанием нулей и единиц, поступающих с шины данных.

Если микропроцессор захочет затем считать из ячейки памяти по адресу 2000Н, в ОЗУ будет прочитано то же сочетание нулей и единиц.

Физически ОЗУ должно быть, очевидно, составлено единственной ИС. Но получается, однако, что очень часто ОЗУ строятся иначе.

На рис. 4.3 заштрихованная часть размещения данных в ОЗУ разделена посредине вертикально. Это указывает на то, что в этом случае зона размещения данных на странице 20Н физически состоит из двух различных ИС. Здесь для реализации зоны памяти 256x8 на странице 20Н микро-ЭВМ использованы два ОЗУ 256X4 бит.

Слайд 17Структура простейшей памяти

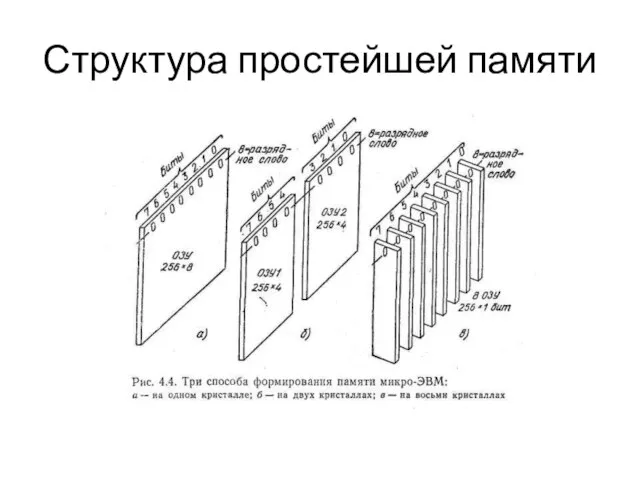

На рис. 4.4 приведены три варианта реализуемых устройств ИС полупроводникового

ОЗУ. На рис. 4.4, а единая ИС организована в ОЗУ 256X8 бит, на рис. 4.4, б две ИС составляют такую же зону размещения данных и, следовательно, два ОЗУ 256X4 бит позволяют составить слово из 8 бит. Наконец, восемь ОЗУ на рис. 4,4, в формируют также устройство размещения для записи-чтения данных 256X8 бит.

Устройство, представленное на рис. 4.4, в, широко используется для составления обширной памяти. Обычно используют ИС ОЗУ 1024X1, 4096X1, 16384x1 бит. Используя способ, показанный на рис. 4.4, в, восемь ОЗУ 4096Х 1 бит будет достаточно для формирования оперативной памяти 4096x8 бит. Отметим, что в этом типе конфигурации такие ОЗУ будут активизированы одной и той же линией выбора кристалла, исходящей из дешифратора адресов.

В системе микро-ЭВМ объем памяти (или память 4096X8 бит) составляет 4 Кбайт (4 К=4096 байт памяти)1.

Слайд 18СОСТАВ КОМАНД

Группа команд, которые может выполнять данный МП, называется его составом команд.

Состав команд МП может содержать как малое число (восемь), так и большое число (200) основных команд. Составы команд не являются нормированными . Это неудобство связано как с индивидуальным подходом к разработке, так и с различиями архитектуры и назначений МП.

Имеется много способов классификации команд одного состава. В этой главе согласно нормативам, предложенным научным обществом инженеров-электронщиков (IEEE),

Слайд 19СОСТАВ КОМАНД

мы изучим следующие команды:

арифметические,

логические,

передачи данных,

вызова подпрограмм,

возврата

из подпрограмм,

прочие.

Слайд 20СОСТАВ КОМАНД

Элементарный МП будет представлен следующим составом арифметических команд: сложение, вычитание, инкрементирование,

сравнение, отрицание.

Некоторые конкретные МП могут обладать другими арифметическими командами, такими, как сложение с переносом, вычитание с заемом, умножение и деление.

Элементарный МП наделяется следующими логическими командами: И, ИЛИ, ИЛИ ИСКЛЮЧАЮЩЕЕ, НЕ (отрицание), сдвиг вправо, сдвиг влево.

Некоторые МП, кроме того, наделены такими логическими командами, как арифметический сдвиг вправо, циклические сдвиги вправо и влево, циклические сдвиги вправо и влево с переносом и тестирование.

Слайд 21СОСТАВ КОМАНД

Наш же элементарный процессор всегда наделяется командами передачи данных: загрузки, размещения,

перемещения, ввода, вывода.

Более сложный состав будет содержать команды обмена, сброса и инициализации.

Что касается команд ветвления, они следующие: безусловный переход; переход, если нуль; переход, если не нуль; переход, если равенство; переход, если неравенство; переход, если положительно; переход, если отрицательно.

Слайд 22СОСТАВ КОМАНД

Другие команды условных переходов, имеющиеся в некоторых микропроцессорах, могут зависеть от

таких условий, как: больше или меньше, сдвиг или нет, переполнение или нет. Команды ветвления являются командами принятия решений.

Элементарный микропроцессор будет наделен командой вызова подпрограммы (обычно CALL—вызов), чтобы программа могла перейти к специальной группе команд, которые решают поставленную задачу.

Все МП обладают командой безусловного вызова, а некоторые наделены командой условного вызова, например, CALL, если нуль;

Слайд 23СОСТАВ КОМАНД

CALL, если не нуль; CALL, если положительно или не положительно, и

т. д.

В конце выполнения подпрограммы МП должен иметь возможность возврата в точку отправления из начальной программы. Эта операция выполняется командой возврата.

Эта команда обычно безусловна, но некоторые МП снабжены и условным возвратом.

Наконец, прочими командами элементарного МП будут: нет операции, поместить в стек, выйти из стека, ожидание, останов.

Возможны и другие команды: прерывания активизации или сброса, останова, десятичной коррекции.

Слайд 24СОСТАВ КОМАНД

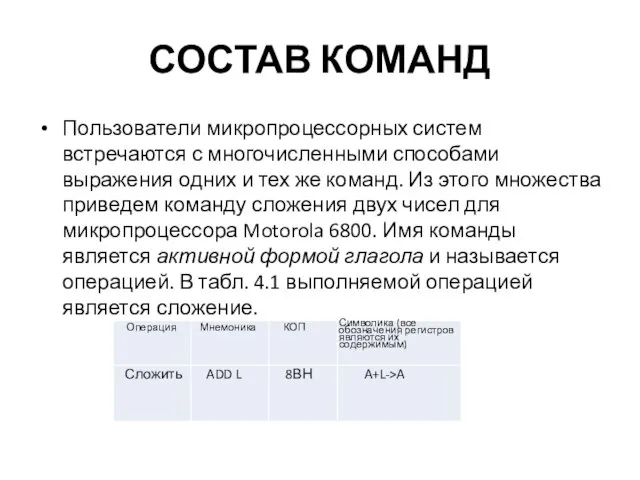

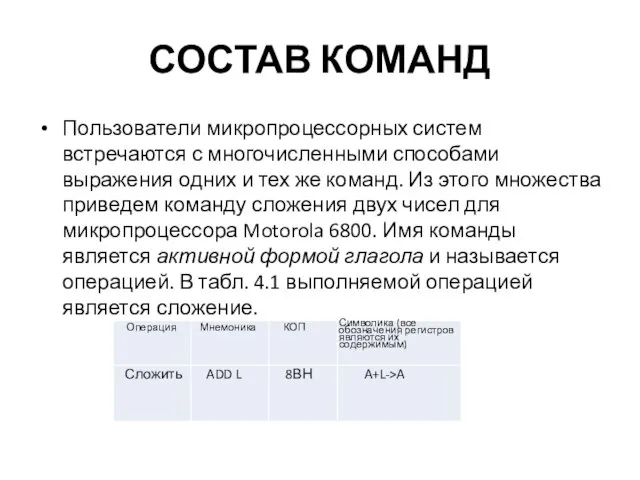

Пользователи микропроцессорных систем встречаются с многочисленными способами выражения одних и тех

же команд. Из этого множества приведем команду сложения двух чисел для микропроцессора Motorola 6800. Имя команды является активной формой глагола и называется операцией. В табл. 4.1 выполняемой операцией является сложение.

Слайд 25СОСТАВ КОМАНД

Пользователи работают часто с сокращенными формами выражения операции, которые являются обычно

мнемоническими.

В табл. мнемоникой сложения является ADD А (отметим, что мнемоники всегда записываются большими буквами). Регистр команд и схема декодирования понимают только язык нулей и единиц.

Код операции (КОП) является шестнадцатеричным представлением 8-разрядного двоичного кода, который заставляет МП выполнить эту команду.

В табл. КОП для МП Motorola 6800 для ADD А будет 8ВН (1000 10112). В колонке символики в табл. 4,1 показывается, что содержимое памяти (М) складывается с содержимым аккумулятора (А) в МП, стрелка указывает, что результат помещается в аккумулятор А.

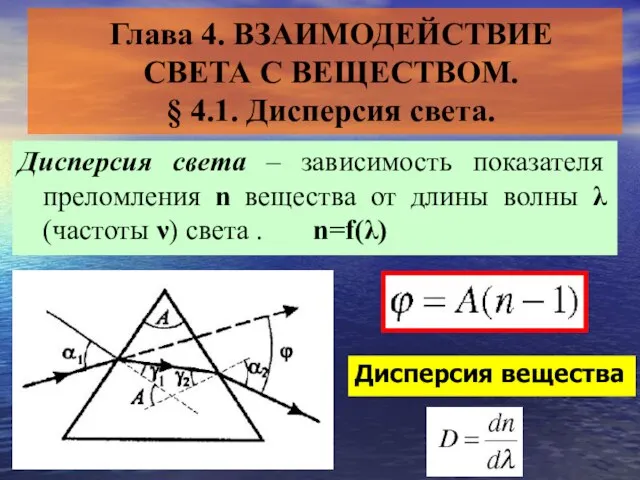

Презентация на тему Взаимодействие света с веществом Дисперсия света

Презентация на тему Взаимодействие света с веществом Дисперсия света

Бизнес-план. Создание детского кафе Счастливое детство

Бизнес-план. Создание детского кафе Счастливое детство Современные и забытые виды спорта

Современные и забытые виды спорта СВЯЗЬ ИННОВАЦИИ СЕРВИС

СВЯЗЬ ИННОВАЦИИ СЕРВИС Аттестационная работа. Пищевые добавки и их влияние на организм

Аттестационная работа. Пищевые добавки и их влияние на организм ООО МДО Душанбе Сити

ООО МДО Душанбе Сити Понятие о профессии, специальности и квалификации работника. Классификация профессий

Понятие о профессии, специальности и квалификации работника. Классификация профессий Производственное здание и зем. участок

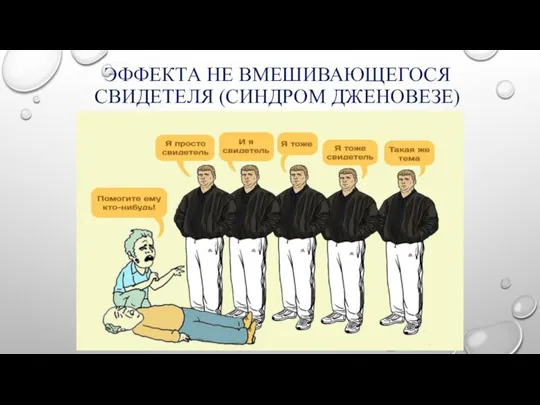

Производственное здание и зем. участок Эффекта не вмешивающегося свидетеля (синдром Дженовезе)

Эффекта не вмешивающегося свидетеля (синдром Дженовезе) Программа Intel «Путь к успеху» Итоги развития программы в 2008 году

Программа Intel «Путь к успеху» Итоги развития программы в 2008 году Стиль рококо. Художественное направление XVII – XVIII веков

Стиль рококо. Художественное направление XVII – XVIII веков Тема: Реальдо Коломбо: описание циркуляции крови через лёгкие.

Тема: Реальдо Коломбо: описание циркуляции крови через лёгкие. Инженер по гарантии. Шаблон документа

Инженер по гарантии. Шаблон документа МЕЛЬНИЦЫ Новейшая разработка в технологии ультратонкого измельчения

МЕЛЬНИЦЫ Новейшая разработка в технологии ультратонкого измельчения Комитет государственного имущества и приватизации Министерства финансов Республики Казахстан (КГИП)

Комитет государственного имущества и приватизации Министерства финансов Республики Казахстан (КГИП) Лекарственные препараты действующие на собирательные трубки

Лекарственные препараты действующие на собирательные трубки  Участник : Тугумбаев Алибек Айтуллаевич Открытие автокинотеатра «Sky cinema» в г. Астана.

Участник : Тугумбаев Алибек Айтуллаевич Открытие автокинотеатра «Sky cinema» в г. Астана. Гуманизм и новая наука

Гуманизм и новая наука Историческая справка Здание нашего детского сада было построено в 19.. году За это время здесь побывали и ясли и центр детского твор

Историческая справка Здание нашего детского сада было построено в 19.. году За это время здесь побывали и ясли и центр детского твор Общие принципы составления программ инфузионной терапии (ИТ) у детей Обедин А.Н. Ставрополь 2004

Общие принципы составления программ инфузионной терапии (ИТ) у детей Обедин А.Н. Ставрополь 2004 Удивительная вода

Удивительная вода Психология цвета

Психология цвета Техническая эксплуатация судовых АКБ

Техническая эксплуатация судовых АКБ Презентация на тему Математическая логика

Презентация на тему Математическая логика Организационно-правовые основы деятельности любительских объединений. Тема 6

Организационно-правовые основы деятельности любительских объединений. Тема 6 Создание республиканской медицинской информационной системы (РМИС)

Создание республиканской медицинской информационной системы (РМИС) Как правильно ставить цели и достигать их

Как правильно ставить цели и достигать их Оборотные средства предприятия

Оборотные средства предприятия