Содержание

- 2. Архитектура Микроархитектура Набор внутренних устройств Взаимодействие устройств Интерфейс для работы с процессором Набор используемых команд Набор

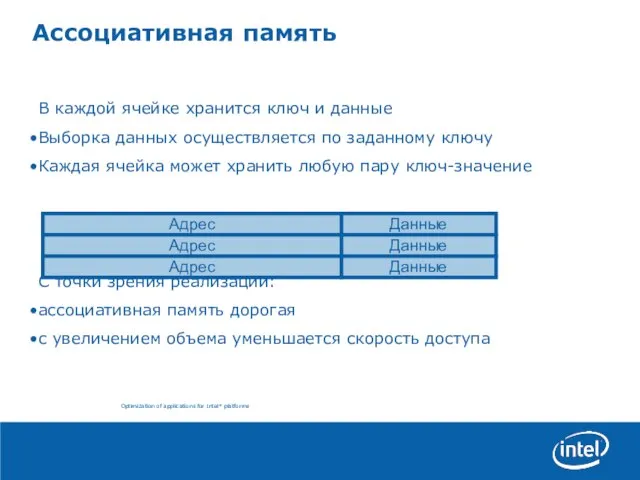

- 3. Ассоциативная память В каждой ячейке хранится ключ и данные Выборка данных осуществляется по заданному ключу Каждая

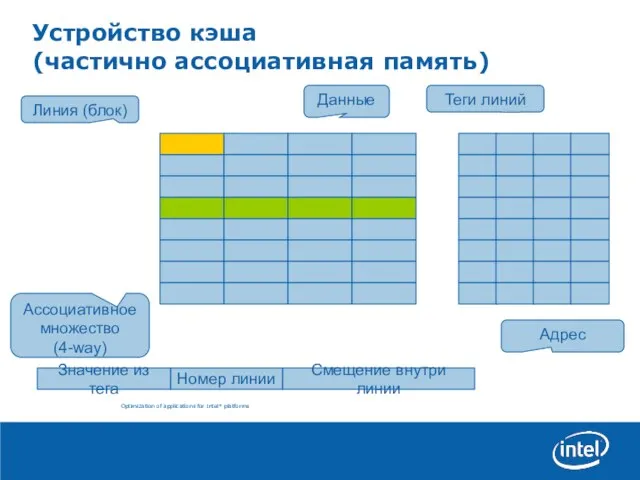

- 4. Устройство кэша (частично ассоциативная память) Значение из тега Номер линии Смещение внутри линии Адрес Линия (блок)

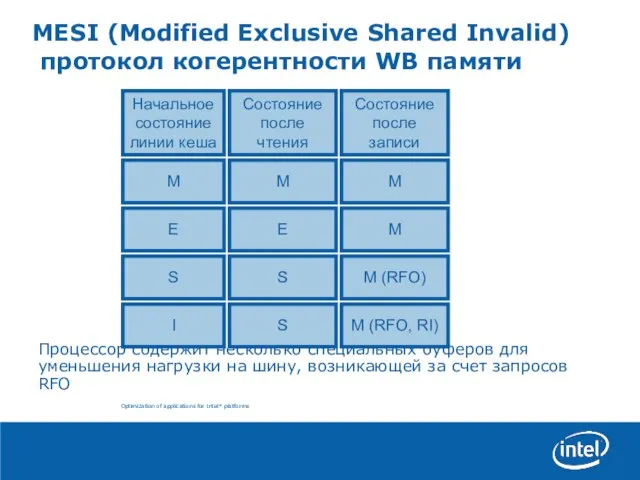

- 5. MESI (Modified Exclusive Shared Invalid) протокол когерентности WB памяти Процессор содержит несколько специальных буферов для уменьшения

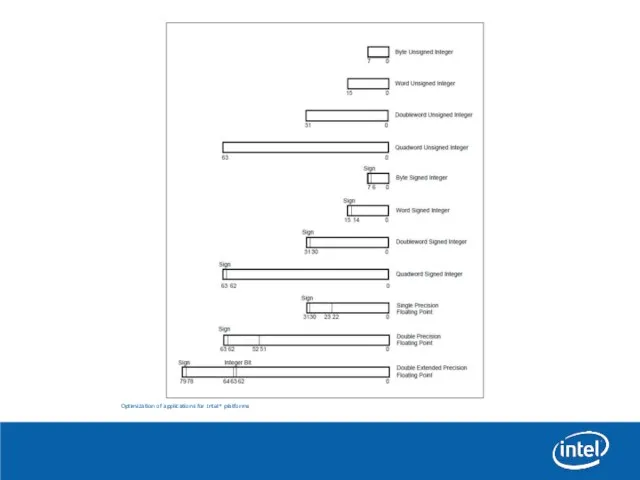

- 6. Типы данных Целые (8, 16, 32, 64 бита) без знака со знаком Числа с плавающей точкой

- 8. Целочисленные регистры (32-битный режим) Регистры общего назначения(General-purpose registers): 8 32-битных регистров используются 32-битном режиме для обращения

- 9. Целочисленные регистры (64-битный режим) Регистры общего назначения(General-purpose registers): 16 64-битных регистров используются 32-битном режиме для обращения

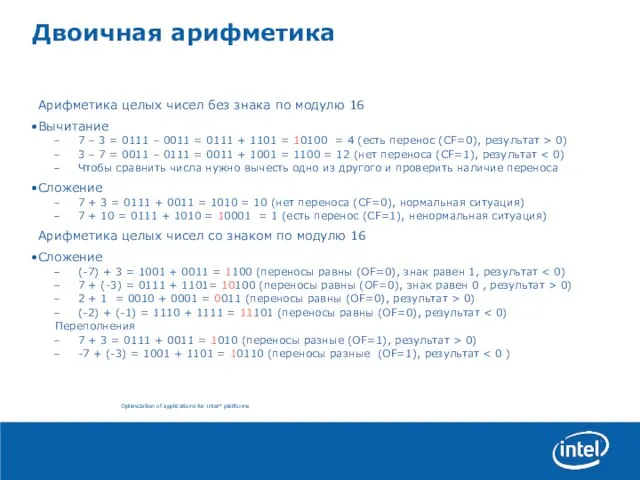

- 10. Двоичная арифметика Арифметика целых чисел без знака по модулю 16 Вычитание 7 – 3 = 0111

- 12. x87 регистры

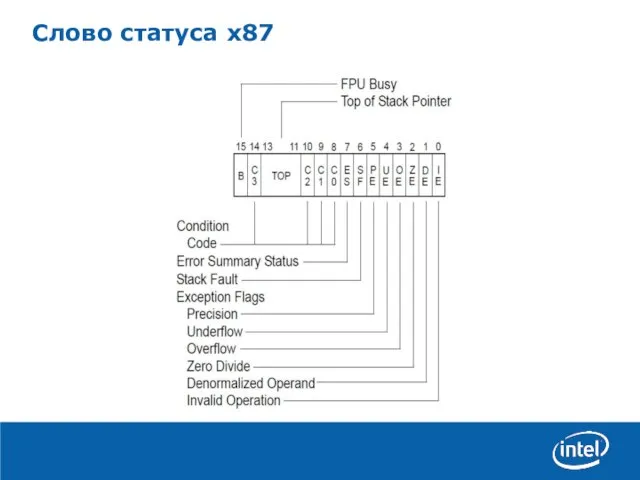

- 13. Слово статуса x87

- 14. Контрольное слово x87

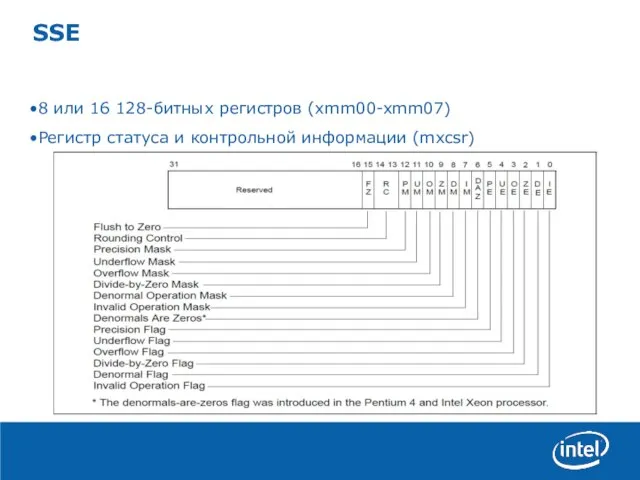

- 15. SSE 8 или 16 128-битных регистров (xmm00-xmm07) Регистр статуса и контрольной информации (mxcsr)

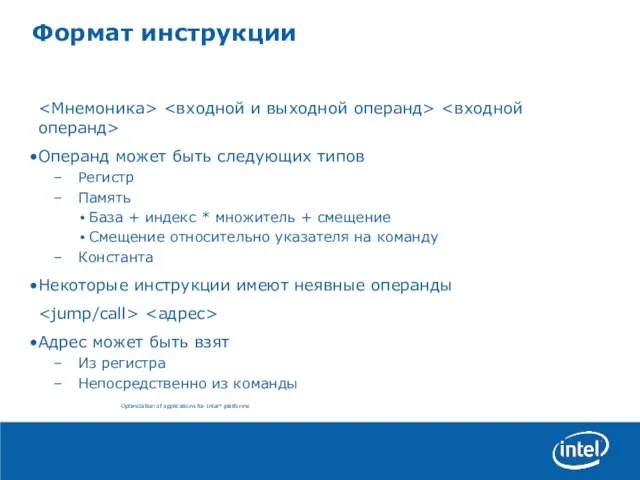

- 16. Формат инструкции Операнд может быть следующих типов Регистр Память База + индекс * множитель + смещение

- 17. Примеры инструкций Add rax, [rbx + 2*rdx + 8] (rax Mul rcx (rdx:rax Cmp rcx, rdi

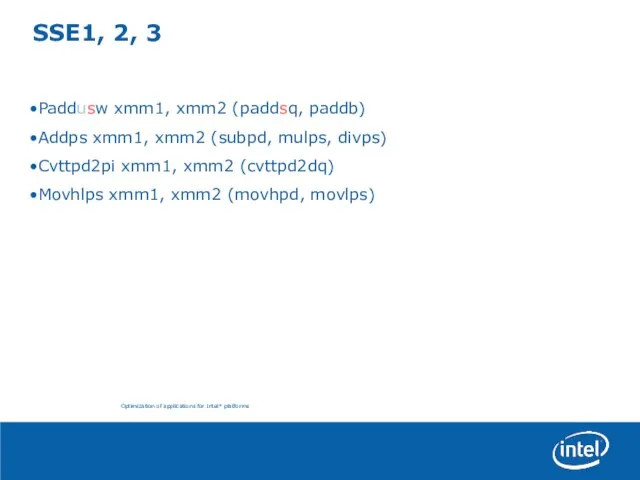

- 18. SSE1, 2, 3 Paddusw xmm1, xmm2 (paddsq, paddb) Addps xmm1, xmm2 (subpd, mulps, divps) Cvttpd2pi xmm1,

- 19. Q&A

- 21. Скачать презентацию

![Примеры инструкций Add rax, [rbx + 2*rdx + 8] (rax Mul rcx](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/431967/slide-16.jpg)

www.elsp.ru

www.elsp.ru Коммунарская методика: история и настоящее

Коммунарская методика: история и настоящее Презентация по картине И.И. Шишкина «Зима»

Презентация по картине И.И. Шишкина «Зима» Введение в дизайн-мышление

Введение в дизайн-мышление Презентация « Природные зоны Африки.» Составитель: Коробкина Елена Геннадьевна учитель географии Кировской средней общеобразова

Презентация « Природные зоны Африки.» Составитель: Коробкина Елена Геннадьевна учитель географии Кировской средней общеобразова Тема : «Анализ интегрированных программ по искусству. Интегрированное занятие» Цель: активизировать знания программ по искусст

Тема : «Анализ интегрированных программ по искусству. Интегрированное занятие» Цель: активизировать знания программ по искусст Мотивация как функция управления

Мотивация как функция управления CMMI Appraisal – Cost Control and Extra Business Benefit

CMMI Appraisal – Cost Control and Extra Business Benefit Безопасность общения в Социальных Сетях. Для детей и взрослых

Безопасность общения в Социальных Сетях. Для детей и взрослых Влияние групповой сплочённости на самооценку учащихся

Влияние групповой сплочённости на самооценку учащихся Пермхимпродукт. Каталог

Пермхимпродукт. Каталог Фонетика тата графика

Фонетика тата графика Антон Павлович Чехов 1860-1904

Антон Павлович Чехов 1860-1904 семинар Шымкент

семинар Шымкент Курьер доставляющего сервиса Чекбокс. Тренинг

Курьер доставляющего сервиса Чекбокс. Тренинг Отечественная война 1812 года

Отечественная война 1812 года Языковые переводы: человек vs. машинный перевод

Языковые переводы: человек vs. машинный перевод Салат здоровья

Салат здоровья РИМСКОЕ ПРАВО

РИМСКОЕ ПРАВО Классификация и устройство копировальных аппаратов

Классификация и устройство копировальных аппаратов Исследование физических явлений

Исследование физических явлений Русские народные игры

Русские народные игры Доброввольное пребывание человека в природной среде

Доброввольное пребывание человека в природной среде Изучение и обобщение передового педагогического опыта

Изучение и обобщение передового педагогического опыта Исследование силовой подготовки девушек и женщин, занимающихся фитнесом

Исследование силовой подготовки девушек и женщин, занимающихся фитнесом Западная Европа в 16-17 вв. Общая характеристика эпохи Раннего Нового времени

Западная Европа в 16-17 вв. Общая характеристика эпохи Раннего Нового времени IT конференция о компании DexSys

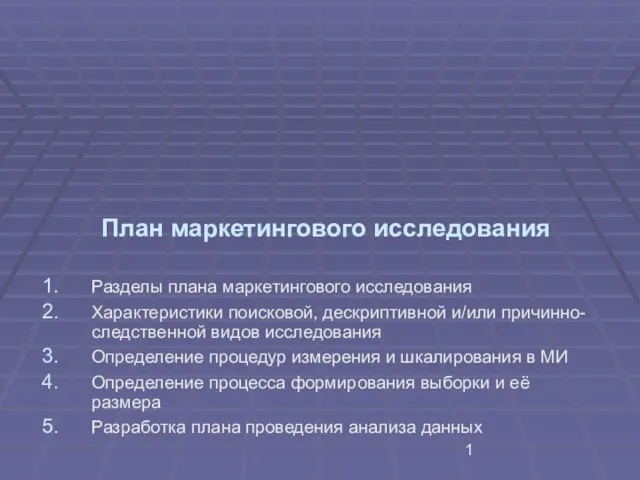

IT конференция о компании DexSys План маркетингового исследования

План маркетингового исследования