Содержание

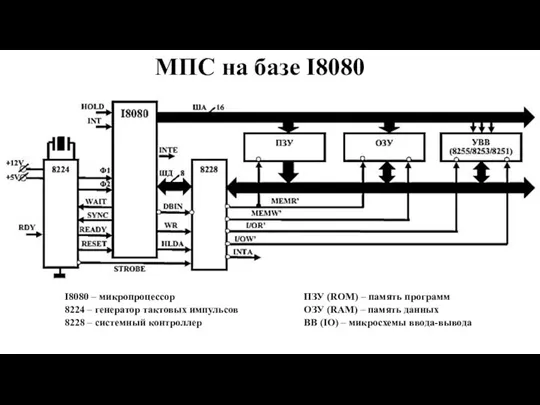

- 2. МПС на базе I8080 I8080 – микропроцессор 8224 – генератор тактовых импульсов 8228 – системный контроллер

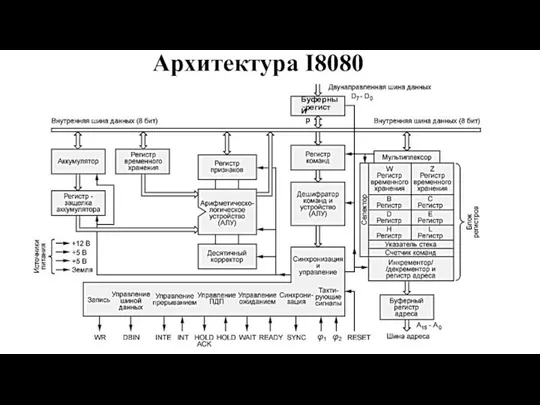

- 3. Архитектура I8080 Буферный регистр

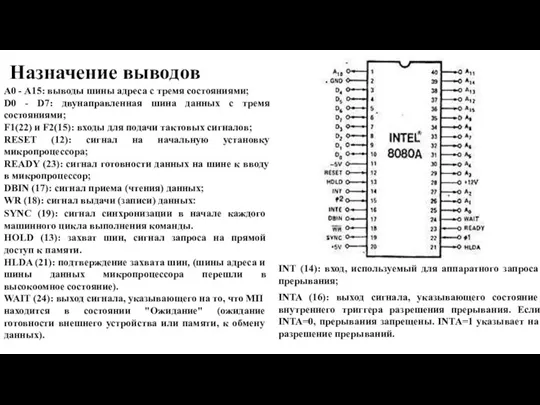

- 4. A0 - A15: выводы шины адреса с тремя состояниями; D0 - D7: двунаправленная шина данных с

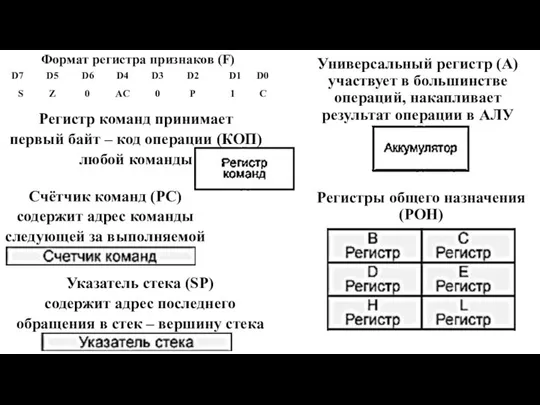

- 5. Регистры общего назначения (РОН) Формат регистра признаков (F) Универсальный регистр (А) участвует в большинстве операций, накапливает

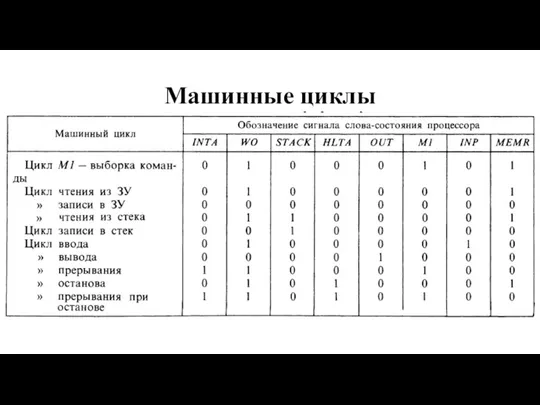

- 6. Машинные циклы

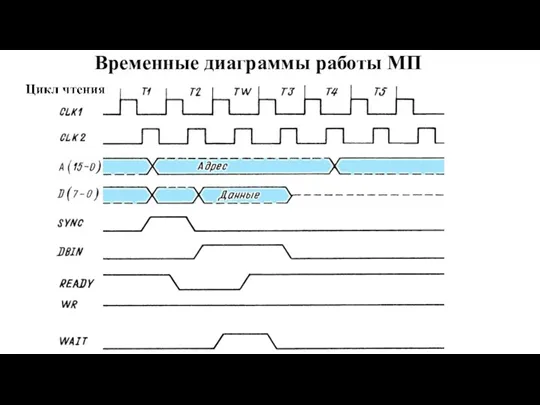

- 7. Временные диаграммы работы МП

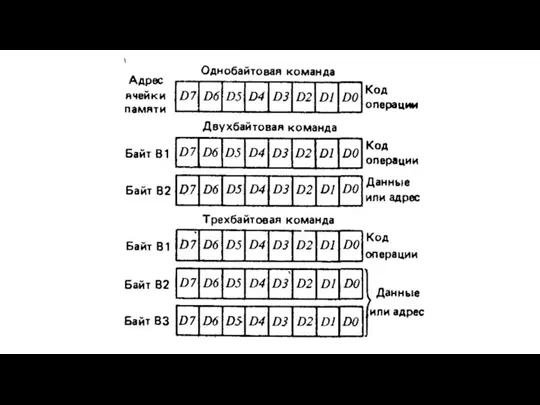

- 9. Способы адресации

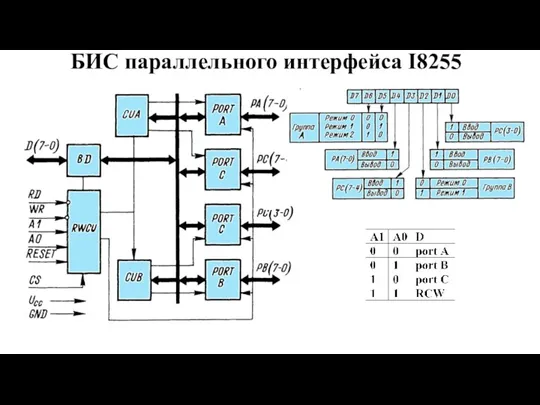

- 10. БИС параллельного интерфейса I8255

- 11. Подключение контактного датчика

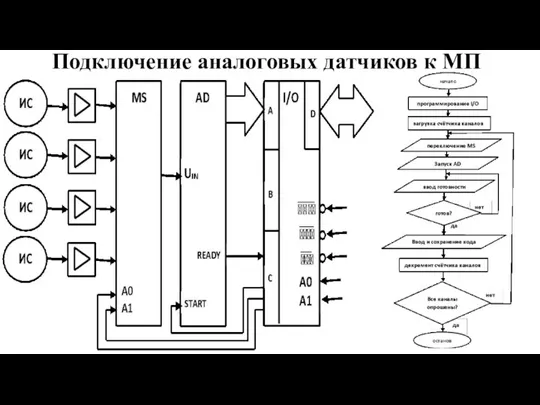

- 12. Подключение аналоговых датчиков к МП

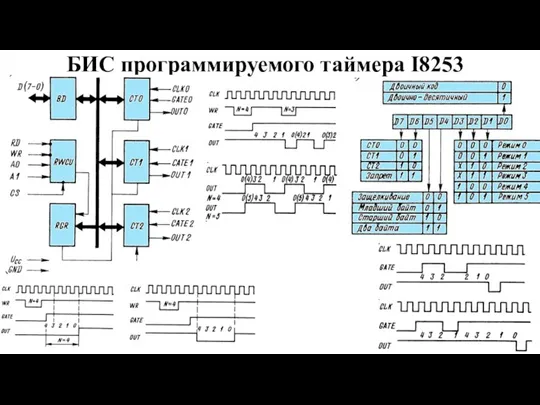

- 13. БИС программируемого таймера I8253

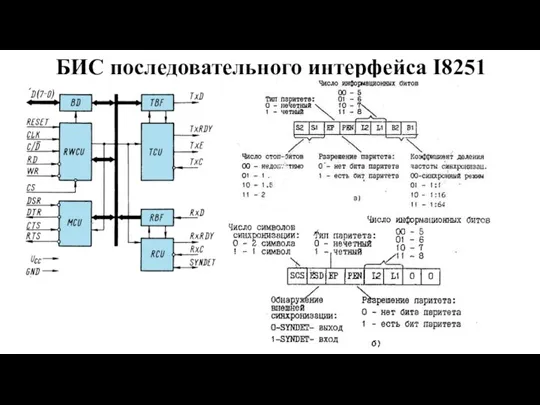

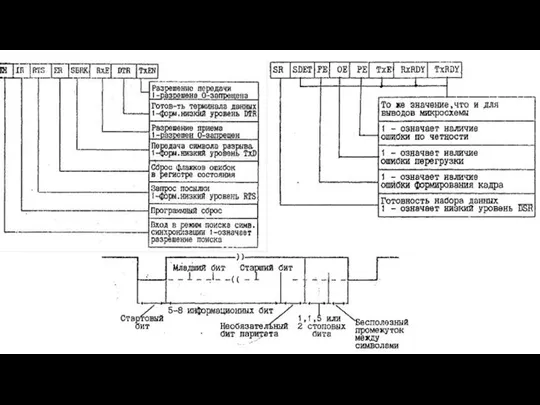

- 14. БИС последовательного интерфейса I8251

- 16. БИС контроллера прерываний I8259

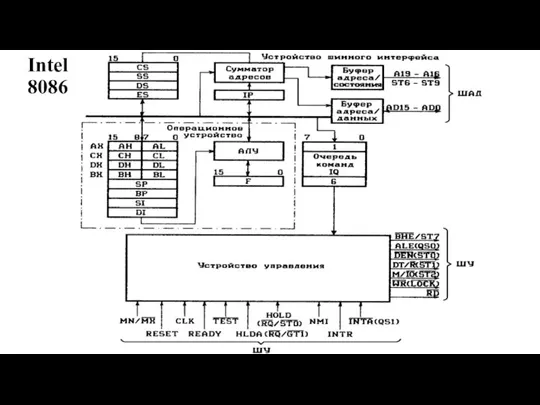

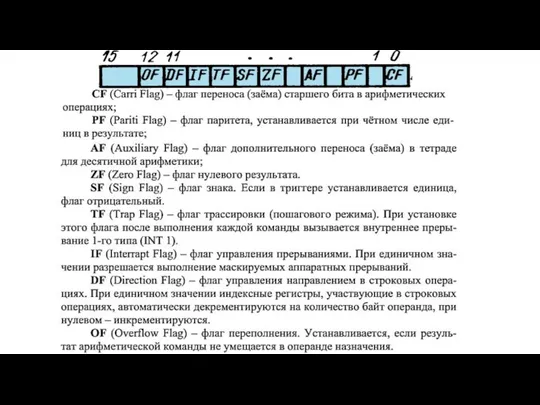

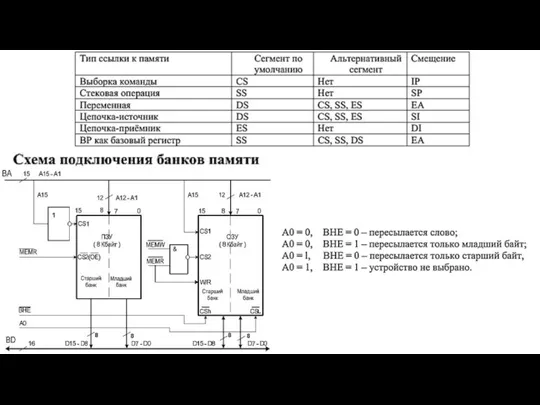

- 17. Intel 8086

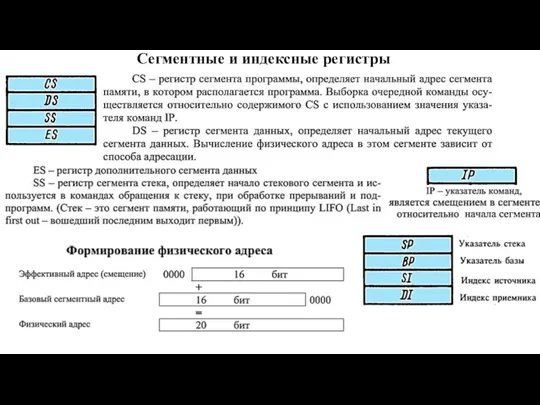

- 18. Сегментные и индексные регистры

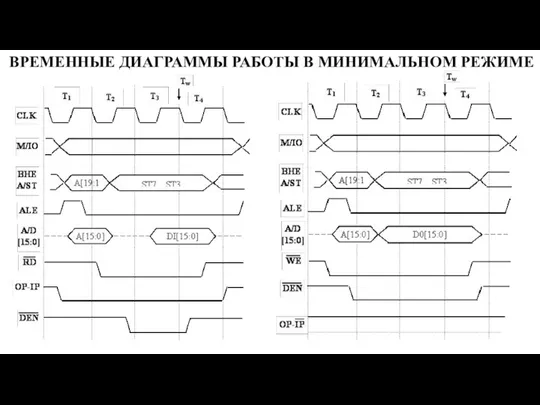

- 21. ВРЕМЕННЫЕ ДИАГРАММЫ РАБОТЫ В МИНИМАЛЬНОМ РЕЖИМЕ

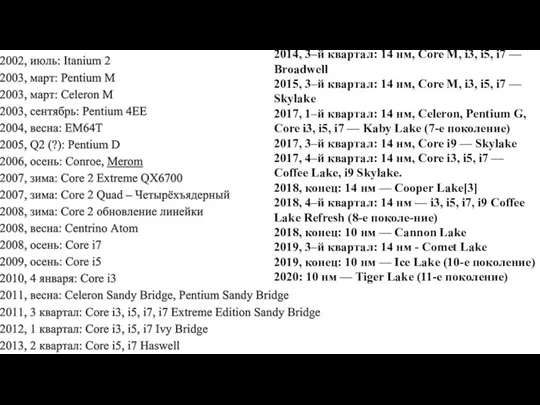

- 23. 2014, 3–й квартал: 14 нм, Core M, i3, i5, i7 — Broadwell 2015, 3–й квартал: 14

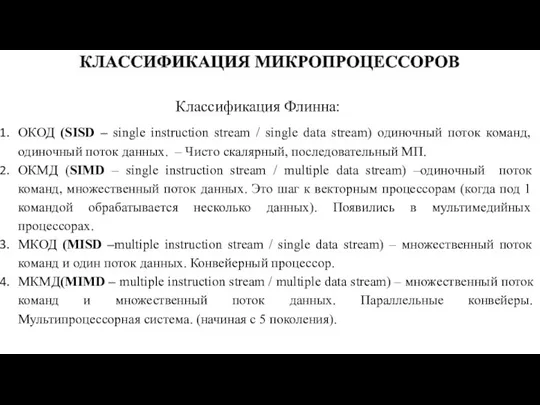

- 24. ОКОД (SISD – single instruction stream / single data stream) одиночный поток команд, одиночный поток данных.

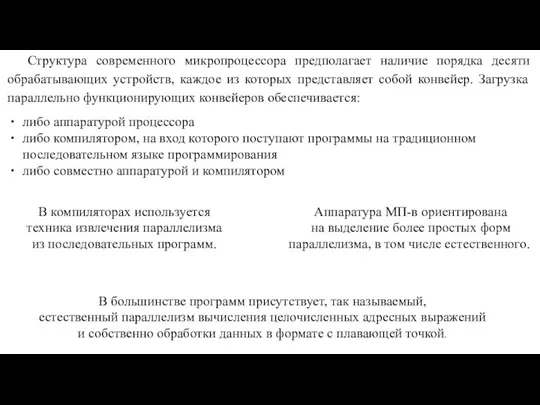

- 25. Структура современного микропроцессора предполагает наличие порядка десяти обрабатывающих устройств, каждое из которых представляет собой конвейер. Загрузка

- 26. Микропроцессор с разнесенной архитектурой Расщепление общей программы на программы для А- и Е- процессоров осуществляется на

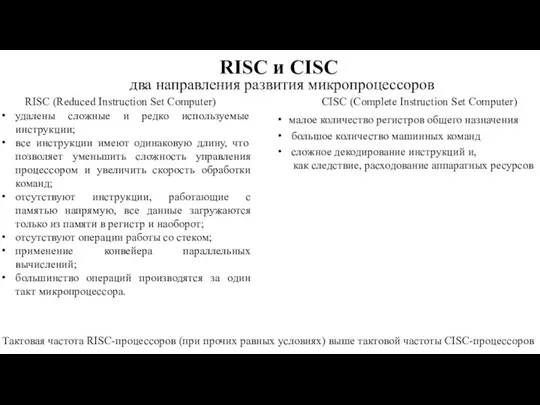

- 27. два направления развития микропроцессоров RISC и CISC RISC (Reduced Instruction Set Computer) удалены сложные и редко

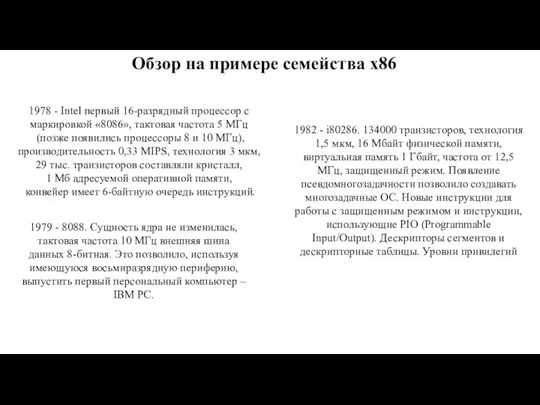

- 28. Обзор на примере семейства х86 1978 - Intel первый 16-разрядный процессор с маркировкой «8086», тактовая частота

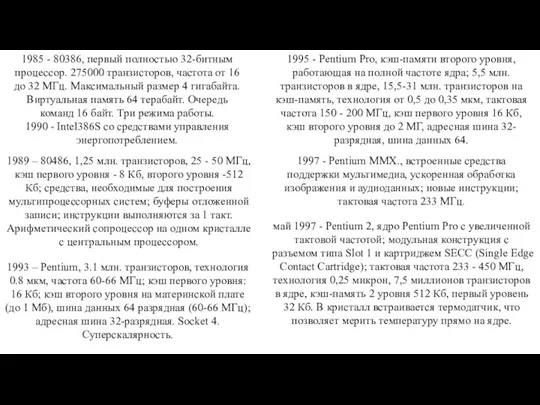

- 29. 1985 - 80386, первый полностью 32-битным процессор. 275000 транзисторов, частота от 16 до 32 МГц. Максимальный

- 30. 1999 - ядро Katmai - введено расширение SSE (Streaming SIMD Extensions), инструкции одновременно над группой операндов

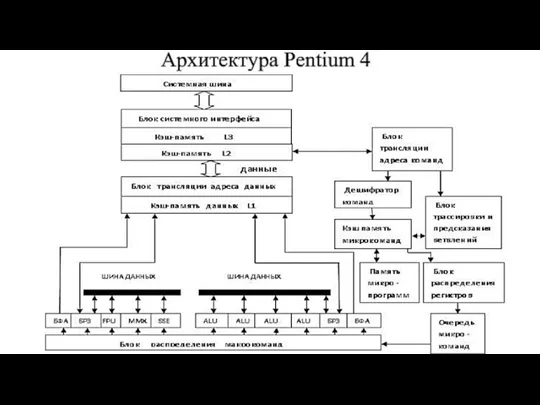

- 31. 2000 - Pentium 4 (Willamette), 0,18 мкм технология, 42 млн. транзисторов на кристалле, частоты от 1.4

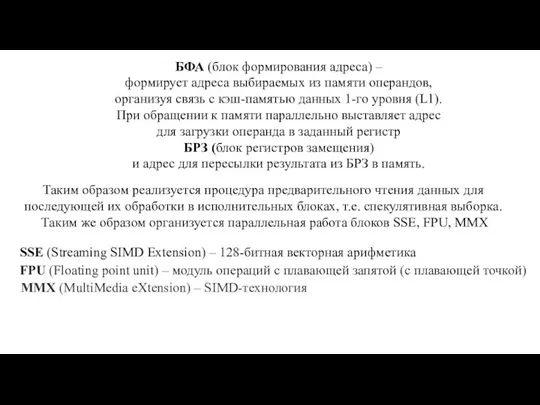

- 33. БФА (блок формирования адреса) – формирует адреса выбираемых из памяти операндов, организуя связь с кэш-памятью данных

- 34. Система команд 80х86 подразделяется на группы: • команды передачи данных; • команды арифметических операций над целыми

- 35. Регистровая адресация – операнды могут находиться в любых регистрах общего назначения и сегментных. Непосредственная адресация –

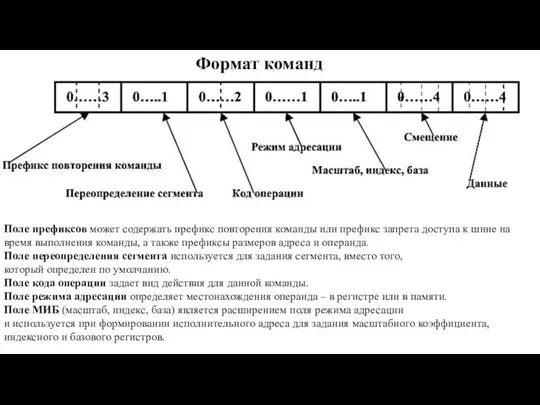

- 36. Формат команд Поле префиксов может содержать префикс повторения команды или префикс запрета доступа к шине на

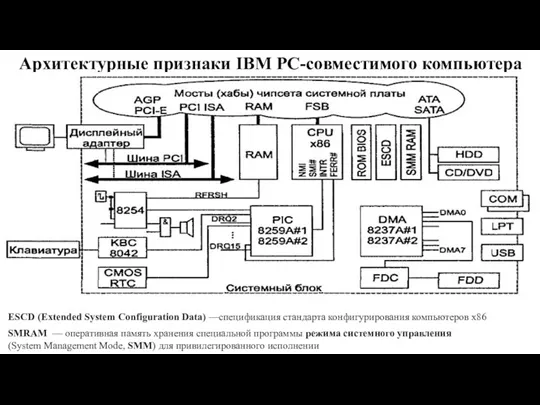

- 37. Архитектурные признаки IBM PC-совместимого компьютера ESCD (Extended System Configuration Data) —спецификация стандарта конфигурирования компьютеров х86 SMRAM

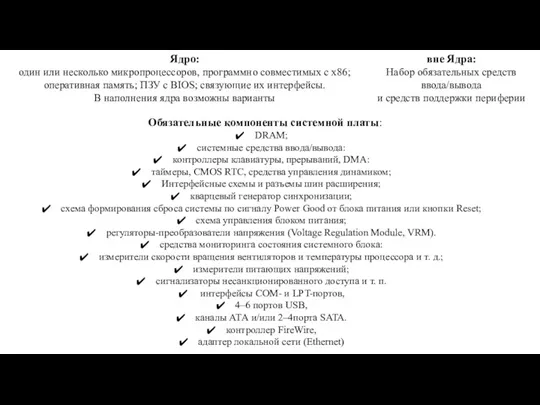

- 38. Ядро: один или несколько микропроцессоров, программно совместимых с х86; оперативная память; ПЗУ с BIOS; связующие их

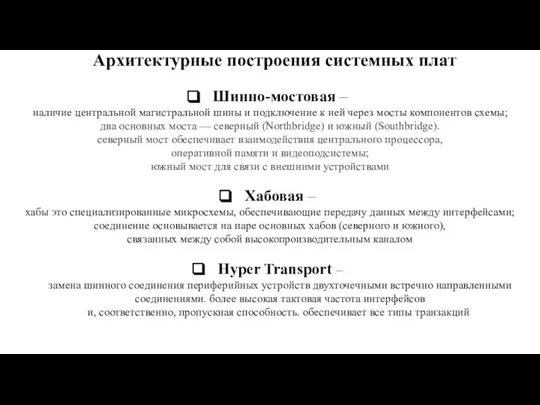

- 39. Архитектурные построения системных плат Шинно-мостовая – наличие центральной магистральной шины и подключение к ней через мосты

- 40. Шинно-мостовая архитектура

- 41. Хабовая архитектура

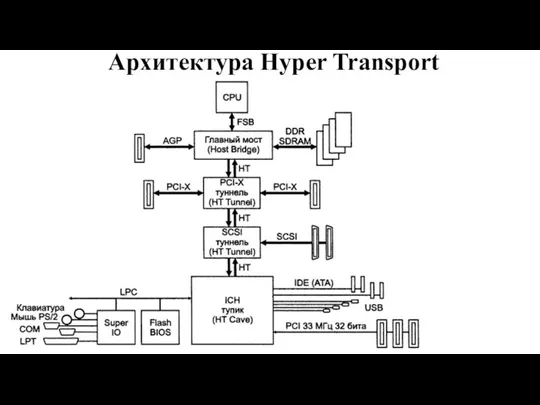

- 42. Архитектура Hyper Transport

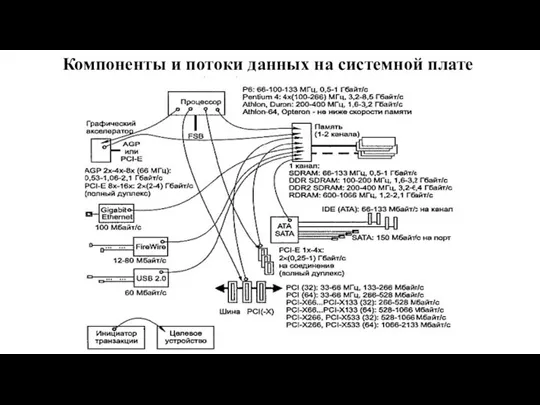

- 43. Компоненты и потоки данных на системной плате

- 44. Типы и характеристики интерфейсов Интерфейс – это аппаратное и программное обеспечение (элементы соединения и вспомогательные схемы

- 45. Архитектура системных интерфейсов Системный интерфейс выполняется в виде стандартизированных системных шин. Возможно внедрение сетевого взаимодействия в

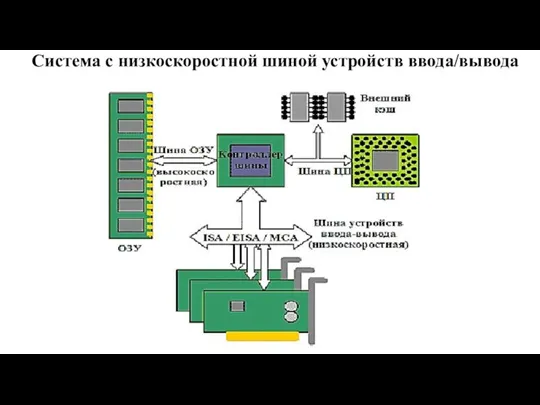

- 46. Система с низкоскоростной шиной устройств ввода/вывода

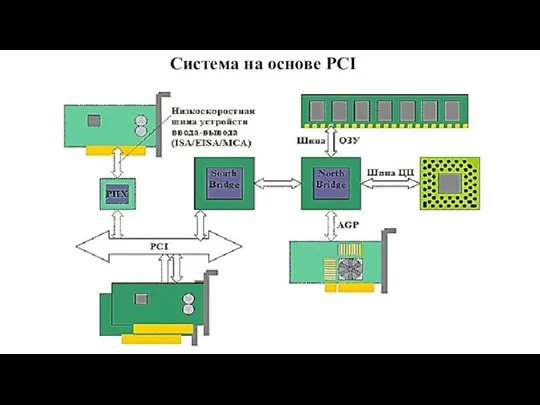

- 47. Система на основе PCI

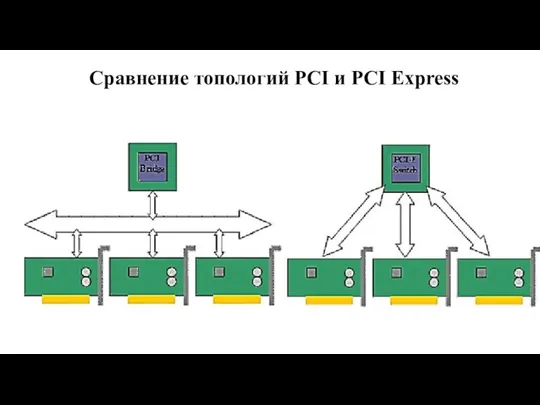

- 48. Сравнение топологий PCI и PCI Express

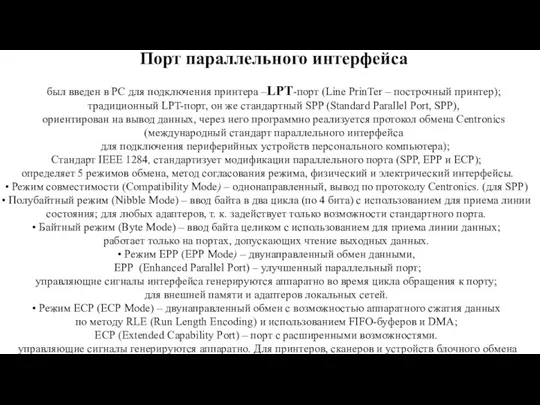

- 49. Порт параллельного интерфейса был введен в PC для подключения принтера –LPT-порт (Line PrinTer – построчный принтер);

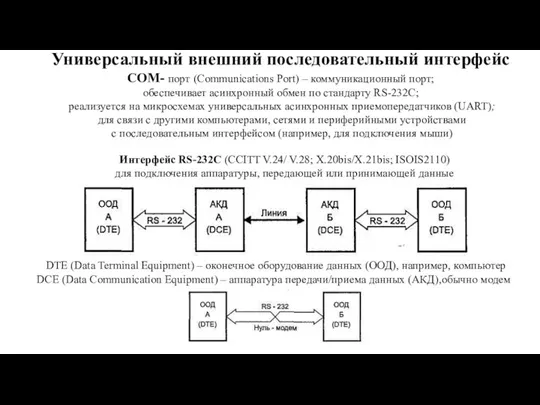

- 50. Универсальный внешний последовательный интерфейс СОМ- порт (Communications Port) – коммуникационный порт; обеспечивает асинхронный обмен по стандарту

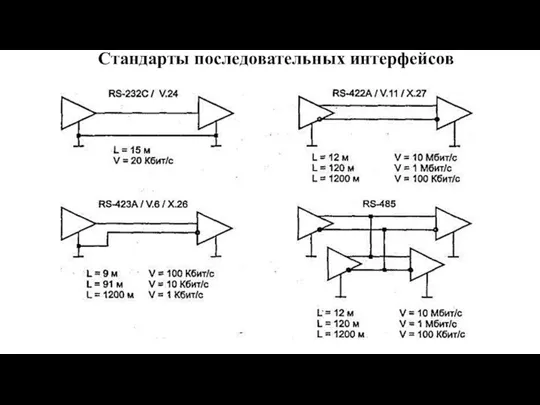

- 51. Стандарты последовательных интерфейсов

- 52. FireWire и USB последовательные соединения с возможностью коммутации при работающей системе большого количества периферийных устройств –

- 53. USB (Universal Serial Bus) – универсальная последовательная шина, промышленный стандарт расширения архитектуры PC кабель USB –

- 54. Транзакции с устройствами USB Поток (stream) однонаправленно доставляет данные от одного конца канала к другому, реализует

- 55. Интерфейсы локальных сетей организуются посредством сетевых адаптеров, или сетевых интерфейсных карт, Network Interface Card (NIC) Ethernet

- 56. Взаимодействие процессора с памятью Иерархическая организация памяти помогает компенсировать разницу в быстродействии процессоров и скорости доступа

- 57. Организация кэш-памяти (Cache memory) кэш для инструкций и данных может быть раздельный и общий в смешанной

- 58. Логическое распределение пространства оперативной и постоянной физической памяти . • 00000h-9FFFFh (640 Кбайт) – стандартная, или

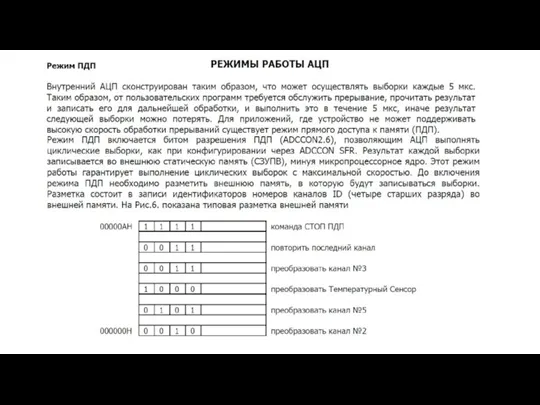

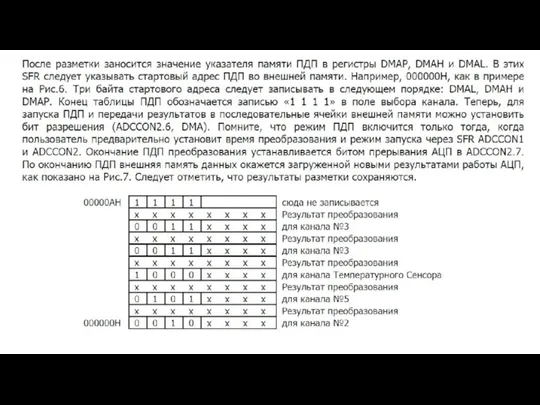

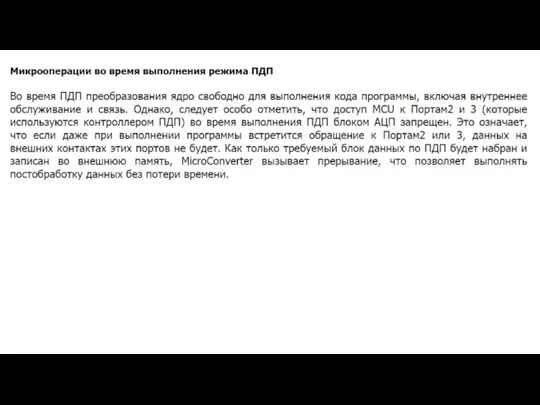

- 59. Режим прямого доступа к памяти (Direct Memory Access, DMA) пассивный доступ (Slave DMA) – устройство при

- 60. Внешняя память энергонезависимые устройства хранения данных, позволяющие сохранять информацию для последующего использования и реализующие различные физические

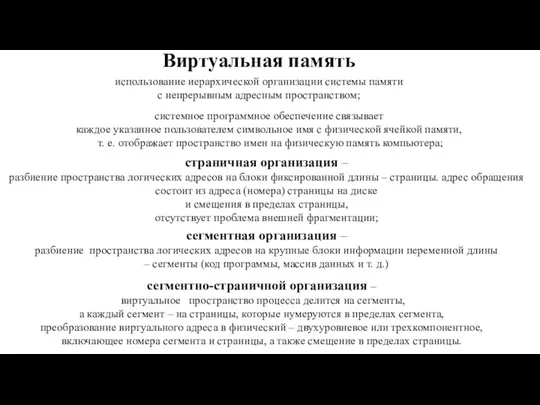

- 61. Виртуальная память использование иерархической организации системы памяти с непрерывным адресным пространством; системное программное обеспечение связывает каждое

- 62. ТИПЫ ПРЕРЫВАНИЙ внутренние прерывания – реакция на возникшие внутренние проблемные события; аппаратные прерывания – запрос посылает

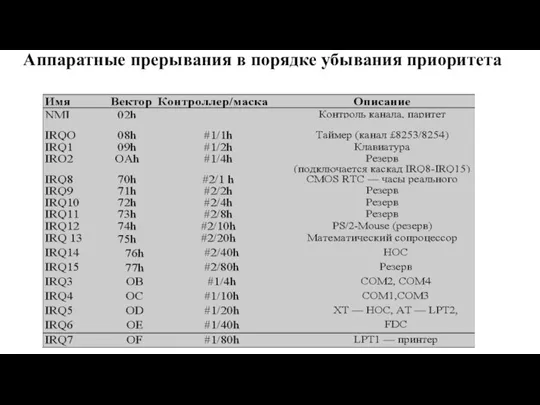

- 63. Аппаратные прерывания в порядке убывания приоритета

- 64. Коммутация запросов прерываний для реализаций системы прерываний процессоры Pentium и выше имеют встроенный контроллер прерываний APIC

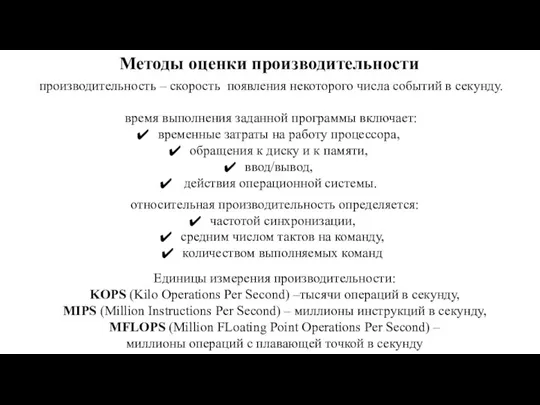

- 65. Методы оценки производительности производительность – скорость появления некоторого числа событий в секунду. время выполнения заданной программы

- 66. Что влияет на производительность Применение конвейерной обработки, когда несколько последовательных команд находятся на разных стадиях выполнения,

- 67. Для оценки и сравнения систем используются следующие критерии: • Пиковая производительность – теоретический максимум быстродействия компьютера

- 68. Тестовая оценка производительности Тесты производителей – предназначены для оценки выпускаемых процессоров, ориентированы на сравнение ограниченного множества

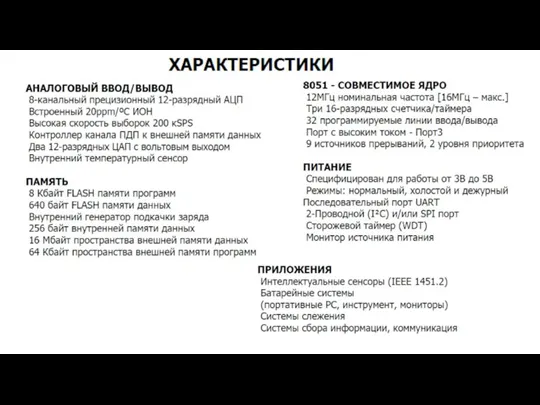

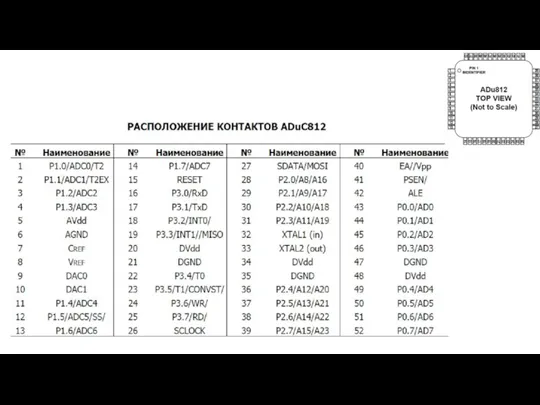

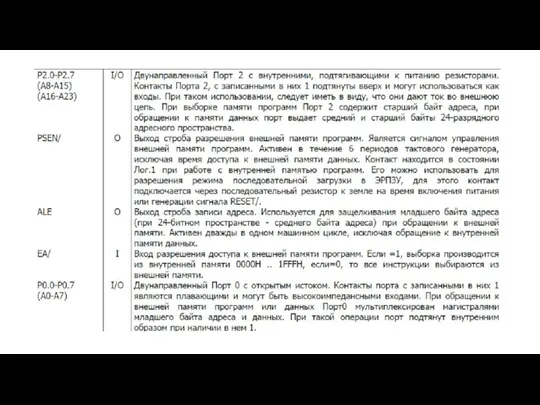

- 69. ОДНОКРИСТАЛЬНЫЕ МИКРОКОНТРОЛЛЕРЫ

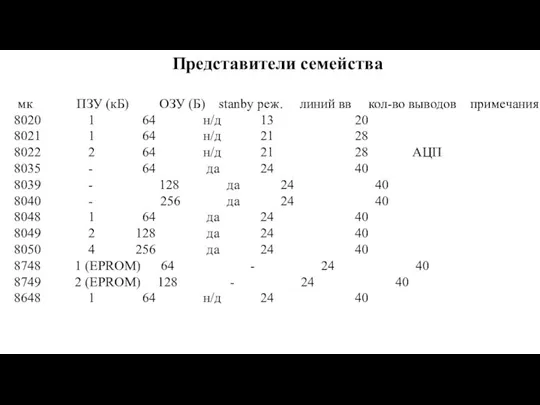

- 70. Представители семейства мк ПЗУ (кБ) ОЗУ (Б) stanby реж. линий вв кол-во выводов примечания 8020 1

- 71. Универсальный периферийный интерфейс (UPI) Обозначение Встроенное ПЗУ (кВ) Встроенное ОЗУ (B) Примечания 8041 1 64 8041AH

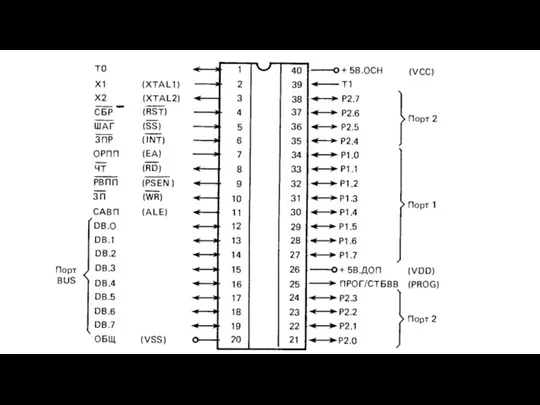

- 73. Схемы синхронизации Начальная установка

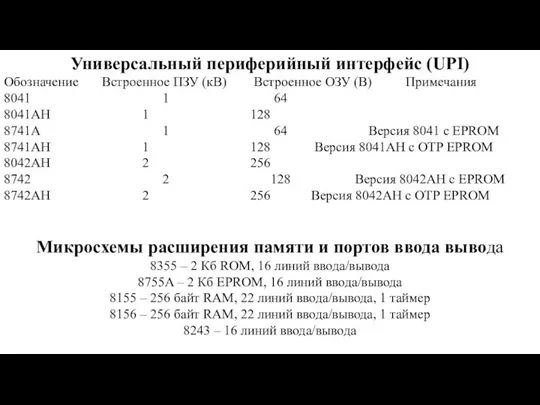

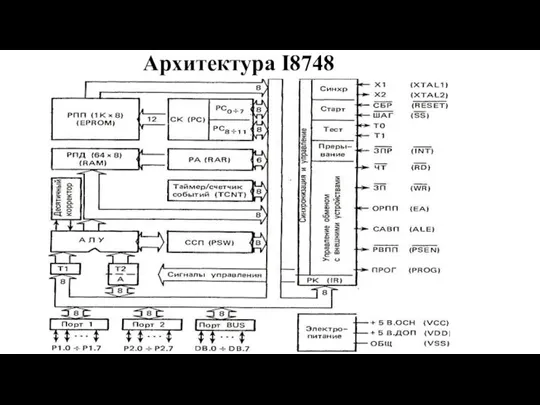

- 74. Архитектура I8748

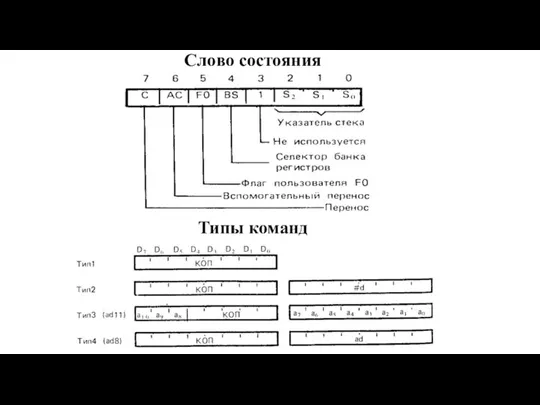

- 75. Слово состояния Типы команд

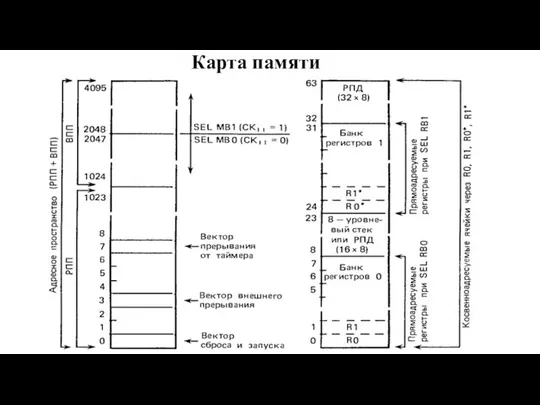

- 76. Карта памяти

- 77. Подключение внешней памяти программ

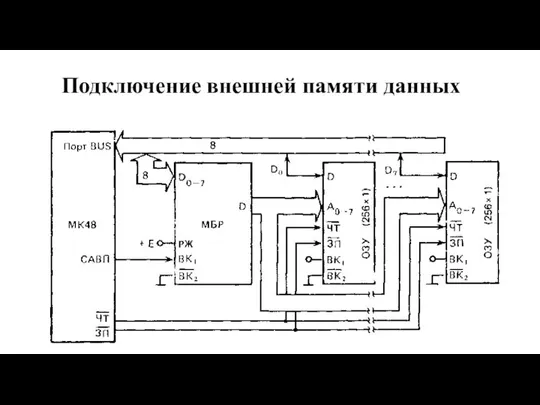

- 78. Подключение внешней памяти данных

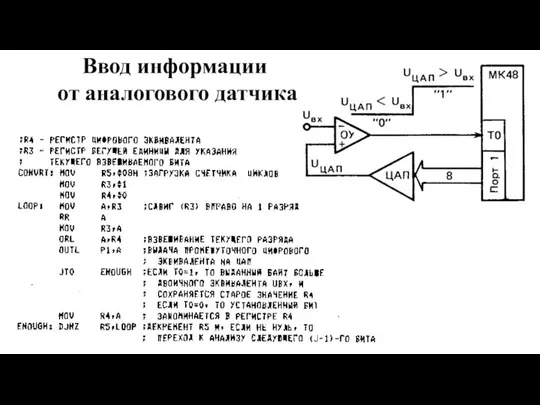

- 79. Ввод информации от аналогового датчика

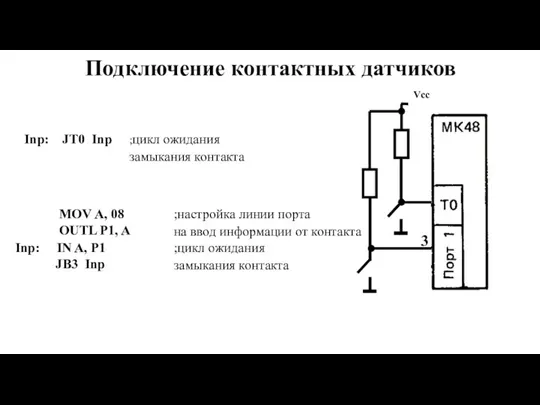

- 80. 3 Vcc Подключение контактных датчиков

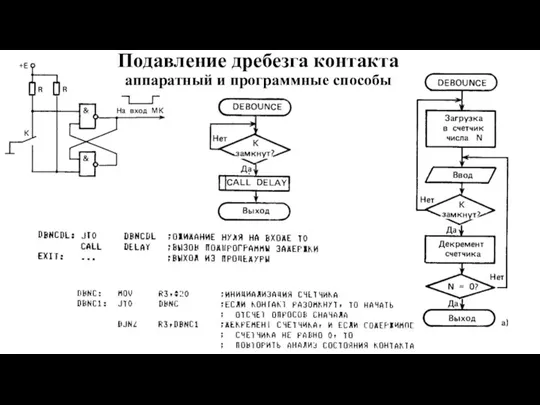

- 81. Подавление дребезга контакта аппаратный и программные способы

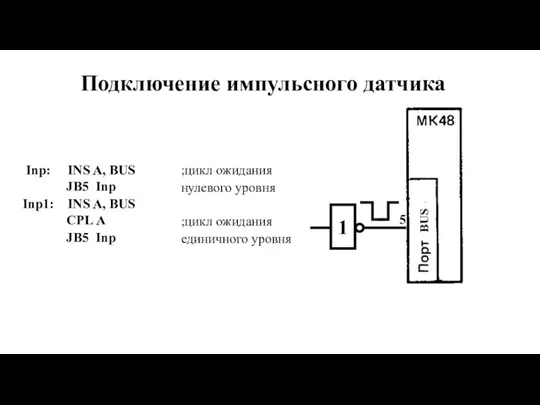

- 82. 5 Подключение импульсного датчика 1

- 83. Подключение клавиатуры

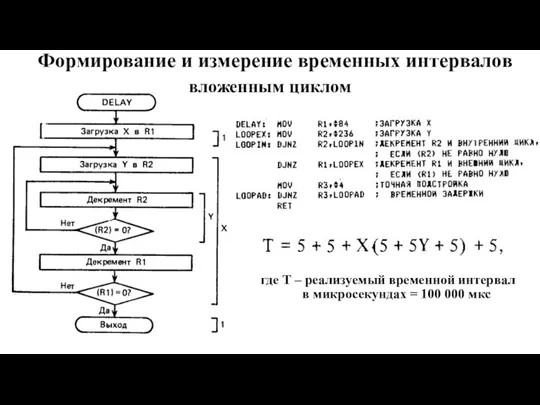

- 84. Формирование и измерение временных интервалов вложенным циклом где Т – реализуемый временной интервал в микросекундах =

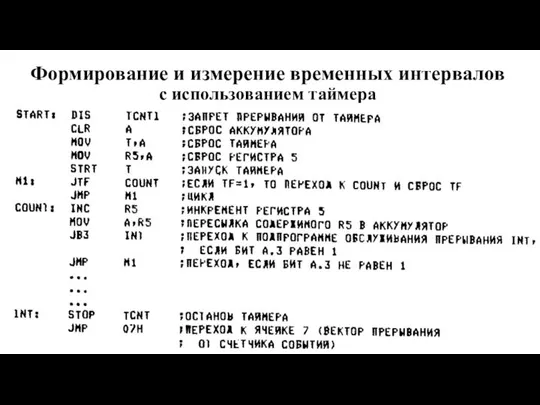

- 85. Формирование и измерение временных интервалов с использованием таймера

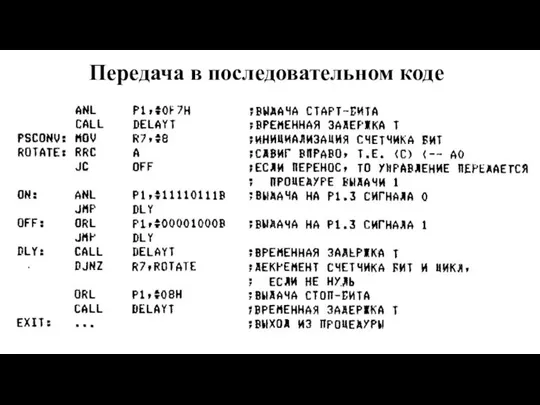

- 86. Передача в последовательном коде

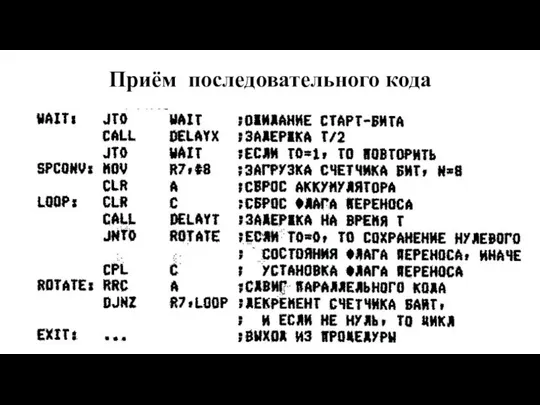

- 87. Приём последовательного кода

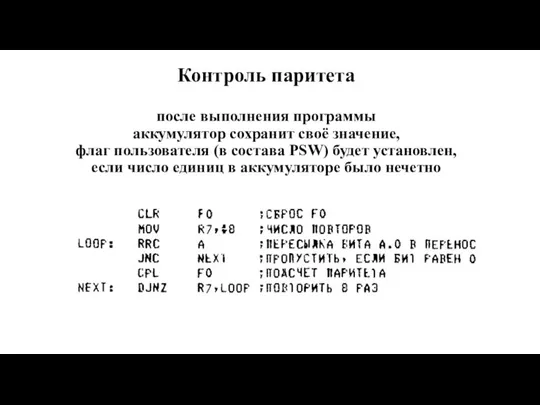

- 88. Контроль паритета после выполнения программы аккумулятор сохранит своё значение, флаг пользователя (в состава PSW) будет установлен,

- 89. MCS 51

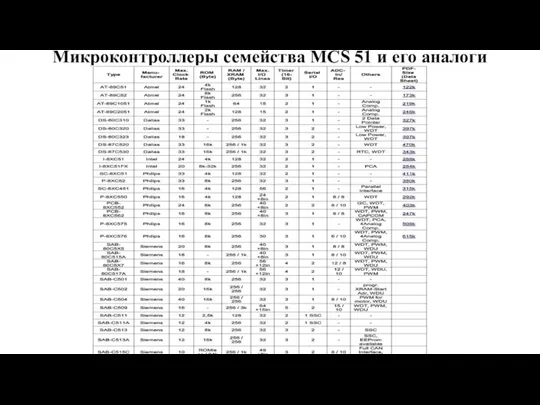

- 90. Микроконтроллеры семейства MCS 51 и его аналоги

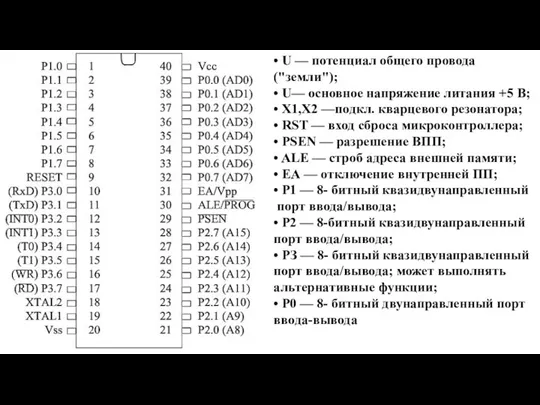

- 91. • U — потенциал общего провода ("земли"); • U— основное напряжение литания +5 В; • X1,X2

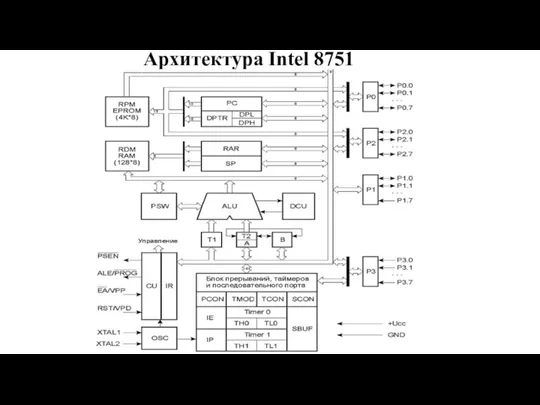

- 92. Архитектура Intel 8751

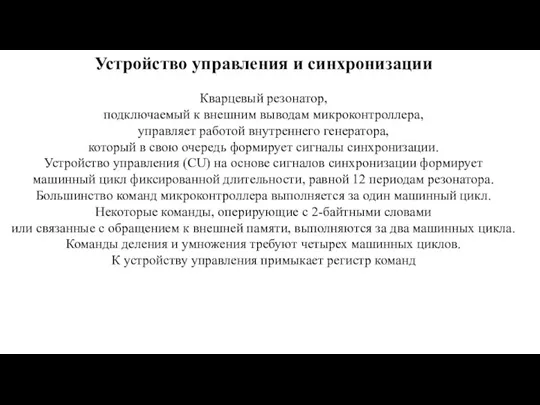

- 93. Устройство управления и синхронизации Кварцевый резонатор, подключаемый к внешним выводам микроконтроллера, управляет работой внутреннего генератора, который

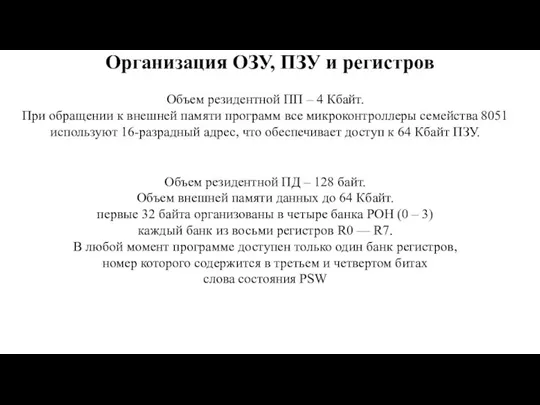

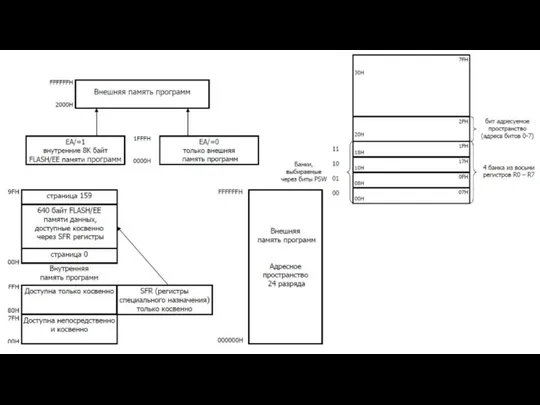

- 94. Организация ОЗУ, ПЗУ и регистров Объем резидентной ПП – 4 Кбайт. При обращении к внешней памяти

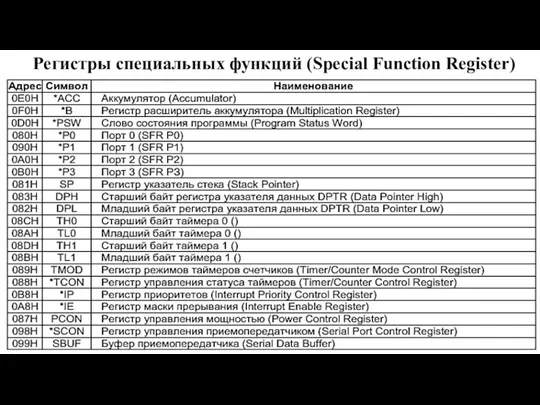

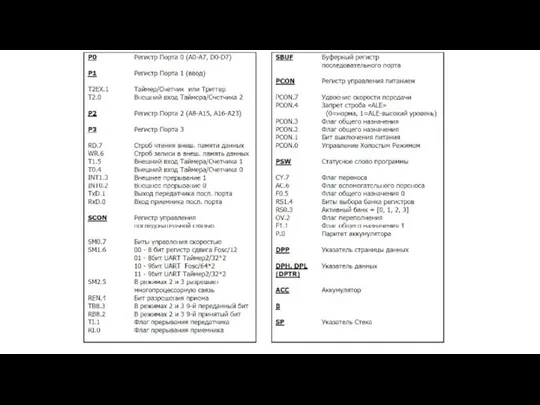

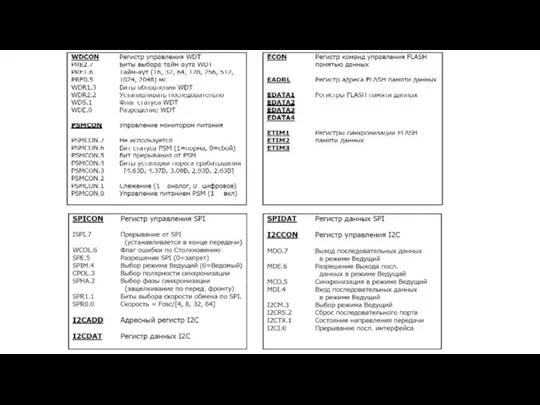

- 95. Регистры специальных функций (Special Function Register)

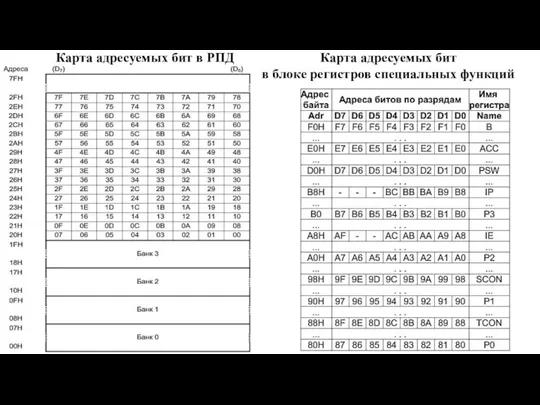

- 96. Карта адресуемых бит в блоке регистров специальных функций Карта адресуемых бит в РПД

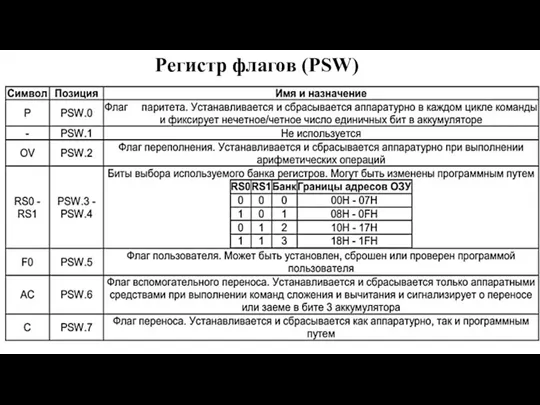

- 97. Регистр флагов (PSW)

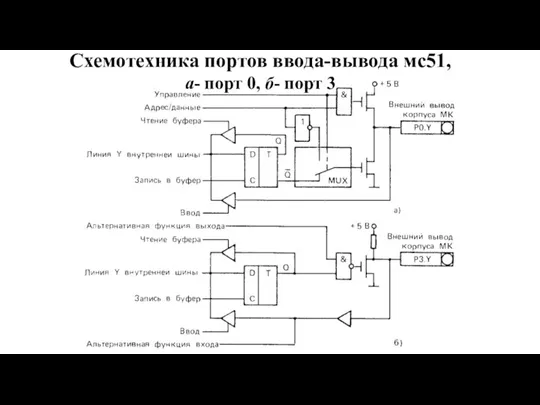

- 98. Схемотехника портов ввода-вывода мс51, а- порт 0, б- порт 3

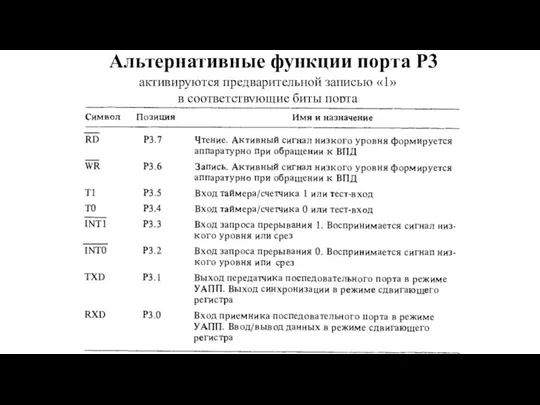

- 99. Альтернативные функции порта Р3 активируются предварительной записью «1» в соответствующие биты порта

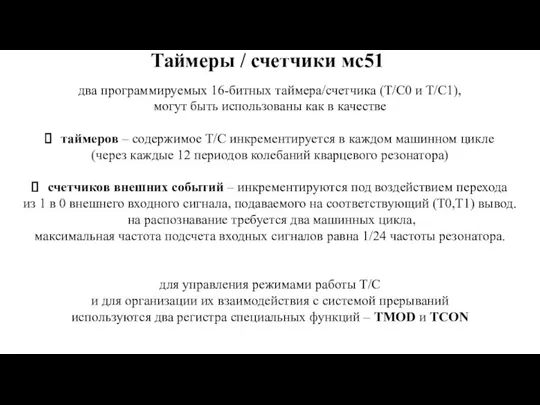

- 100. Таймеры / счетчики мс51 два программируемых 16-битных таймера/счетчика (T/C0 и T/C1), могут быть использованы как в

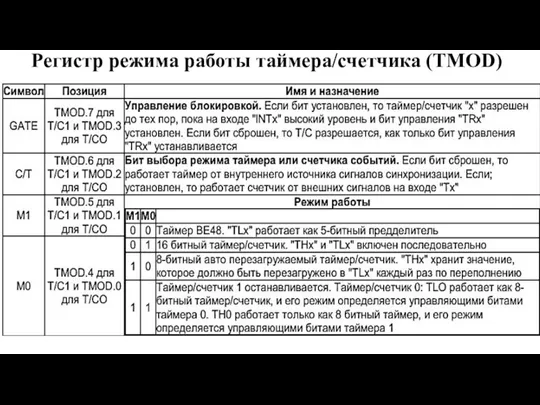

- 101. Регистр режима работы таймера/счетчика (TMOD)

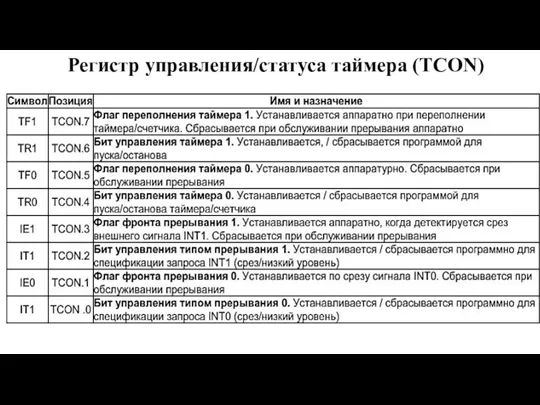

- 102. Регистр управления/статуса таймера (TCON)

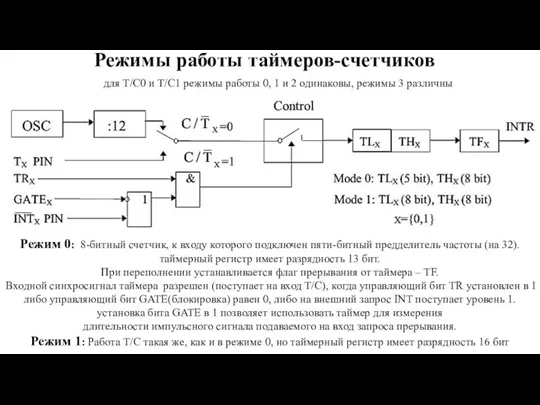

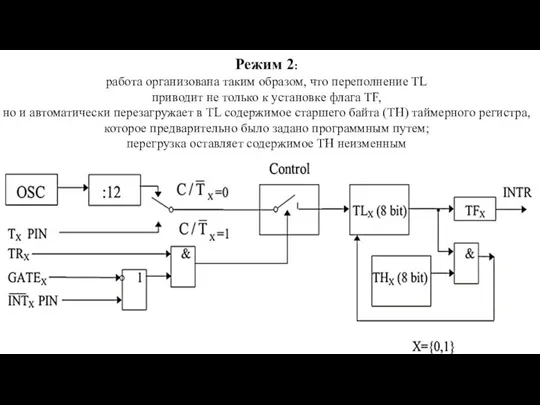

- 103. Режимы работы таймеров-счетчиков для Т/С0 и Т/С1 режимы работы 0, 1 и 2 одинаковы, режимы 3

- 104. Режим 2: работа организована таким образом, что переполнение TL приводит не только к установке флага TF,

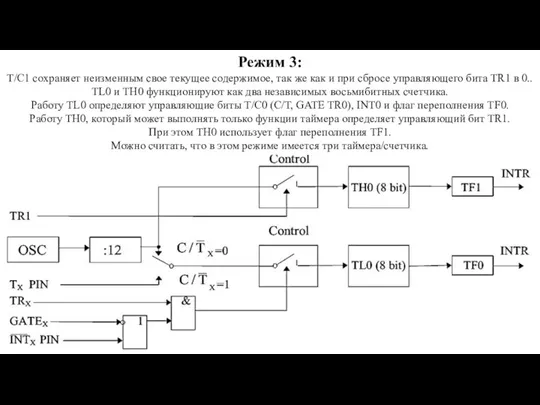

- 105. Режим 3: Т/С1 сохраняет неизменным свое текущее содержимое, так же как и при сбросе управляющего бита

- 106. Универсальный асинхронный приемопередатчик UART (Universal Asynchronous ReceiverTransmitter) прием и передача информации в последовательном коде младшими битами

- 107. Режимы работы УАПП Режим 0. Информация и передается, и принимается через вывод входа приемника (RхD). Принимаются

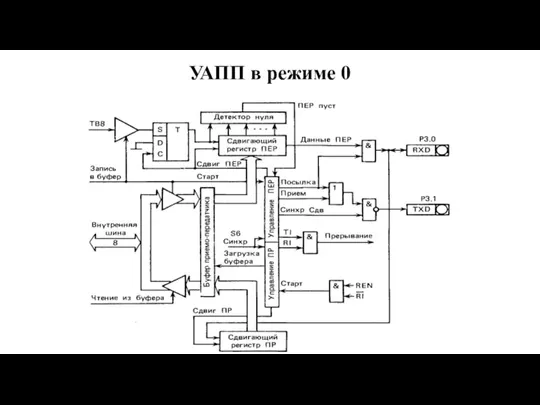

- 108. УАПП в режиме 0

- 109. УАПП в режимах 1, 2, 3

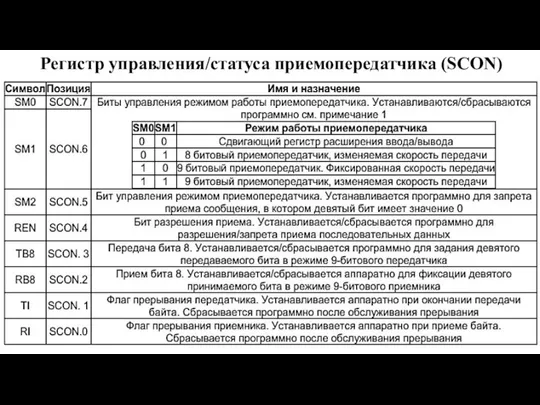

- 110. Регистр управления/статуса приемопередатчика (SCON)

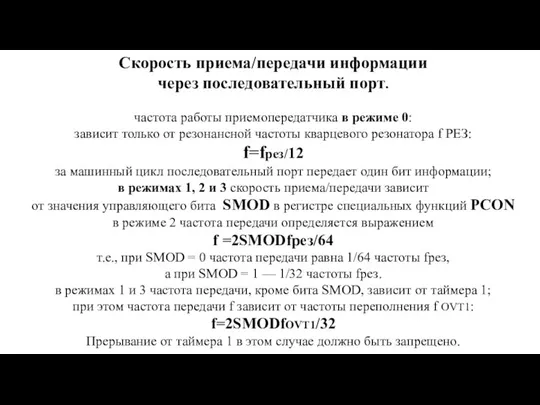

- 111. Скорость приема/передачи информации через последовательный порт. частота работы приемопередатчика в режиме 0: зависит только от резонансной

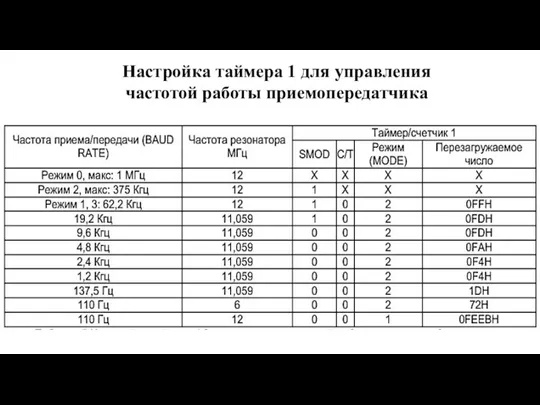

- 112. Настройка таймера 1 для управления частотой работы приемопередатчика

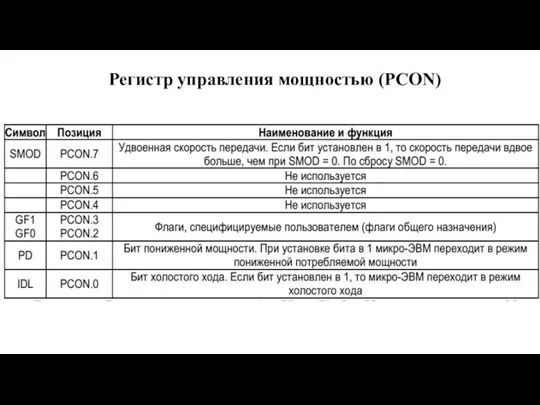

- 113. Регистр управления мощностью (PCON)

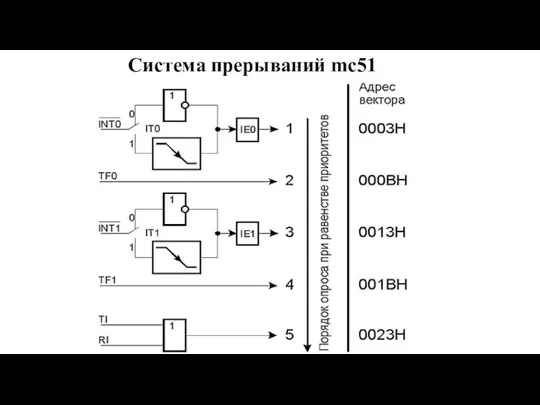

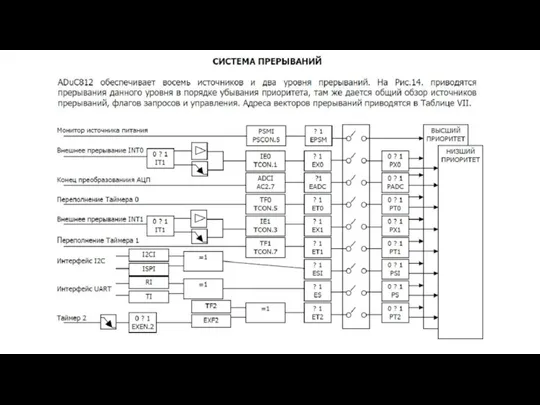

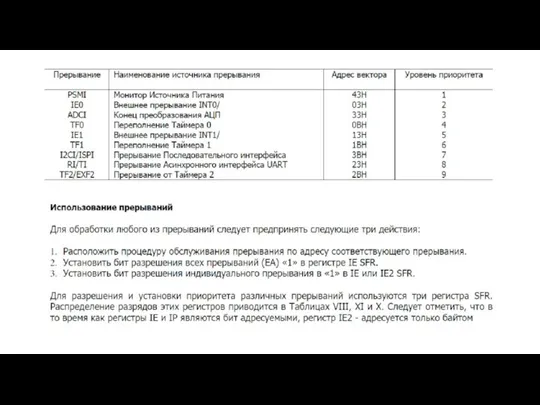

- 114. Система прерываний mc51

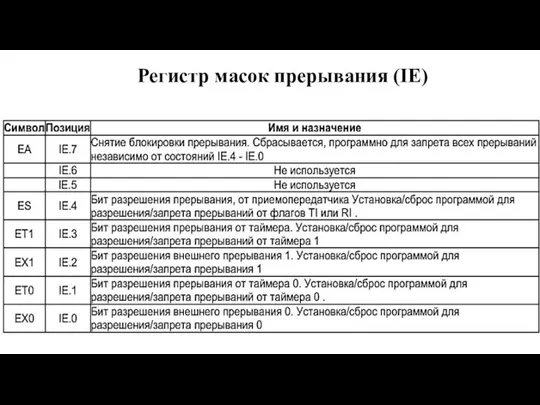

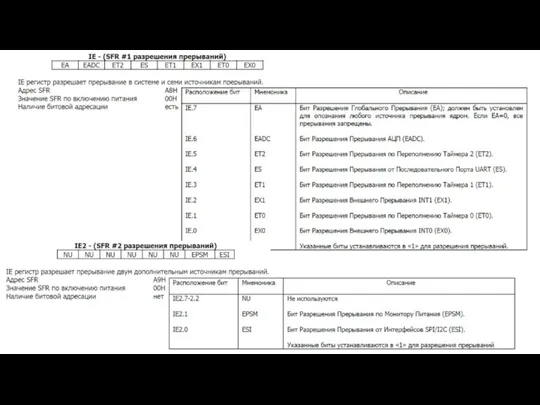

- 115. Регистр масок прерывания (IE)

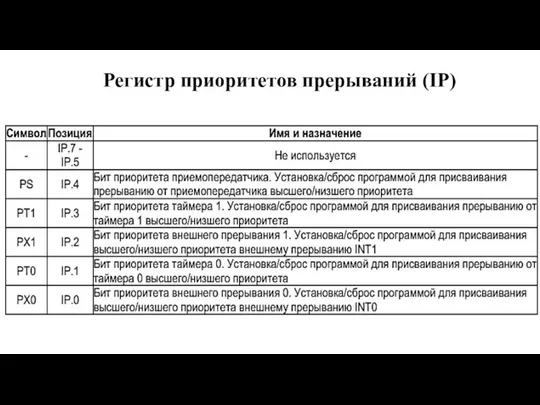

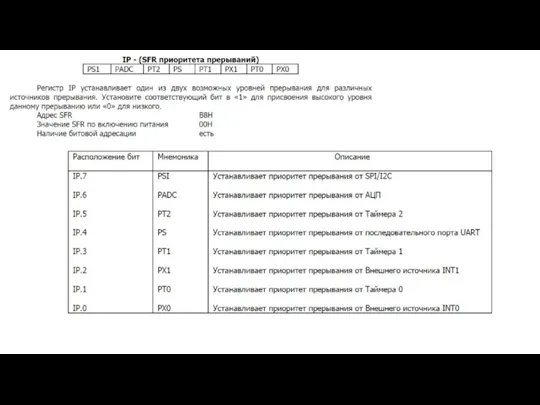

- 116. Регистр приоритетов прерываний (IP)

- 117. Система команд mс51 111 базовых команд, по функциональному признаку подразделяются на группы команд: пересылки данных; арифметических

- 118. Режимы адресации Прямая адресация (Direct Addressing) операнд определяется 8-битным адресом в инструкции, используется только для внутренней

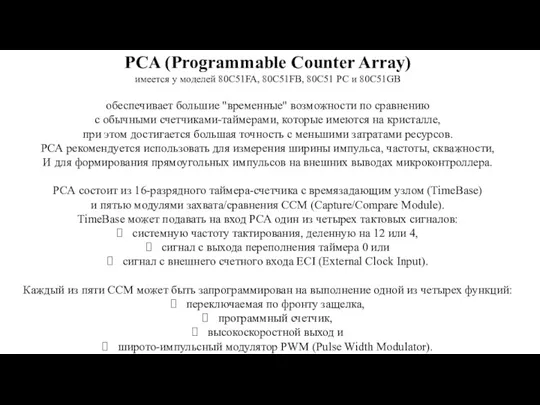

- 120. PCA (Programmable Counter Array) имеется у моделей 80C51FA, 80C51FB, 80С51 РС и 80C51GB обеспечивает большие "временные"

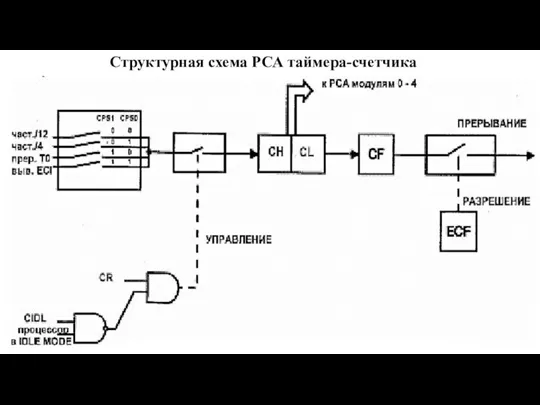

- 122. Структурная схема РСА таймера-счетчика

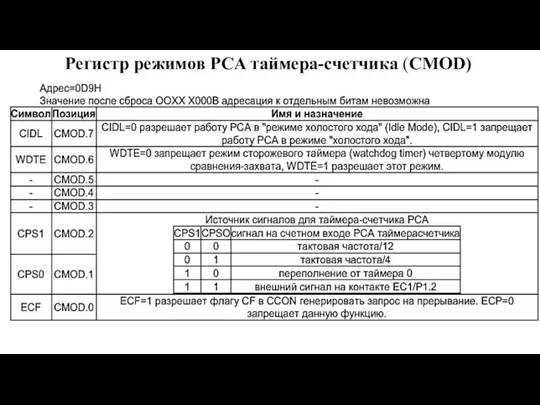

- 123. Регистр режимов PCA таймера-счетчика (CMOD)

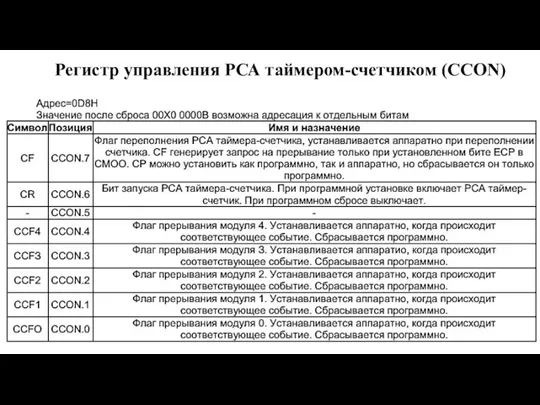

- 124. Регистр управления РСА таймером-счетчиком (CCON)

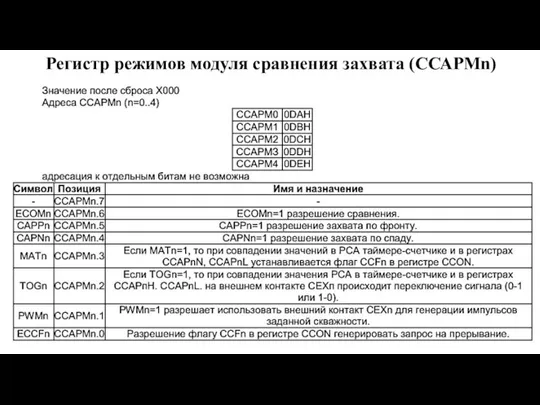

- 125. Регистр режимов модуля сравнения захвата (ССАРМn)

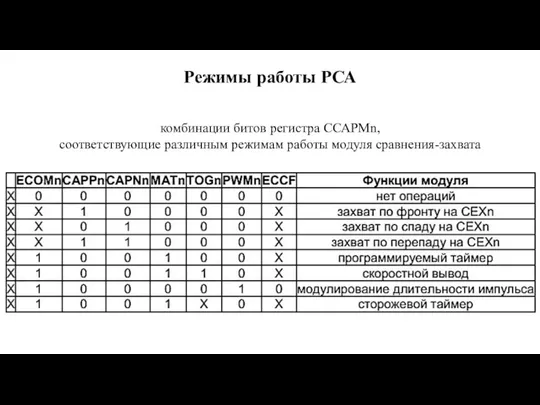

- 126. Режимы работы РСА комбинации битов регистра ССАРМn, соответствующие различным режимам работы модуля сравнения-захвата

- 127. Режим захвата рекомендуется использовать при измерении периодов, длительности, скважности импульсов, разности фаз между различными входами; Установка

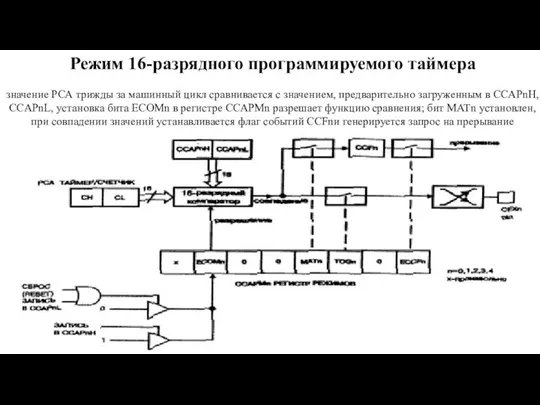

- 128. Режим 16-разрядного программируемого таймера значение РСА трижды за машинный цикл сравнивается с значением, предварительно загруженным в

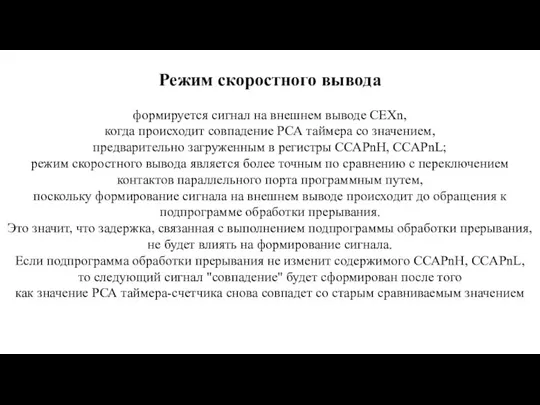

- 129. Режим скоростного вывода формируется сигнал на внешнем выводе СЕХn, когда происходит совпадение РСА таймера со значением,

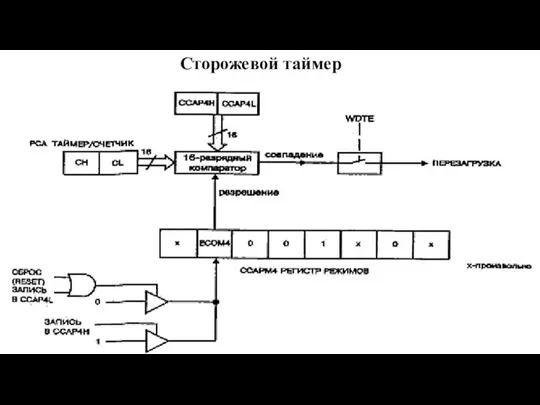

- 130. Режим сторожевого таймера (watchdog timer) Сторожевой таймер - это схема, которая автоматически сбрасывает микроконтроллер, если не

- 131. Сторожевой таймер

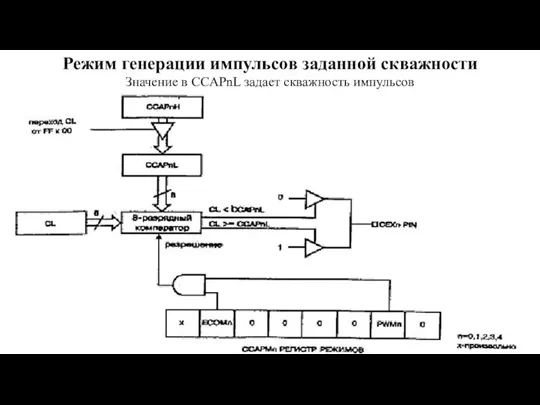

- 132. Режим генерации импульсов заданной скважности Значение в CCAPnL задает скважность импульсов

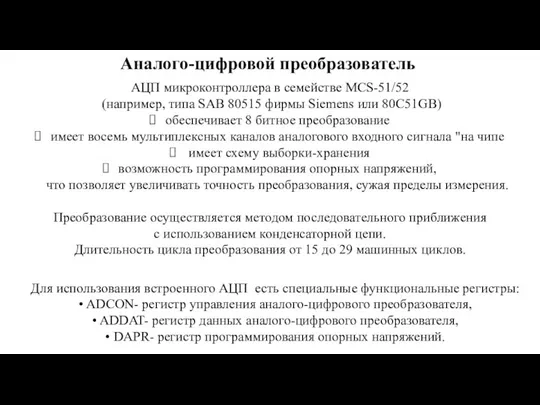

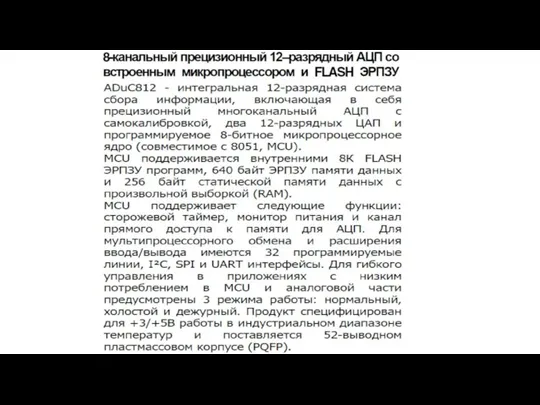

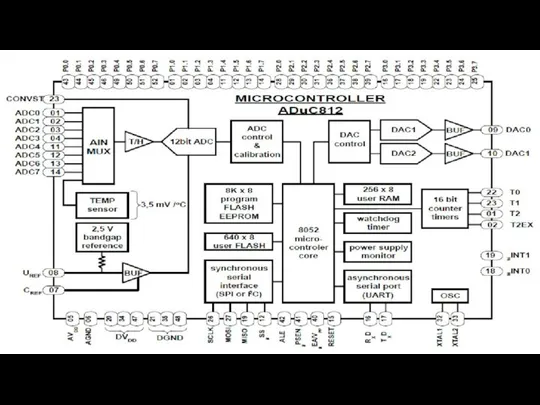

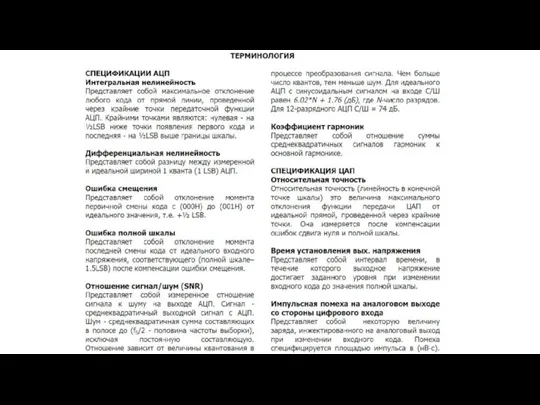

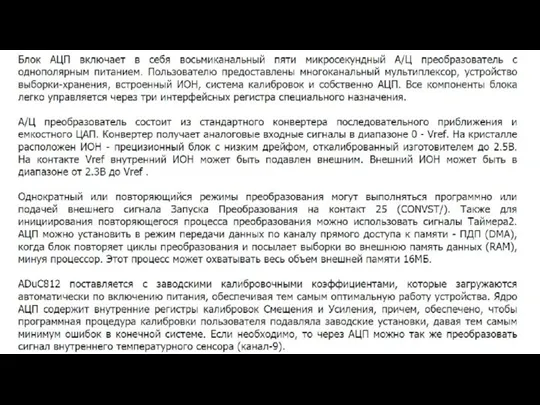

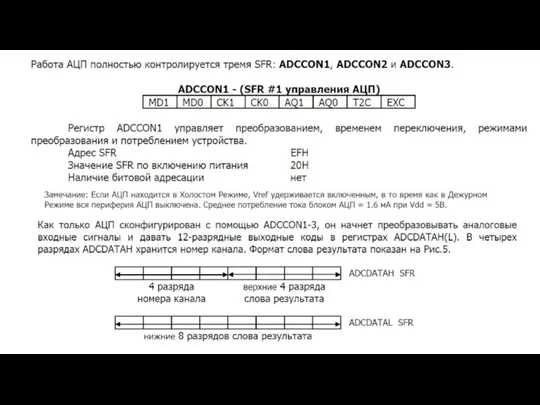

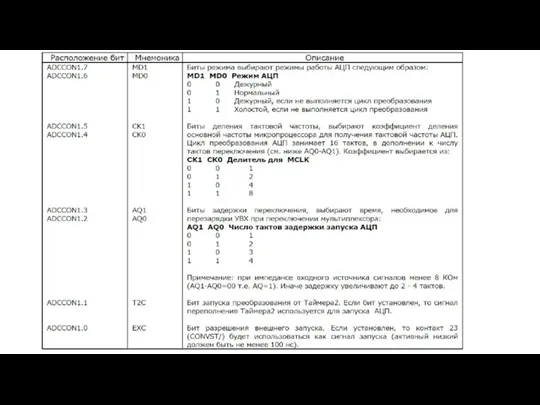

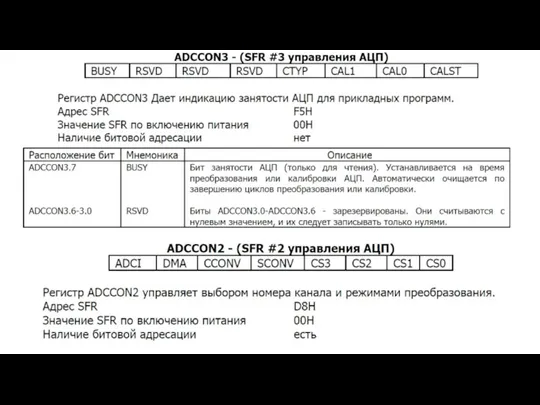

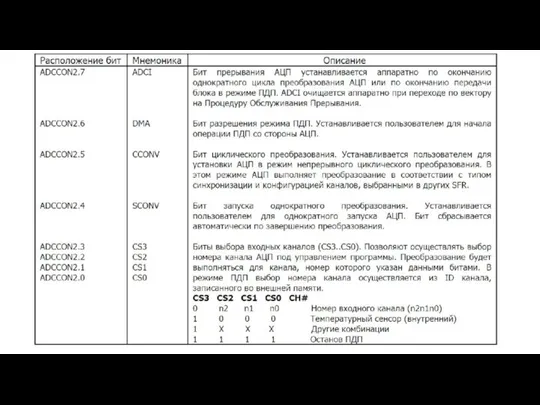

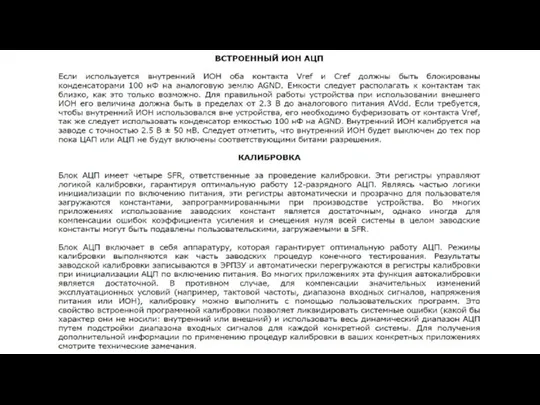

- 133. Аналого-цифровой преобразователь АЦП микроконтроллера в семействе MCS-51/52 (например, типа SAB 80515 фирмы Siemens или 80C51GB) обеспечивает

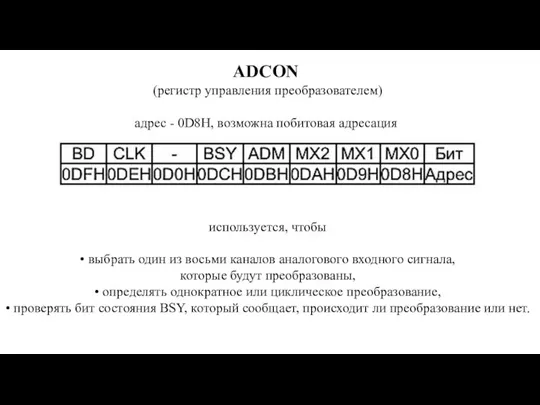

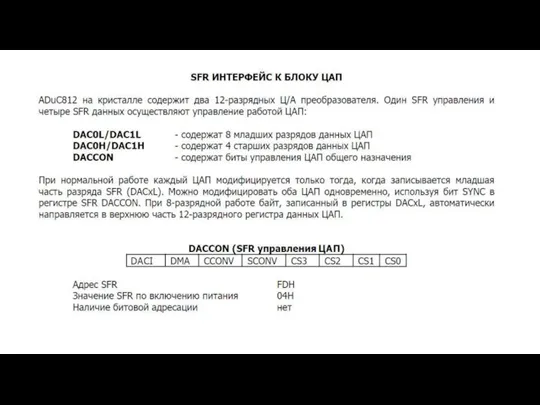

- 134. ADCON (регистр управления преобразователем) адрес - 0D8H, возможна побитовая адресация используется, чтобы • выбрать один из

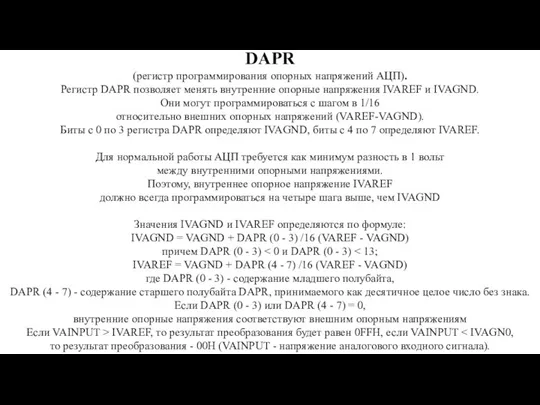

- 136. DAPR (регистр программирования опорных напряжений АЦП). Регистр DAPR позволяет менять внутренние опорные напряжения IVAREF и IVAGND.

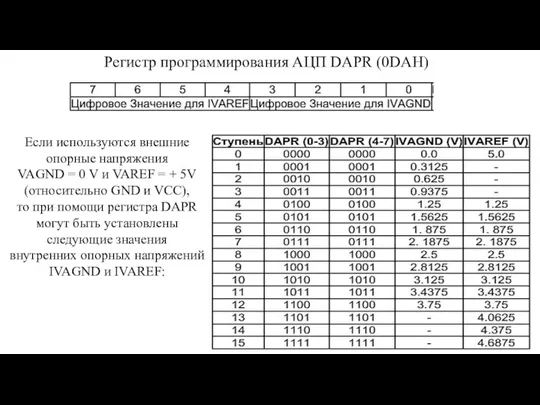

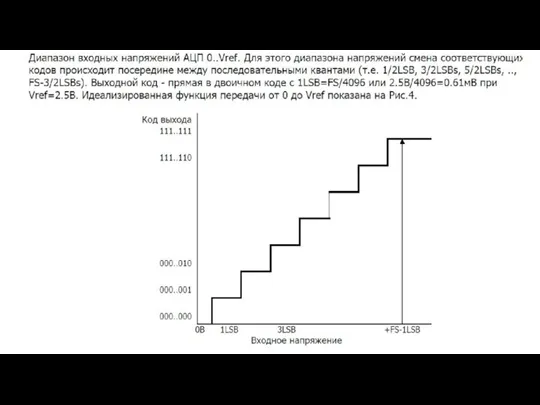

- 137. Регистр программирования АЦП DAPR (0DAH) Если используются внешние опорные напряжения VAGND = 0 V и VAREF

- 182. Скачать презентацию

3 декабря Международный день инвалидов

3 декабря Международный день инвалидов Museo Enrique Urcola

Museo Enrique Urcola Буратино

Буратино Съедобные грибы

Съедобные грибы Презентация на тему Лилейные и злаковые растения

Презентация на тему Лилейные и злаковые растения  Учебники маминой юности и моей жизни

Учебники маминой юности и моей жизни Этикет в деловом диалоге по телефону

Этикет в деловом диалоге по телефону Презентация на тему Трансформаторы 11 класс

Презентация на тему Трансформаторы 11 класс Инвестиционный Проект Строительство малого города - спутника города Калуга с использованием современных технологий и возможност

Инвестиционный Проект Строительство малого города - спутника города Калуга с использованием современных технологий и возможност Костры. Виды костров

Костры. Виды костров Психологія вимушених переселенців

Психологія вимушених переселенців Скалярное произведение векторов. Решение задач на вычисление скалярного произведения векторов

Скалярное произведение векторов. Решение задач на вычисление скалярного произведения векторов СЕМЕЙНОЕ ЖИЗНЕУСТРОЙСТВО ВОСПИТАННИКОВ ПАТРОНАТ ДО СОВЕРШЕННОЛЕТИЯ ВОСПИТАННИКА (7 СЕМЕЙ) ПАТРОНАТ ДО СОВЕРШЕННОЛЕТИЯ ВОСПИТАНН

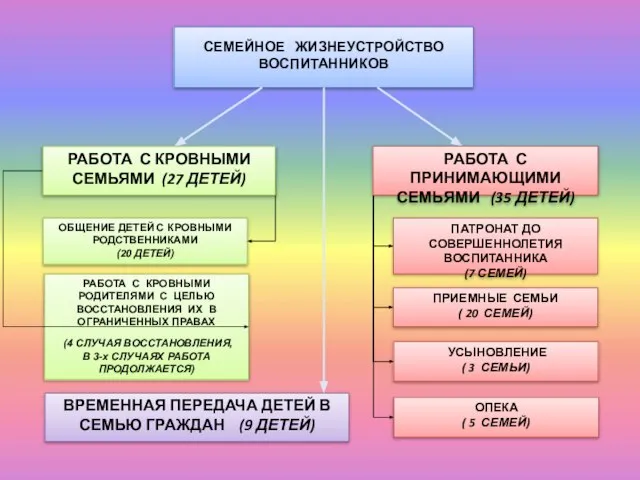

СЕМЕЙНОЕ ЖИЗНЕУСТРОЙСТВО ВОСПИТАННИКОВ ПАТРОНАТ ДО СОВЕРШЕННОЛЕТИЯ ВОСПИТАННИКА (7 СЕМЕЙ) ПАТРОНАТ ДО СОВЕРШЕННОЛЕТИЯ ВОСПИТАНН НАШИ ПЕРНАТЫЕ ДРУЗЬЯ

НАШИ ПЕРНАТЫЕ ДРУЗЬЯ Комплексная автоматизация производственного процесса на примере внутрицеховой логистики.

Комплексная автоматизация производственного процесса на примере внутрицеховой логистики. Урок развития речи на основе ознакомления с предметами и явлениями окружающей действительности

Урок развития речи на основе ознакомления с предметами и явлениями окружающей действительности ГОУ ВПО «АСТРАХАНСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ»

ГОУ ВПО «АСТРАХАНСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ» Презентация на тему Проблема урбанизации

Презентация на тему Проблема урбанизации Мы рады представить Вам нашу рекламную площадку

Мы рады представить Вам нашу рекламную площадку ПЕРВЫЕ ХУДОЖНИКИ ЗЕМЛИ

ПЕРВЫЕ ХУДОЖНИКИ ЗЕМЛИ Традиционные общества в XIX – начале XX века

Традиционные общества в XIX – начале XX века Права ребёнка

Права ребёнка Заработная плата. НДФЛ

Заработная плата. НДФЛ Театральные профессии

Театральные профессии ГАРМОНИЗАЦИЯ ДЕТСКО-РОДИТЕЛЬСКИХ ОТНОШЕНИЙ

ГАРМОНИЗАЦИЯ ДЕТСКО-РОДИТЕЛЬСКИХ ОТНОШЕНИЙ Страхование гражданской ответственности

Страхование гражданской ответственности Каникулы tab team таиланд | 2022 начните в октябре! (Баннер)

Каникулы tab team таиланд | 2022 начните в октябре! (Баннер) Правовые основы брака и семьи

Правовые основы брака и семьи