Содержание

- 2. Introduction to Digital Systems. Combinational Circuits. Digital Integrated Circuits. Lecture 1 Dana Utebayeva

- 3. Outline Basic concepts Simple gates Completeness Logic functions Expressing logic functions Equivalence Boolean algebra Boolean identities

- 4. Introduction Hardware consists of a few simple building blocks These are called logic gates AND, OR,

- 5. Basic Concepts Simple gates AND OR NOT Functionality can be expressed by a truth table A

- 6. Basic Concepts (cont’d) Additional useful gates NAND NOR XOR NAND = AND + NOT NOR =

- 7. Basic Concepts (cont’d) Number of functions With N logical variables, we can define 22N functions Some

- 8. Basic Concepts (cont’d) Complete sets A set of gates is complete if we can implement any

- 9. Basic Concepts (cont’d) Proving NAND gate is universal

- 10. Basic Concepts (cont’d) Proving NOR gate is universal

- 11. Logic Chips Basic building block: Transistor Three connection points Base Emitter Collector Transistor can operate Linear

- 12. Logic Chips (cont’d) NOT NAND NOR

- 13. Logic Chips (cont’d) Low voltage level: High voltage level: > 2.4V Positive logic: Low voltage represents

- 14. Logic Chips (cont’d)

- 15. Logic Chips (cont’d) Integration levels SSI (small scale integration) Introduced in late 1960s 1-10 gates (previous

- 16. Logic Functions Logical functions can be expressed in several ways: Truth table Logical expressions Graphical form

- 17. Logic Functions (cont’d) 3-input majority function A B C F 0 0 0 0 0 0

- 18. Logical Equivalence All three circuits implement F = A B function

- 19. Logical Equivalence (cont’d) Proving logical equivalence of two circuits Derive the logical expression for the output

- 20. Logical Equivalence (cont’d) Derivation of logical expression from a circuit Trace from the input to output

- 21. Logical Equivalence (cont’d) Proving logical equivalence: Truth table method A B F1 = A B F3

- 22. Thanks for your attention

- 23. LECTURE 2

- 24. FUNDAMENTALS OF LOGICAL DESIGN SIS 2 “Binary systems” [email protected] Dana Utebayeva

- 25. DECIMAL TO BINARY CONVERSION Convert Decimal Number to a Binary Number: Decimal Binary 1110011100000 7392

- 26. QUIZ for SIS Project 1 Conversion of Decimal Number to a Binary Number: Dana Zh. Utebayeva:

- 27. FUNDAMENTALS OF LOGICAL DESIGN Lecture 2 “Number systems and Codes” [email protected] Dana Utebayeva

- 28. Goal of the lecture is to be familiar with number systems and code in digital electronics.

- 29. Outline of Lecture Counting in Decimal and Binary Place Value Binary to Decimal Conversion Decimal to

- 30. Number systems Radix and subscript

- 31. COUNTING IN DECIMAL AND BINARY Number System - Code using symbols that refer to a number

- 32. Generalized approach of Number systems A number with a decimal point is represented by series of

- 33. PLACE VALUE Numeric value of symbols in different positions. Example - Place value in binary system:

- 34. BINARY TO DECIMAL CONVERSION Convert Binary Number 110011 to a Decimal Number: 32 + 16 +

- 35. TEST Convert the following binary numbers into decimal numbers: Binary 1001 = 9 Binary 1111 =

- 36. DECIMAL TO BINARY CONVERSION Divide by 2 Process Decimal # 13 ÷ 2 = 6 remainder

- 37. TEST Convert the following decimal numbers into binary: Decimal 11 = Decimal 4 = Decimal 17

- 38. ELECTRONIC TRANSLATORS Devices that convert from decimal to binary numbers and from binary to decimal numbers.

- 39. ELECTRONIC ENCODER - DECIMAL TO BINARY 0 Decimal to Binary Encoder Binary output Decimal input 0

- 40. Binary-to- 7-Segment Decoder/ Driver ELECTRONIC DECODING: BINARY TO DECIMAL Binary input 0 0 0 0 Decimal

- 41. Uses 16 symbols -Base 16 System 0-9, A, B, C, D, E, F Decimal 1 9

- 42. Hexadecimal to Binary Conversion Hexadecimal C 3 Binary 1100 0011 Binary 1110 1010 Hexadecimal E A

- 43. DECIMAL TO HEXADECIMAL CONVERSION Divide by 16 Process Decimal # 47 ÷ 16 = 2 remainder

- 44. HEXADECIMAL TO DECIMAL CONVERSION Convert hexadecimal number 2DB to a decimal number 512 + 208 +

- 45. TEST Convert Hexadecimal number A6 to Binary Convert Hexadecimal number 16 to Decimal Convert Decimal 63

- 46. OCTAL NUMBERS Uses 8 symbols -Base 8 System 0, 1, 2, 3, 4, 5, 6, 7

- 47. PRACTICAL SUGGESTION ON NUMBER SYSTEM CONVERSIONS Use a scientific calculator Most scientific calculators have DEC, BIN,

- 48. 1) first page (Names, Title: “Binary systems”) 2) Outline (План) 3) Part I: (images from your

- 49. Attendance for Lecture 2 Dana Zh. Utebayeva: https://docs.google.com/forms/d/e/1FAIpQLSfotGeOUvqjykd78SYCT_WEU… опубликовано в 13507 Fundamentals of Logic Design (Утебаева

- 50. LECTURE 3-4

- 51. Outline Binary numbers Logic States Implementation The Buffer Logic Gate using n-p-n transistors Logic Gates using

- 52. POS – product of sums

- 53. Logic Gates Simple gates AND OR NOT Functionality can be expressed by a truth table A

- 54. Basic Concepts (cont’d) Additional useful gates NAND NOR XOR NAND = AND + NOT NOR =

- 55. Basic Concepts (cont’d) Number of functions With N logical variables, we can define 22N functions Some

- 56. Basic Concepts (cont’d) Complete sets A set of gates is complete if we can implement any

- 57. Basic Concepts (cont’d) Proving NAND gate is universal

- 58. Basic Concepts (cont’d) Proving NOR gate is universal

- 59. Logic Chips Basic building block: Transistor Three connection points Base Emitter Collector Transistor can operate Linear

- 60. Logic Chips (cont’d) NOT NAND NOR

- 61. Logic Chips (cont’d) Low voltage level: High voltage level: > 2.4V Positive logic: Low voltage represents

- 62. Logic Chips (cont’d)

- 63. Logic Chips (cont’d) Integration levels SSI (small scale integration) Introduced in late 1960s 1-10 gates (previous

- 64. Logic Functions Logical functions can be expressed in several ways: Truth table Logical expressions Graphical form

- 65. Logic Functions (cont’d) 3-input majority function A B C F 0 0 0 0 0 0

- 66. Logical Equivalence All three circuits implement F = A B function

- 67. Logical Equivalence (cont’d) Proving logical equivalence of two circuits Derive the logical expression for the output

- 68. Logical Equivalence (cont’d) Derivation of logical expression from a circuit Trace from the input to output

- 69. Logical Equivalence (cont’d) Proving logical equivalence: Truth table method A B F1 = A B F3

- 70. Thanks for your attention

- 71. LECTURE 4

- 72. #3 Boolean Algebra and Digital Logic Gates. #4 Combinational logic design. Completely and Incompletely Specified Logic

- 73. Outline Binary numbers Logic States Implementation The Buffer Logic Gate using n-p-n transistors Logic Gates using

- 74. Basic Concepts (cont’d) Number of functions With N logical variables, we can define 22N functions Some

- 75. Basic Concepts (cont’d) Complete sets A set of gates is complete if we can implement any

- 76. Basic Concepts (cont’d) Proving NAND gate is universal

- 77. Basic Concepts (cont’d) Proving NOR gate is universal

- 78. Logic Chips Basic building block: Transistor Three connection points Base Emitter Collector Transistor can operate Linear

- 79. Logic Chips (cont’d) NOT NAND NOR

- 80. Logic Chips (cont’d) Low voltage level: High voltage level: > 2.4V Positive logic: Low voltage represents

- 81. Logic Chips (cont’d)

- 82. Logic Chips (cont’d) Integration levels SSI (small scale integration) Introduced in late 1960s 1-10 gates (previous

- 83. Logic Functions Logical functions can be expressed in several ways: Truth table Logical expressions Graphical form

- 84. Logic Functions (cont’d) 3-input majority function A B C F 0 0 0 0 0 0

- 85. Logical Equivalence All three circuits implement F = A B function

- 86. Logical Equivalence (cont’d) Proving logical equivalence of two circuits Derive the logical expression for the output

- 87. Logical Equivalence (cont’d) Derivation of logical expression from a circuit Trace from the input to output

- 88. Logical Equivalence (cont’d) Proving logical equivalence: Truth table method A B F1 = A B F3

- 89. Thanks for your attention

- 90. LECTURE 5

- 91. «СРС»: SIS, Practice class and Lab class assignments explanation #5 Combinational and Sequential Circuit. Adders. Subtractors.

- 92. Outline «СРС» SIS assignments explanation Practice class Lab class SIS assignments explanation Boolean Identities/Postulates/laws Expressing logic

- 93. Boolean Identities / Postulates / laws Boolean Laws

- 94. Problem 2 (a) Implementation of f= ABCD + ABCD + BC(b) implementation of the simplified function

- 96. Simplification Using Boolean Identities f= ABCD + ABCD + BC

- 98. Complement of a Boolean Function (А + В + С)

- 99. Complement of a Boolean Function f= C'(AB + A'B'D + A'BD') f= C(AB + ABD +

- 100. Combinational and Sequential circuits

- 103. Full Adder

- 104. Logic Diagram of Full Adder

- 105. Two-bit Comparator

- 107. Full Subtractor

- 108. Logic Chips (cont’d) Integration levels SSI (small scale integration) Introduced in late 1960s 1-10 gates (previous

- 109. LECTURE 6

- 110. Multiplexer design Procedure and applications Lecture 6 Utebayeva dana

- 118. Truth table for MUX Truth table for 4-to-1 MUX

- 119. LECTURE 7

- 120. Demultiplexers and their Applications Lecture 7, By dana Utebayeva

- 121. DEMUX DEMULTIPLEXER

- 125. MUX and DEMUX applications

- 126. MUX and DEMUX applications

- 127. MUX and DEMUX applications

- 128. LECTURE 8 K-MAP K MAP KMAP

- 129. Introduction to Karnaugh map (k-map) СРС (SIS) by Dana Utebayeva

- 137. LECTURE 9

- 138. Sequential Circuit. Sequential logic design. Flip-Flop. Counters Lecture 9 By Dana Utebayeva

- 139. Sequential Circuit. Sequential logic design. Flip-Flop. Counters

- 140. In Sequential Circuit, the Present Output depends on the Present Input as well as Past output

- 142. Cascaded NOT logic gate

- 143. The basic storage element is called latch

- 151. LECTURE 11-12

- 152. Lecture 10-11 MICROCOMPUTER ARCHITECTURE Memory ADC and DAC

- 153. ADC and DAC 1.1 Basic Blocks of a Microcomputer 1.2 Typical Microcomputer Architecture 1.3 Single-Chip Microprocessor

- 154. ADC

- 155. ADC and DAC Work use of ADC and DAC Sound Waves Electrical Voltage Binary Data Electrical

- 156. Need Conversation

- 157. ADC in Multisim

- 158. DAC DAC scheme DAC circuit

- 159. A microcomputer has three basic blocks: a central processing unit (CPU), a memory unit, and an

- 160. 2.1 Basic Blocks of a Microcomputer System bus

- 161. In a single-chip microcomputer, these three elements are on one chip, whereas in a single-chip microprocessor,

- 162. 2.2 Typical Microcomputer Architecture Simplified version of typical microprocessor

- 163. The microcomputer’s system bus contains three buses, address, data, and control bus When a memory or

- 164. The Address Bus Unidirectional bus: Information transfer takes place in only one direction, from the microprocessor

- 165. The data bus, bidirectional bus: data can flow in both directions, that is, to or from

- 166. The control bus consists of a number of signals that are used to synchronize operation of

- 167. The system clock signals are contained in the control bus. The number of cycles per second

- 168. The microprocessor is the CPU of the microcomputer The logic inside the microprocessor chip can be

- 169. The number, size, and types of registers vary from one microprocessor to another. Basic Microprocessor Registers

- 170. Instruction register (IR) : The instruction register stores instructions. The word size of the microprocessor determines

- 171. Program Counter (PC): The program counter contains the address of the instruction or operation code (op-code).

- 172. How Program Counter is Work ? Upon activating the microprocessor’s RESET input, the address of the

- 173. Memory Address Register (MAR). The memory address register contains the address of data. The microprocessor uses

- 174. General Purpose Register (GPR). For an 8-bit microprocessor, the general-purpose register is called the accumulator. It

- 175. General Purpose Register (GPR). The term general-purpose comes from the fact that these registers can hold

- 176. Other Microprocessor Registers such as general-purpose registers, index register, status register and stack pointer register. general-purpose

- 177. Flags Type A carry flag is used to reflect whether or not the result generated by

- 178. Flags Type A zero flag is used to show whether the result of an operation is

- 179. Flags Type A sign flag (sometimes called a negative flag) is used to indicate whether the

- 180. EXAMPLE : Find the sign,carry,zero,overflow,and parity even flag for the following arithmetic sign number: (11110000)+(10100001) =10010001

- 181. Stack Pointer Register A stack consists of a number of RAM locations set aside for reading

- 182. 2.3.1 Register Section Push operation when accessing a stack from the bottom

- 183. 2.3.1 Register Section

- 184. 2.3.1 Register Section

- 185. 2.3.1 Register Section

- 186. The main purpose of the control unit is to read and decode instructions from the program

- 187. Control Signal Actions RESET. This input is common to all microprocessors. When this input pin is

- 188. Control Signal Actions READ/WRITE (R/W) This output line is common to all microprocessors. The status of

- 189. Control Signal Actions READY, This is an input to a microprocessor. Slow devices (memory and I/O)

- 190. Control Signal Actions Interrupt Request (INT or IRQ). The external I/O devices can interrupt the microprocessor

- 191. The ALU performs all the data manipulations, such as arithmetic and logic operations, inside a microprocessor.

- 192. Simple Microprocessor 2.3.4 Functional Representations of Simple and Typical Microprocessors

- 193. Buffer Register : Stores any data read from memory for further processing by the ALU. 2.3.4

- 194. Typical Microprocessor 2.3.4 Functional Representations of Simple and Typical Microprocessors

- 196. The Pentium contains two instruction pipelines: the U-pipe and the V-pipe. The U-pipe can execute all

- 197. The control unit performs two basic operations: instruction interpretation and instruction sequencing. 2.3.5 Simplified Explanation of

- 198. There are two methods for designing a control unit: 2.3.5 Simplified Explanation of Control Unit design

- 199. How incrementing the contents of the register by 1 is done in microprogramming control ?? (see

- 200. 2.3.5 Simplified Explanation of Control Unit design Transferring register contents to a data bus

- 201. 2.3.5 Simplified Explanation of Control Unit design

- 202. 2.3.5 Simplified Explanation of Control Unit design

- 203. 2.3.5 Simplified Explanation of Control Unit design

- 204. 2.3.5 Simplified Explanation of Control Unit design

- 205. The following three steps for completing the instruction: 1.Fetch. The microprocessor fetches (instruction read) the instruction

- 206. For example, suppose that it is desired to add the contents of two registers, X and

- 207. Enhancement in 32-bit microprocessors (like Pentium) include : cache memory, memory management, pipelining, floating-point arithmetic, and

- 208. Memory management allows programmers to write programs much larger than those that could fit in the

- 209. Basic Concept 2.5.1 Pipelining Hi is Hardware designed to perform activity Ai

- 210. 2.5.1 Pipelining

- 211. Two Kind of Pipelining: Arithmetic operations and instruction execution. 2.5.1 Pipelining

- 212. Arithmetic Pipelines Consider the process of adding two floating-point numbers x =0.9234 * 104 and y

- 213. Pipelined floating-point add/subtract unit segment

- 214. Instruction Pipelines Instruction cycle typically involves the following activities: 1. Instruction fetch -?needs five clocks to

- 215. Five-segment instruction pipeline

- 216. Example of the execution of a stream of five instructions: 11,12,13,14, and 15, in which I3

- 217. This allows these microprocessors to anticipate jumps of the instruction flow ahead of time. 2.5.2 Branch

- 218. To accomplish this, the Pentium includes on-chip hardware called the Branch Unit (BU). The BU contains

- 219. Scalar processors such as the 80486 can execute one instruction per cycle. The 80486 contains only

- 220. There are two types of microprocessor architectures: RISC and CISC. RISC stand for (reduced instruction set

- 221. 2.7 RISC vs. CISC

- 222. Intel’s original Pentium is a CISC microprocessor. Intel Pentium Pro and other succeeding members of the

- 223. LECTURE 11-12

- 224. Lecture 10-11 MICROCOMPUTER ARCHITECTURE Memory ADC and DAC

- 225. ADC and DAC 1.1 Basic Blocks of a Microcomputer 1.2 Typical Microcomputer Architecture 1.3 Single-Chip Microprocessor

- 226. Flags Type A zero flag is used to show whether the result of an operation is

- 227. Flags Type A sign flag (sometimes called a negative flag) is used to indicate whether the

- 228. EXAMPLE : Find the sign,carry,zero,overflow,and parity even flag for the following arithmetic sign number: (11110000)+(10100001) =10010001

- 229. Stack Pointer Register A stack consists of a number of RAM locations set aside for reading

- 230. 2.3.1 Register Section

- 231. 2.3.1 Register Section

- 232. 2.3.1 Register Section

- 233. 2.3.1 Register Section

- 234. The main purpose of the control unit is to read and decode instructions from the program

- 235. Control Signal Actions RESET. This input is common to all microprocessors. When this input pin is

- 236. Control Signal Actions READ/WRITE (R/W) This output line is common to all microprocessors. The status of

- 237. Control Signal Actions READY, This is an input to a microprocessor. Slow devices (memory and I/O)

- 238. Control Signal Actions Interrupt Request (INT or IRQ). The external I/O devices can interrupt the microprocessor

- 239. The ALU performs all the data manipulations, such as arithmetic and logic operations, inside a microprocessor.

- 240. Simple Microprocessor 2.3.4 Functional Representations of Simple and Typical Microprocessors

- 241. Buffer Register : Stores any data read from memory for further processing by the ALU. 2.3.4

- 242. Typical Microprocessor 2.3.4 Functional Representations of Simple and Typical Microprocessors

- 244. The Pentium contains two instruction pipelines: the U-pipe and the V-pipe. The U-pipe can execute all

- 245. The control unit performs two basic operations: instruction interpretation and instruction sequencing. 2.3.5 Simplified Explanation of

- 246. There are two methods for designing a control unit: 2.3.5 Simplified Explanation of Control Unit design

- 247. How incrementing the contents of the register by 1 is done in microprogramming control ?? (see

- 248. 2.3.5 Simplified Explanation of Control Unit design

- 249. 2.3.5 Simplified Explanation of Control Unit design

- 250. 2.3.5 Simplified Explanation of Control Unit design

- 251. 2.3.5 Simplified Explanation of Control Unit design

- 252. 2.3.5 Simplified Explanation of Control Unit design

- 253. The following three steps for completing the instruction: 1.Fetch. The microprocessor fetches (instruction read) the instruction

- 254. For example, suppose that it is desired to add the contents of two registers, X and

- 255. Enhancement in 32-bit microprocessors (like Pentium) include : cache memory, memory management, pipelining, floating-point arithmetic, and

- 256. Memory management allows programmers to write programs much larger than those that could fit in the

- 257. Basic Concept 2.5.1 Pipelining Hi is Hardware designed to perform activity Ai

- 258. 2.5.1 Pipelining

- 259. Two Kind of Pipelining: Arithmetic operations and instruction execution. 2.5.1 Pipelining

- 260. Arithmetic Pipelines Consider the process of adding two floating-point numbers x =0.9234 * 104 and y

- 262. Instruction Pipelines Instruction cycle typically involves the following activities: 1. Instruction fetch -?needs five clocks to

- 264. Example of the execution of a stream of five instructions: 11,12,13,14, and 15, in which I3

- 265. This allows these microprocessors to anticipate jumps of the instruction flow ahead of time. 2.5.2 Branch

- 266. To accomplish this, the Pentium includes on-chip hardware called the Branch Unit (BU). The BU contains

- 267. Scalar processors such as the 80486 can execute one instruction per cycle. The 80486 contains only

- 268. There are two types of microprocessor architectures: RISC and CISC. RISC stand for (reduced instruction set

- 269. 2.7 RISC vs. CISC

- 270. Intel’s original Pentium is a CISC microprocessor. Intel Pentium Pro and other succeeding members of the

- 271. LECTURE 12

- 277. • The Requirements of a memory chip A memory chip requires address lines to identity a

- 279. • INPUT AND OUTPUT (I/O) DEVICES : • Input/output devices are the means through which theMPU

- 281. • THE 8085 MPUoThe term microprocessing unit (MPU) is similar to theterm central processing unit (CPU)

- 283. • THE 8085 AND ITS PIN DESCRIPTION• The 8085 is an 8-bit general purpose microprocessorthat can

- 284. 8085 Microprocessor Pin Out Diagram

- 287. • Control and Status Signals :-o ALE-Address Latch Enable:This is a positive going pulse generated every

- 289. IO/M :This is a status signal used to differentiate between I/Oand memory operations.When it is high

- 292. • Interrupts :Processor has 5 interrupts. They are presented below inthe order of their priority (from

- 294. RST 7.5 is a maskable interrupt. When this interrupt isreceived the processor saves the contents of

- 298. TIMING SIGNALS FOR FETCHING AN INSTRUCTIONAt T1 , the high order 8 address bits (20H) are

- 300. During T3 the RD signal is Disabled (goes high). This turnsoff the output Tri-state buffers in

- 302. • DEMULTIPLEXING AD7-ADO• From the above description, it becomes obvious thatthe AD7- ADO lines are serving

- 303. Demultiplexing AD7-AD0

- 304. Given that ALE operates as a pulse during T1, wewill be able to latch the address.

- 306. • CYCLES AND STATES• From the above discussion, we can define terms thatwill become handy later

- 308. •GENERATING CONTROL SIGNALS• The 8085 generates a single RD signal. However, thesignal needs to be used

- 311. • THE 8085 MACHINE CYCLES• The 8085 executes several types of instructions witheach requiring a different

- 313. • OPCODE FETCH MACHINE CYCLE• The first step of executing any instruction is theOpcode fetch cycle.•

- 316. the memory read machine cycle• To understand the memory read machine cycle, let'sstudy the execution of

- 318. • MACHINE CYCLES VS. NUMBER OF BYTES INTHE INSTRUCTION• Machine cycles and instruction length, do not

- 319. LECTURE 13 MICROPROCESSORS

- 320. Microprocessors

- 322. Input / OutputInput DevicesSwitches , Keyboard , …Output Devices:Seven Segments (LEDs) , printer , Monitor ,…The

- 323. The CPU includes ALU, control Units, and Various Registers

- 324. The Von Neumann Model It uses von Neumann execution cycle (also called the fetch-decode-execute cycle)

- 326. A cycle could be as follows:The control unit fetches the next programinstruction from the memory, using

- 330. Advances in SemiconductorTechnologyIC- Integrated Circuits -> few transistors and diodes onone chipSSI -small scale Integration-> few

- 331. Microprocessor programming * Machine language Instruction written in binary format Assembly language Text based format add

- 332. Z80 instructions and alphanumeric codes

- 333. Microprocessor Based System

- 334. Microprocessor Unit Progremmable logic unit with a designed set of instructions

- 335. MPU frequently communicates with the memory, I/O devices

- 336. What does it needs to do so..

- 337. What does it needs to do so…Group of logic circuitsSet of signal to transfer informationControl signals

- 339. Program-initiated operationsand BusesanMicroprocessor and Memory OperationsMemory ReadReads instructions or data from the memoryMemory WriteWrites instructions and

- 341. Program-initiated operationsand BusesFrom where to read or to write?We need an address! Right?How the input/output will

- 343. BusesAddress BusIdentify the memorylocationsCPU(ALU, Registers,and Control)MemoryInputandOutputData BusData BusHolds the data duringAddress Bustransfer operationControl BusControl Lines° For

- 345. BusesAddress Bus Size - bitsDepends on the number of memory locations thatcan be accessedZ80 has 16

- 351. How the MPU Writes into the Memory?•MPU places the 16 bit address on the address busMemory

- 353. How the MPU reads from the Memory?MPU places the 16 bit address on the address busMemory

- 354. LECTURE 13 MICROPROCESSOR

- 358. BusesAddress Bus Size - bitsDepends on the number of memory locations thatcan be accessedZ80 has 16

- 360. Externally Initiated operationInterruptions categories :Reset - e. g. timer to reset everything in the MPUInterrupt -

- 366. LECTURE 14

- 367. Microcontrollers Fundamentals of Logic Design By Dana Utebayeva

- 368. Micro-Controller A single chip Computer (to some extent) Has CPU RAM EEPROM I/O in form of

- 369. Background Line Following Robots Wireless keyboards They were made using Microcontrollers

- 370. Suppose we want to make a Line following Robot What do we do ? Use a

- 371. Why not a Computer ? PC is a general purpose computer. Can run thousand of softwares

- 372. Why MCU Small reflected by the word “MICRO” Inexpensive Ideal for doing repetitive tasks Easy to

- 373. Selecting a MCU Two family of MCU extremely popular AVR PIC We use AVR series of

- 374. Tools Required -> CVAVR

- 375. Compiler -> CVAVR The code is written in C language so we need to convert it

- 376. Transfer code to Atmega AVR Studio

- 377. Avr Programmer

- 378. So we need two softwares overall CVAVR –> Editor and Compiler Avr Studio –> Transfer Code

- 379. Atmega 16

- 380. Basics of C language If else block If(condition) { … … } else { … …

- 381. While & For While (conditon) { … ... } for(initialisation; condition; increment) { … … }

- 383. Lets Begin by blinking a simple LED

- 384. Circuit Diagram

- 385. Getting Started with CVAVR

- 386. Open CVAVR Go to File New Project

- 387. Open CVAVR

- 388. Go to File

- 389. Click on New

- 390. Select Project- > Click OK

- 391. Click YES

- 392. Select Chip

- 393. Introduction to I/O

- 394. Atmega has total of 40 pins out of which 32 pins can be used as Input

- 395. Data Direction register (DDR) This sets direction for all pins (32) Direction for these pins can

- 397. What is Next ? We have set the Pin as Output What else do we need

- 398. PORT Register Only after you have set the Pin to Output you can control them through

- 399. Simple Questions DDRA= 0b 00101100 DDRD = 0xf4 DDRC = 0b 01111110 DDRB = 0x3b Assume

- 400. Setting I/O

- 401. Go to Ports

- 402. Click on In to make that pin Output Can do so for all four ports

- 403. Click on File

- 404. Generate Save and Exit

- 405. Enter name (3 times)

- 406. Where is the code stored ?

- 407. Then Click Save

- 408. Name of Project & Location

- 409. Writing the Code

- 410. NOTE : We write our code in While block While (1) { PORTA.1=1; // sets the

- 411. This is because Atmega runs at a frequency of 8000000 Hz We need to introduce delay

- 412. How to compile Code is written in C language but Atmega understands Hex file so we

- 413. Compiling

- 414. Make the Project

- 415. Check for errors

- 416. Hex File You can find the Hex file in Bin folder or the EXE folder of

- 417. So we Have our Code ready Feed this code to Atmega using Programmer (we will see

- 418. Lets add an Input Most Common Input ? Button Since we have already made A0 as

- 419. Circuit Diagram

- 420. Never leave any Input pin unconnected / floating at any point of time while your circuit

- 421. What is the Voltage at the Floating PIN ? Not 5 V Not 0V Its UNDEFINED

- 422. In Layman terms PULL DOWN : Gives 0V when unconnected PULL UP : Gives 5V when

- 423. Correct Circuit Diagram

- 424. PIN Register It is a 8 bit register . It corresponds to the pin in same

- 425. Using Pin Register int a; // Define the variable a to store the value of voltage

- 426. Code in Action

- 427. Microprocessor consists of only a Central Processing Unit, whereas Micro Controller contains a CPU, Memory, I/O

- 428. LECTURE 15 APPLICATIONS OF MICROPROCESSORS MICROCONTROLLERS

- 429. Applications of Microprocessors & Microcontrollers Dana Utebayeva

- 430. Outline

- 431. Best Processors of PCs and Laptops

- 432. Mobile Processor The mobile processor is used in mobile computers and cell phones. The CPU IC

- 433. 5 chips (in alphabetic order)especially designed for AI AMD Radeon Instinct Usage Radeon Instinct is AMD’s

- 434. Apple A11 Bionic Neural Engine The Apple A11 Bionic is a 64-bit ARM-based system on a

- 435. Google Tensor Processing Unit A tensor processing unit (TPU) is an application-specific integrated circuit (ASIC) developed

- 436. Huawei Kirin 970 Kirin 970 is powered by an 8-core CPU and a new generation 12-core

- 437. IBM Power9 Recently launched by IBM, Power9 is a chip which has a new systems architecture

- 438. Intel Nervana The Nervana ‘Neural Network Processor’ uses a parallel, clustered computing approach and is built

- 440. Скачать презентацию

Системы счисления

Системы счисления Методологические основы прогнозирования

Методологические основы прогнозирования Алгоритмизация и программирование

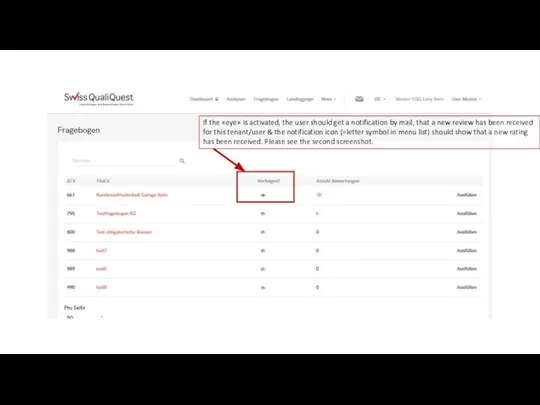

Алгоритмизация и программирование Bug notifications

Bug notifications Гаджеты спешат на помощь!

Гаджеты спешат на помощь! Развитие вычислительной техники

Развитие вычислительной техники Текстура и фактура 3D модели

Текстура и фактура 3D модели Категория целей в системном анализе

Категория целей в системном анализе The basics of working in R

The basics of working in R Программный интерфейс для парсинга и обработки данных из социальной сети Вконтакте

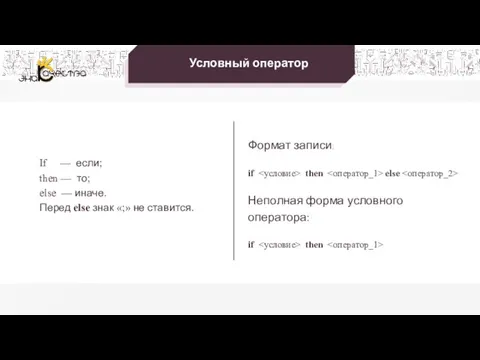

Программный интерфейс для парсинга и обработки данных из социальной сети Вконтакте Программирование разветвляющихся алгоритмов

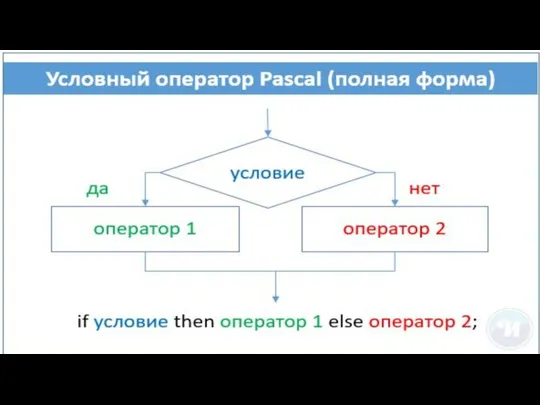

Программирование разветвляющихся алгоритмов Microsoft Office. Краткая характеристика изученных программ

Microsoft Office. Краткая характеристика изученных программ Последовательность Фибоначчи

Последовательность Фибоначчи ConnectKey – новые контроллеры для офисных МФУ

ConnectKey – новые контроллеры для офисных МФУ inf

inf Одномерные массивы

Одномерные массивы Использование свободного программного обеспечения для обучения графике

Использование свободного программного обеспечения для обучения графике Псевдокод. Дискретность

Псевдокод. Дискретность Файловые системы. Flash-носители. Конфиденциальность информации

Файловые системы. Flash-носители. Конфиденциальность информации Муравьиные сказки. Часть 2

Муравьиные сказки. Часть 2 Проблема идентификации пользователей сети Интернет

Проблема идентификации пользователей сети Интернет Системы счисления. Решение задач

Системы счисления. Решение задач Как найти свою первую работу программистом?

Как найти свою первую работу программистом? Тест по информатике компьютерные сети

Тест по информатике компьютерные сети منصة تعليمية لرياض األطفال

منصة تعليمية لرياض األطفال What kind of communication can not be carried out by the great invention of American scientists - the Internet?

What kind of communication can not be carried out by the great invention of American scientists - the Internet? Основы рисования в Microsoft Word

Основы рисования в Microsoft Word Игры в смартфоне: польза или вред? 1 класс

Игры в смартфоне: польза или вред? 1 класс