Содержание

- 2. Часть 2: Обработка данных 2.1 Архитектура компьютера 2.2 Концепция хранимой программы 2.3 Выполнение программы 2.4 Арифметические

- 3. Архитектура компьютера Процессор или CPU (Central Processing Unit) Арифметико-логический блок и устройство управления Регистры Общего назначения

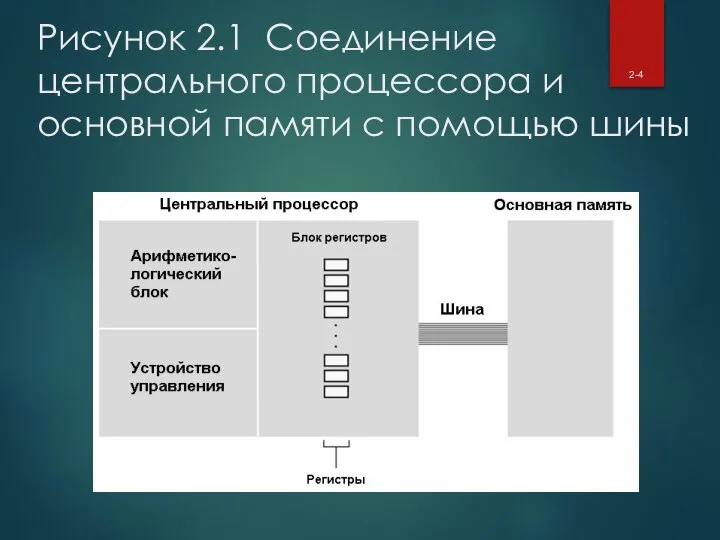

- 4. Рисунок 2.1 Соединение центрального процессора и основной памяти с помощью шины 2-

- 5. Концепция хранимой программы Программа должна быть закодирована в виде битовых последовательностей и хранится в оперативной памяти.

- 6. Терминология Машинная команда: Команда (инструкция), закодированная битовой комбинацией и распознаваемая процессором Машинный язык: Полный набор машинных

- 7. Философия машинных языков Компьютер с сокращенным набором команд (RISC - Reduced Instruction Set Computing) Инструкций мало,

- 8. Типы машинных команд Передача данных: копирование данных из одного места в другое Арифметико-логические: используют существующие битовые

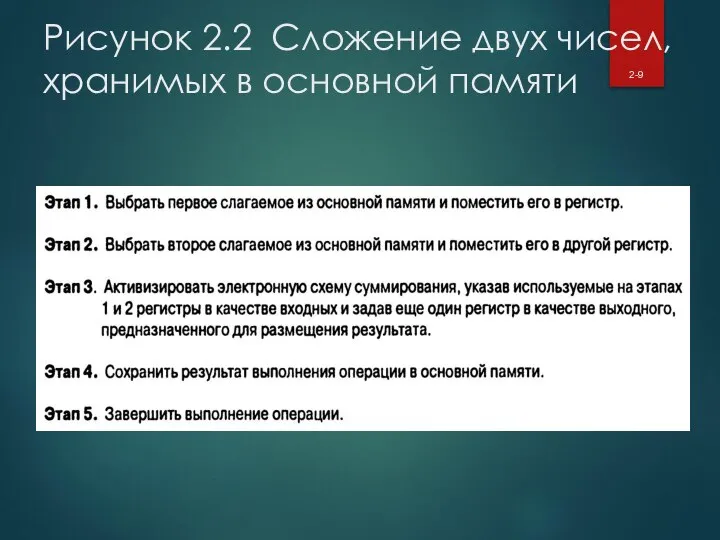

- 9. Рисунок 2.2 Сложение двух чисел, хранимых в основной памяти 2-

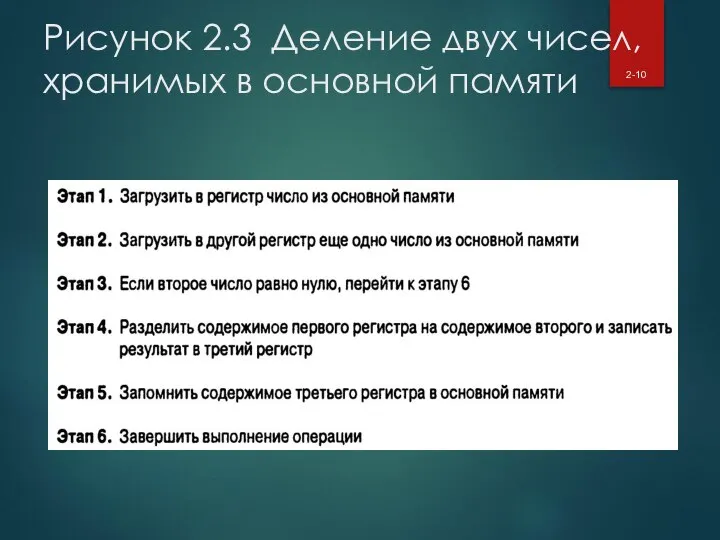

- 10. Рисунок 2.3 Деление двух чисел, хранимых в основной памяти 2-

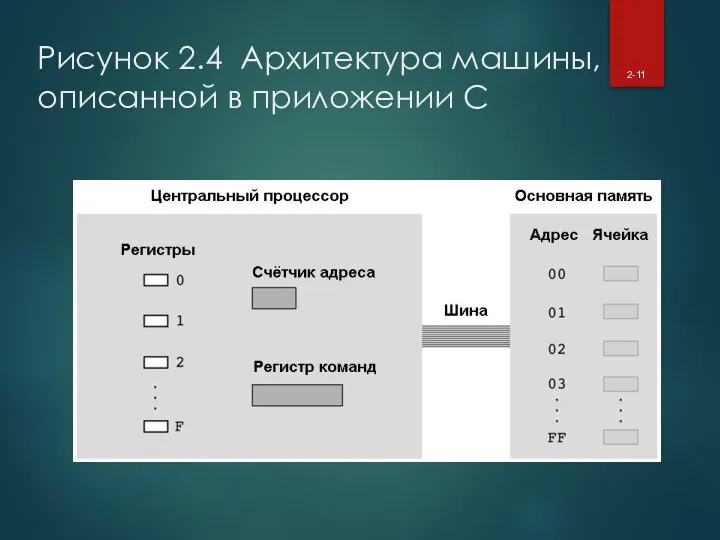

- 11. Рисунок 2.4 Архитектура машины, описанной в приложении C 2-

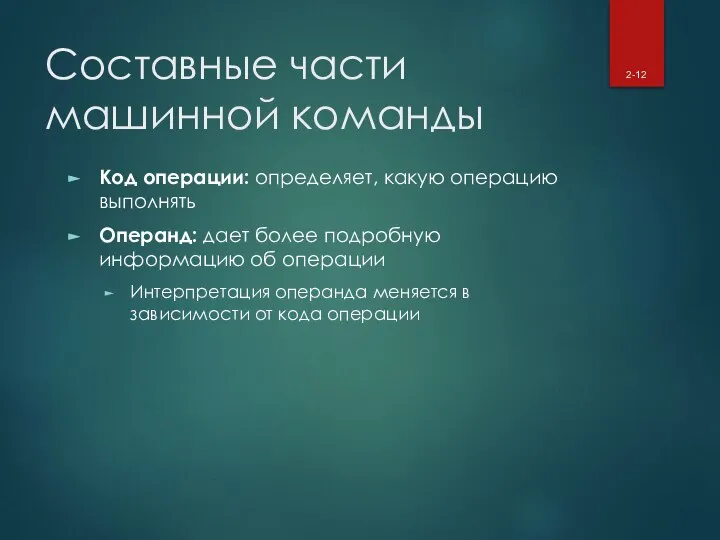

- 12. Составные части машинной команды Код операции: определяет, какую операцию выполнять Операнд: дает более подробную информацию об

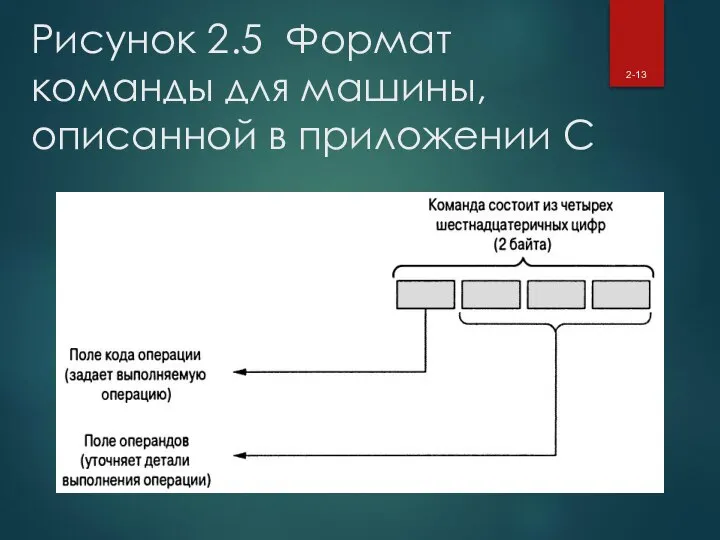

- 13. Рисунок 2.5 Формат команды для машины, описанной в приложении C 2-

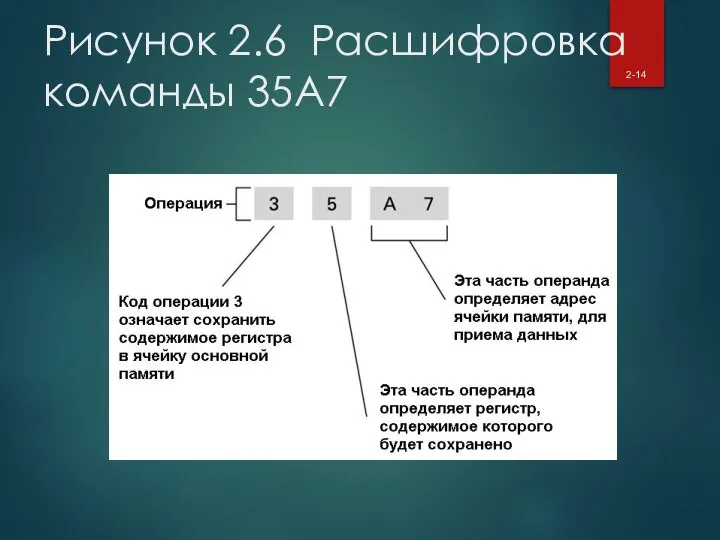

- 14. Рисунок 2.6 Расшифровка команды 35A7 2-

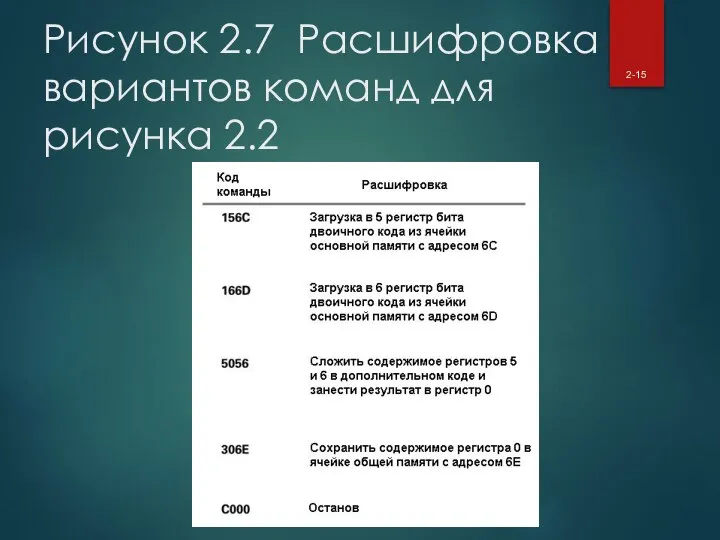

- 15. Рисунок 2.7 Расшифровка вариантов команд для рисунка 2.2 2-

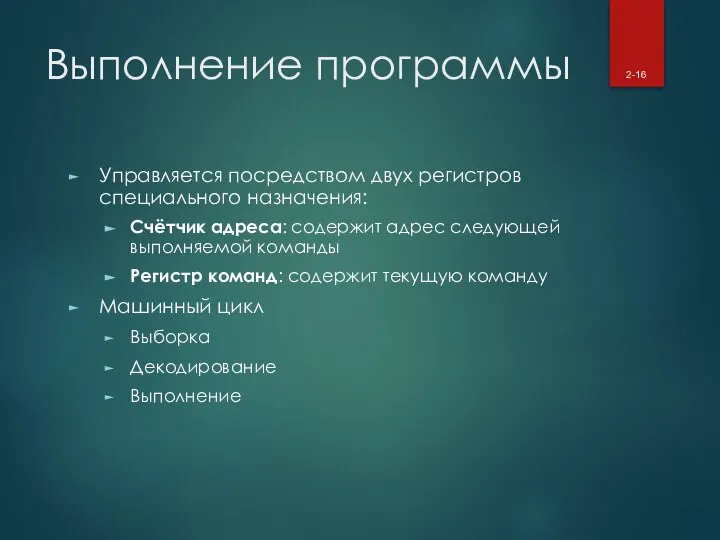

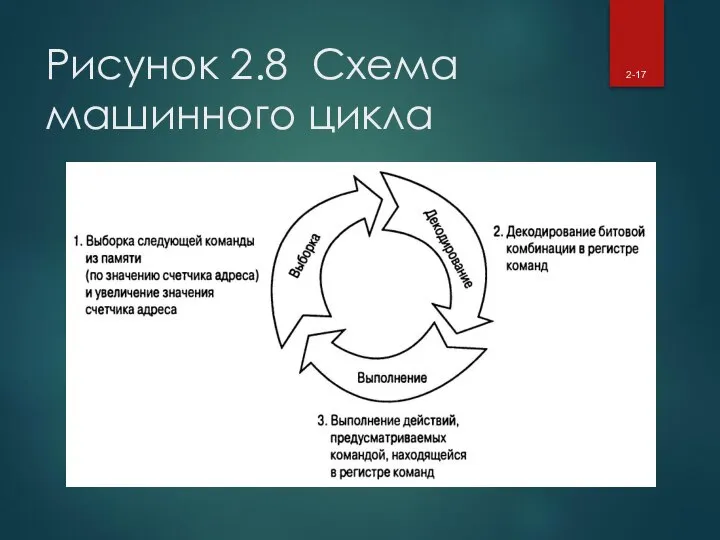

- 16. Выполнение программы Управляется посредством двух регистров специального назначения: Счётчик адреса: содержит адрес следующей выполняемой команды Регистр

- 17. Рисунок 2.8 Схема машинного цикла 2-

- 18. Рисунок 2.9 расшифровка команды B258 2-

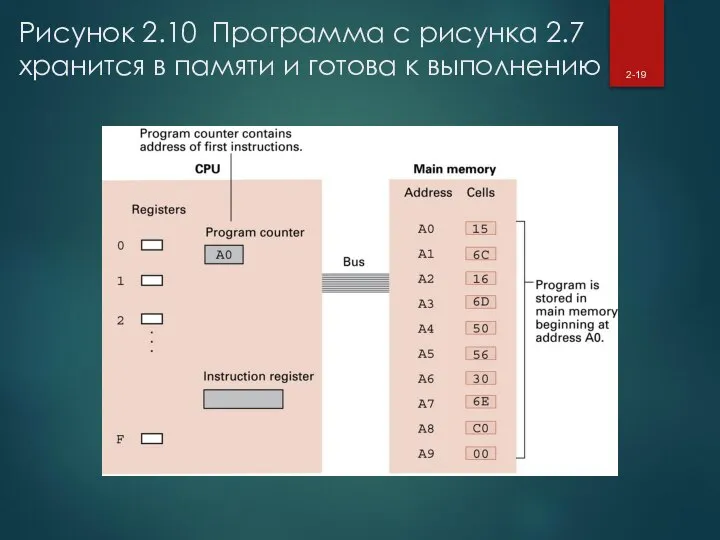

- 19. Рисунок 2.10 Программа с рисунка 2.7 хранится в памяти и готова к выполнению 2-

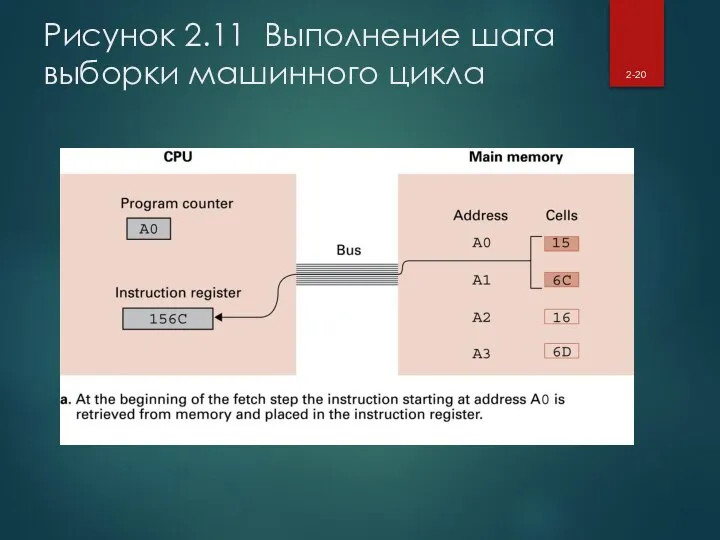

- 20. Рисунок 2.11 Выполнение шага выборки машинного цикла 2-

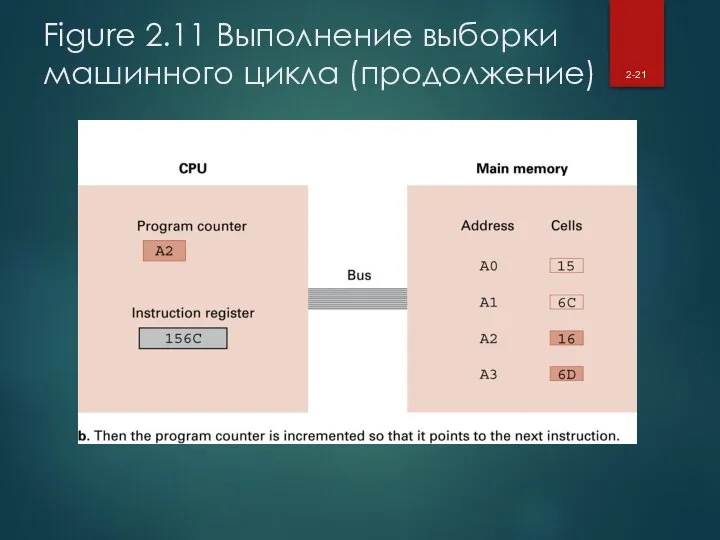

- 21. Figure 2.11 Выполнение выборки машинного цикла (продолжение) 2-

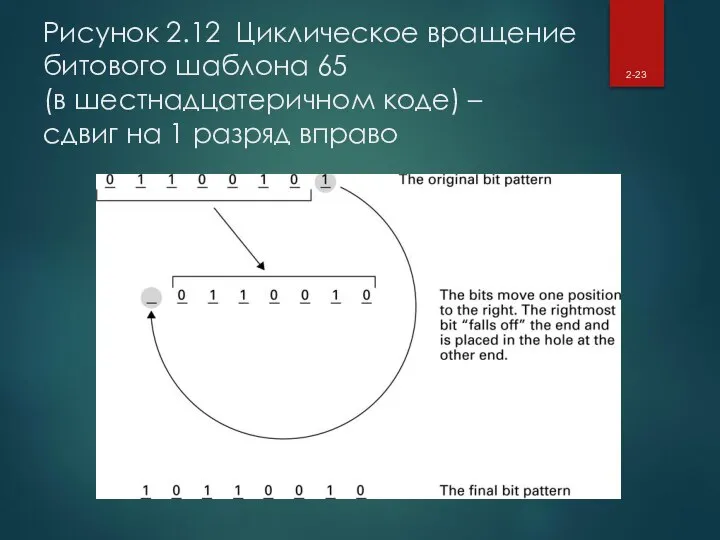

- 22. Арифметико-логические операции Логические: AND, OR, XOR Маскирование Вращение и сдвиг: циклический сдвиг, логический сдвиг, арифметический сдвиг

- 23. Рисунок 2.12 Циклическое вращение битового шаблона 65 (в шестнадцатеричном коде) – сдвиг на 1 разряд вправо

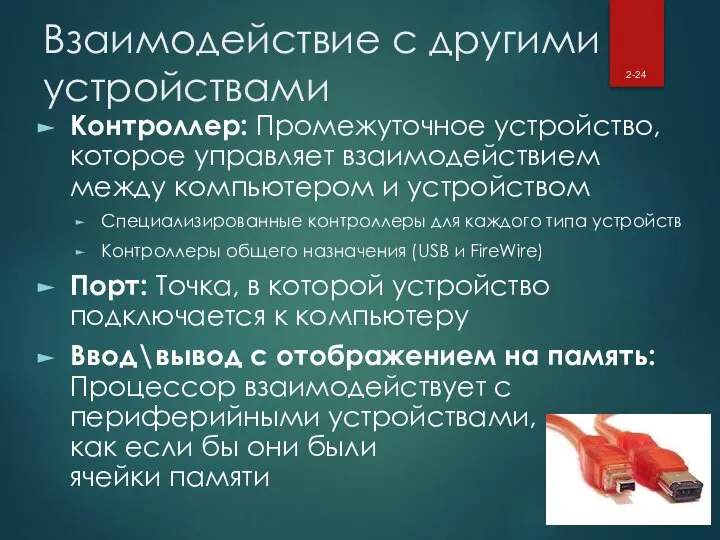

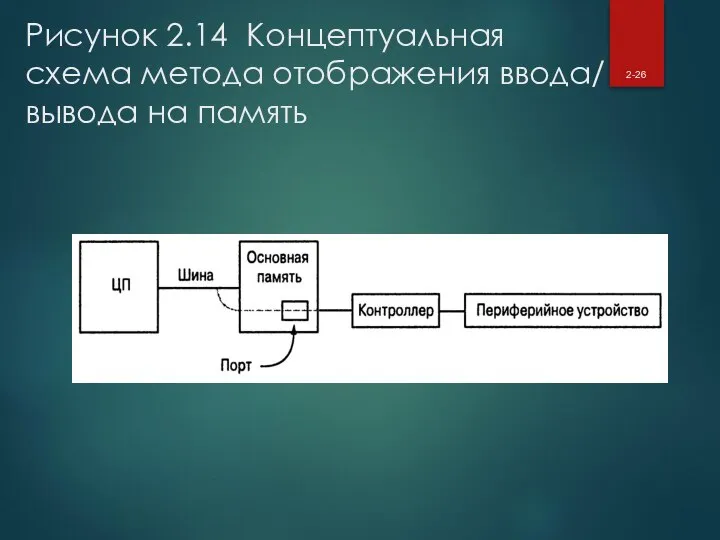

- 24. Взаимодействие с другими устройствами Контроллер: Промежуточное устройство, которое управляет взаимодействием между компьютером и устройством Специализированные контроллеры

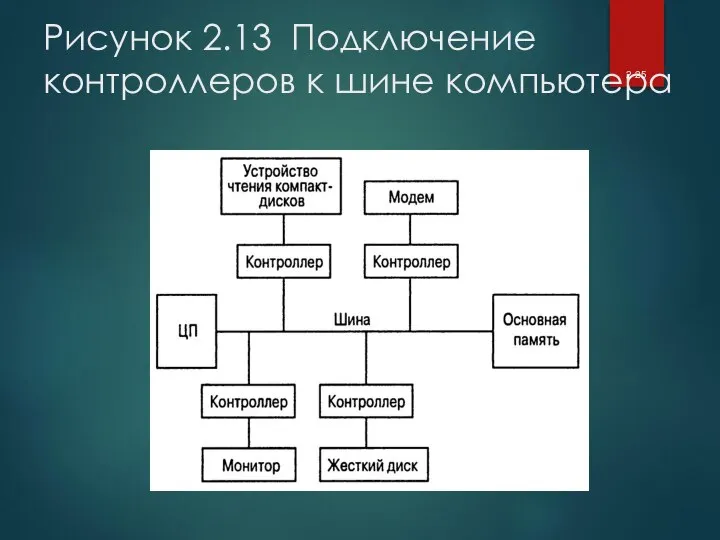

- 25. Рисунок 2.13 Подключение контроллеров к шине компьютера 2-

- 26. Рисунок 2.14 Концептуальная схема метода отображения ввода/ вывода на память 2-

- 27. Взаимодействие с другими устройствами (продолжение) Прямой доступ к памяти (DMF - Direct memory access): Основная память

- 28. Взаимодействие с другими устройствами (продолжение) Параллельная передача: Нескольких битов одновременно передаются по каналам связи. Последовательная передача:

- 29. Скорости передачи данных Единицы измерения Bps: биты в секунду Kbps: Kilo-bps (1,000 bps) Mbps: Mega-bps (1,000,000

- 31. Скачать презентацию

Технические устройства в презентации

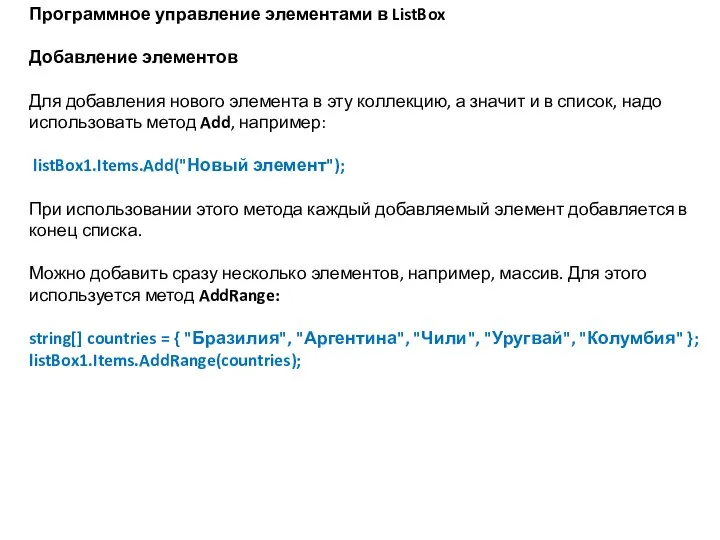

Технические устройства в презентации (1 пара)Тема 2.3. RadioButton

(1 пара)Тема 2.3. RadioButton Массивы и структуры

Массивы и структуры Обработка исключений. Лекция 12

Обработка исключений. Лекция 12 Алгоритмы с ветвлением и циклом. 3 класс

Алгоритмы с ветвлением и циклом. 3 класс 5298

5298 Информационные услуги

Информационные услуги Статистическая сводка и группировка

Статистическая сводка и группировка Информация. Знания. Информационные процессы

Информация. Знания. Информационные процессы Организация вычислений в электронных таблицах. Абсолютные и относительные ссылки

Организация вычислений в электронных таблицах. Абсолютные и относительные ссылки Презентация на тему Паскаль

Презентация на тему Паскаль  Основные конструкции языка С++. Подпрограммы (функции). Создаем переключатель цвета

Основные конструкции языка С++. Подпрограммы (функции). Создаем переключатель цвета Разработка подсистемы управления доступом инфрастуктуры безопасности распределительных информационно-вычислительных систем

Разработка подсистемы управления доступом инфрастуктуры безопасности распределительных информационно-вычислительных систем Шутер. Враги и снаряды

Шутер. Враги и снаряды Оформление публикаций

Оформление публикаций Computer Networks (lecture 9)

Computer Networks (lecture 9) Презентация на тему Персональные данные и их защита

Презентация на тему Персональные данные и их защита  İqtisadi informatika

İqtisadi informatika Цифровые технологии и сервисы ФНС России

Цифровые технологии и сервисы ФНС России МО СО

МО СО Cisco packet tracer physical layer 1

Cisco packet tracer physical layer 1 Презентация на тему Введение в теорию графов

Презентация на тему Введение в теорию графов  Интернет как один из источников информационного обеспечения фундаментальных и прикладных научных исследований

Интернет как один из источников информационного обеспечения фундаментальных и прикладных научных исследований Анализ методов и средств резервного копирования

Анализ методов и средств резервного копирования Системи обробки тексту

Системи обробки тексту Аниме. Игра

Аниме. Игра Проектирование информационной системы риелторского агентства

Проектирование информационной системы риелторского агентства Основы построения и функционирования

Основы построения и функционирования