Содержание

- 2. Архитектура ЭВМ и микроархитектура процессора 2. Архитектура процессора включает: 2.1. Набор и доступность регистров (программную модель

- 4. Иерархия памяти [3] Микроархитектура Nehalem L0: L1: L2: L3: L4: L5: L6: Регистры (4 ядра) 4

- 5. Программная модель процессора [1, 2] Архитектура IA-32 до процессора Pentium 4 Программная модель процессора в архитектуре

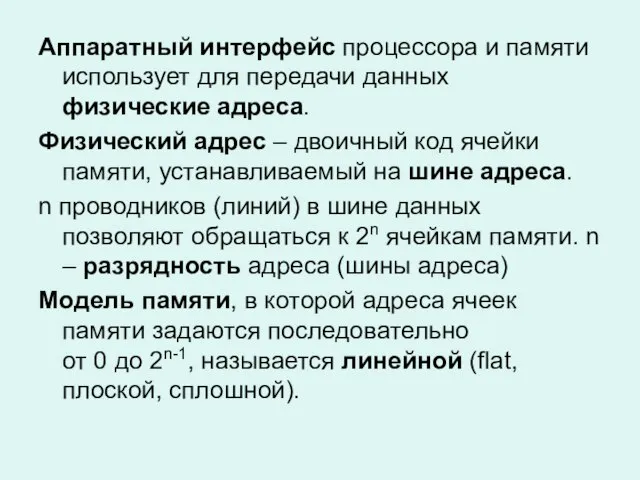

- 6. Аппаратный интерфейс процессора и памяти использует для передачи данных физические адреса. Физический адрес – двоичный код

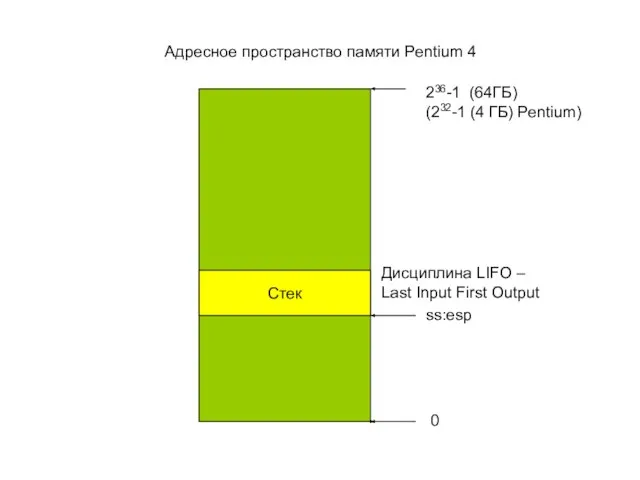

- 7. Адресное пространство памяти Pentium 4 Стек ss:esp 0 236-1 (64ГБ) (232-1 (4 ГБ) Pentium) Дисциплина LIFO

- 8. Логическая адресация осуществляется с использованием блоков смежных адресов, называемые сегментами. В пределах сегмента можно использовать линейную

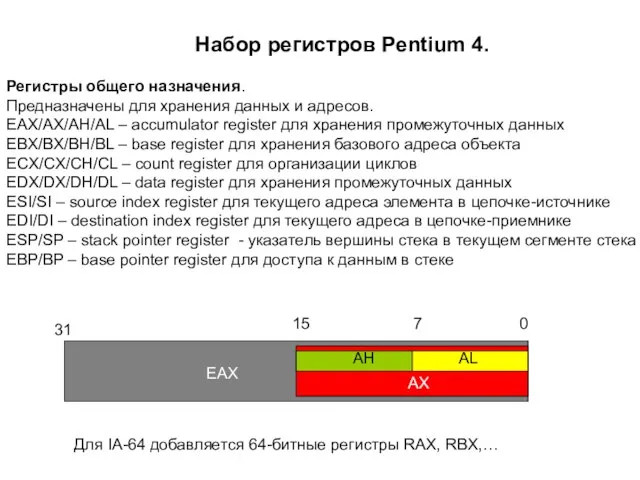

- 9. Набор регистров Pentium 4. Регистры общего назначения. Предназначены для хранения данных и адресов. EAX/AX/AH/AL – accumulator

- 10. Сегментные регистры Аппаратная поддержка сегментной организации вычислений. 3 сегмента программы: код (команды), данные, стек. CS –

- 11. Регистры состояния и управления EIP/IP – instruction pointer register – адрес следующей подлежащей выполнению команде (смещение

- 12. 4 регистра системных адресов: GDTR (48) - Global Descriptor Table register – предел (размер таблицы) (0-15)

- 13. Регистры сопроцессора 8 регистров стека сопроцессора R0-R7 (80) 0-63 - мантисса, 64-78 – порядок, 79 –

- 14. Регистры целочисленного MMX-расширения MultiMedia eXtensions начиная с Pentium MMX MMX реализует целочисленные SIMD (Single Instruction Multiple

- 16. Скачать презентацию

![Иерархия памяти [3] Микроархитектура Nehalem L0: L1: L2: L3: L4: L5: L6:](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/469195/slide-3.jpg)

![Программная модель процессора [1, 2] Архитектура IA-32 до процессора Pentium 4 Программная](/_ipx/f_webp&q_80&fit_contain&s_1440x1080/imagesDir/jpg/469195/slide-4.jpg)

Обучение монологической речи на базе художественного текста

Обучение монологической речи на базе художественного текста Высокое Возрождение

Высокое Возрождение Христианский праздник, рождение Христа

Христианский праздник, рождение Христа Комплексное решение для организации услуг OTT. Транскодирование, доставка контента, управление абонентами

Комплексное решение для организации услуг OTT. Транскодирование, доставка контента, управление абонентами О ходе мониторинга достижения целевых показателей национальных проектов

О ходе мониторинга достижения целевых показателей национальных проектов Сибирский специалитет. Промо – дегустация

Сибирский специалитет. Промо – дегустация Наш любимый Успенский район

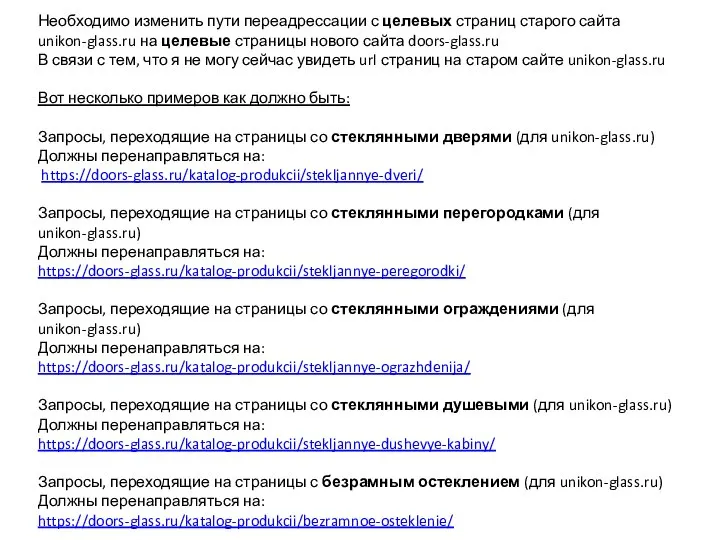

Наш любимый Успенский район Переадрессация на страницы

Переадрессация на страницы www.ackom.net

www.ackom.net Действия по урегулированию конфликта. Практическое задание № 1

Действия по урегулированию конфликта. Практическое задание № 1 Территориальные споры и их причины

Территориальные споры и их причины Художественная резьба по дереву (7 класс)

Художественная резьба по дереву (7 класс) Модель ВАЗ

Модель ВАЗ PRICKLY FARM

PRICKLY FARM Сложения чисел в столбик

Сложения чисел в столбик Воспитатель ---- кто он ?

Воспитатель ---- кто он ? Внимание к людям – внимание людей

Внимание к людям – внимание людей Политическая карта мира

Политическая карта мира Почтовые секреты Что нужно знать, работая с «Укрпочтой»

Почтовые секреты Что нужно знать, работая с «Укрпочтой» Itvpd_Bi21_Spark_Zadanie (1)

Itvpd_Bi21_Spark_Zadanie (1) КУЛЬТУРА И ТРАДИЦИИ КУБАНСКОГО КАЗАЧЕСТВА

КУЛЬТУРА И ТРАДИЦИИ КУБАНСКОГО КАЗАЧЕСТВА Н.В.Гоголь «Мертвые души» Чичиков и помещики

Н.В.Гоголь «Мертвые души» Чичиков и помещики Животворящий кислород BigOx

Животворящий кислород BigOx Прямой поставщик товаров из Китая

Прямой поставщик товаров из Китая Индийская культура в творчестве К. Д. Бальмонта

Индийская культура в творчестве К. Д. Бальмонта  Внутренняя энергия

Внутренняя энергия Достопримечательности Новосибирска

Достопримечательности Новосибирска Роль государства в экономике

Роль государства в экономике