Слайд 2Pojmovi

Memorija - specijalizovan hardver namenjen čuvanju informacija.

Sastoji se od memorijskog medijuma

i upravljačkog sistema.

Dve osnovne operacije, čitanje i pisanje.

Слайд 3Pojmovi

Podaci (u glavnoj memoriji) organizovani u reči (kao osnovne jedinice)*.

Van glavne

memorije postoje različiti načini organizacije(npr. sektori kod hard diska)

*Dužina reči memorije(najčešće) odgovara dužini instrukcije, odnosno dužini prikazivanja celog broja, odnosno dužini procesorske reči.

Слайд 4Načini pristupa memoriji

Adresni pristup - podaci se traže po njihovoj lokaciji

Direktni

Poludirektni

Sekvencijalni

Asocijativni pristup

- podaci se traže po sadržaju

Слайд 5Direktni pristup

Karakteristično za RAM

Svaka memorijska lokacija ima jedinstveni identifikator

Vreme pristupa konstantno

Takođe

se naziva i slučajni pristup

Слайд 6Poludirektni pristup

Grupa podataka nalazi se na istoj adresi

Karakteristično kod spoljne memorije (recimo,

hard diskova, gde su podaci organizovani po sektorima)

Vreme pristupa zavisi od pozicije mehanizma za čitanje

Слайд 7Sekvencijalni pristup

Podaci organizovani u zapise koji slede jedan za drugim

Da bi se

našao neki podatak, mora se preći kroz sve predhodne

Primer, magnetne trake (kod starijih računara)

Vreme pristupa se razlikuje za svaki podatak

Слайд 8Asocijativni pristup

Reč se iz memorije izvlači na osnovu sadržaja, a ne na

osnovu lokacije

Vreme pristupa konstantno

Čest slučaj kod keš memorija

Слайд 9Vreme pristupa

Vreme koje protekne od dovođenja signala (za čitanje ili upis) do

trenutka kada je podatak na magistrali podataka, ili do trenutka kada je podatak upisan, respektivno.

Vreme između dva uzastopna pristupa memoriji jeste memorijski ciklus*.

*u opštem slučaju duži od vremena pristupa zbog tehničkih razloga

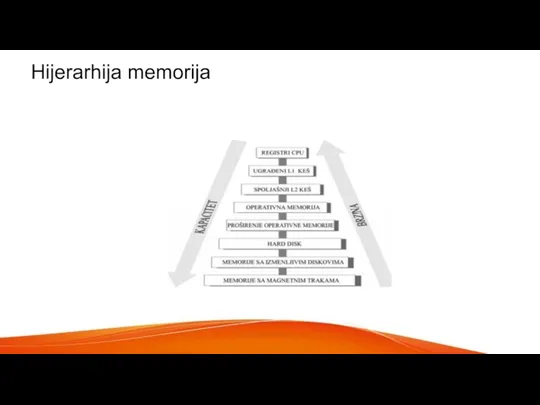

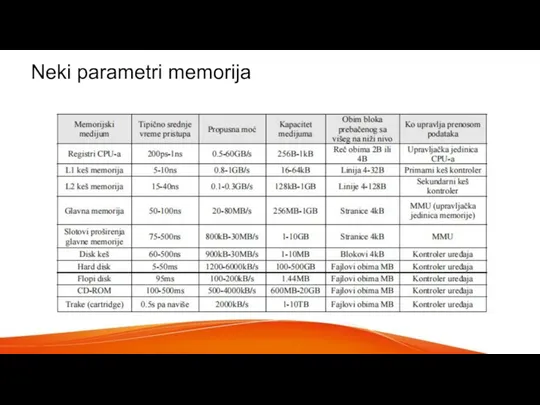

Слайд 10Hijerarhija memorija

Bitne karakteristike: brzina memorije, kapacitet, cena

Idealni računar imao bi jeftinu, brzu

memoriju velikog kapaciteta brzina cena

kapacitet cena

kapacitet brzina

Слайд 11Hijerarhija memorija

Za efikasan rad suštinski bitna brzina memorije.

Prilaskom kroz hijerarhiju:

smanjije

se cena po bitu

povećava se kapacitet

povećava se vreme pristupa

smanjuje se učestalost pristupa memoriji od strane procesora.

Слайд 13Registri

Lokalna memorija procesora

Čuva podatke dok se obrađuju

Desetak registara po procesoru

Vreme pristupa

~1ns

Слайд 14Keš

Cache - skriven (fr.)

Brza memorija (brzine procesora ili uporediva)

Sastoji se

od keš kontrolera i memorijskih (SRAM) čipova.

L1 unutar čipa (nekoliko desetina kilobajta)

L2 van čipa (nekoliko megabajta), vreme pristupa ~10ns

Слайд 15Operativna (glavna) memorija

Vreme pristupa nekoliko desetina ns

Procesor joj može pristupiti direktno

Слайд 16Hard disk/SSD

Vreme pristupa nekoliko desetina ms.

Pristup poludirektan (podaci organizovani u sektore).

Kod

HDD-a podaci se čuvaju magnetskim putem

Kod SSD-a podaci se čuvaju elektronskim putem, na NAND čipovima (flash memorija)

Слайд 17Memorija sa izmeljivim diskovima

CD

DVD

Floppy

Vreme pristupa nekoliko stotina ms (kod optičkih medijuma) do

sekinde (kod magnetskih traka)

Слайд 18Virtuelizacija

Proces prividnog povećanja kapaciteta memorije

Adresni prostor (skup svih mogućih adresa) objedinjuje primarnu

i sekundarnu memoriju (RAM i hard disk)

Svaka virtuelna adresa identifikuje podatak koji može biti u RAM-u ili na hard disku

Ukoliko je podatak na hard disku, on se mora prebaciti u RAM kako bi se mogao obraditi (straničenje)

Слайд 20Poluprovodničke memorije

Primarna memorija izrađena je u poluprovodičkoj tehnologiji. Osnovni element poluprovodničke memorije

je memorijska ćelija.

Слайд 21Poluprovodničke memorije

Ćelija najčešće ima tri terminala koji mogu da nose električni signal.

upravljački

terminal

terminal izbora

ulazno/izlazni terminal

Слайд 22Poluprovodničke memorije

RAM - random access memory, za čitanje i pisanje

ROM - read

only memory, za trajno čuvanje podataka, pri čemu se može samo čitati

RAM mogu biti statičke i dinamičke

Memorijski elementi izrađeni su od tranzistora.

bipolarni tranzistori (npn, pnp)

MOS tranzistori (NMOS, PMOS)

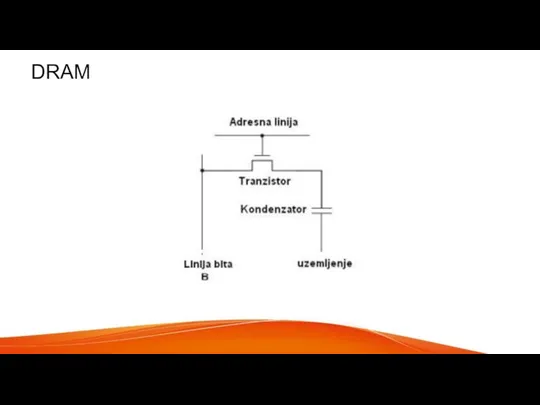

Слайд 24DRAM

Jednostavna tehnologija

Može se gusto pakovati

Mora da se osvežava (potreban poseban hardver za

osvežavanje)

Problem - potreba za memorijom dok se ona osvežava

Слайд 25DRAM

Generalno, DRAM je asihnrona memorija, tj. radi van procesorskog takta.

SDRAM

ili sinhroni DRAM radi na taktu procesora, što znači da je spreman za prenos podataka kada CPU to i očekuje.

Prenos kod SDRAM traje nekoliko taktova, tako da je CPU slobodan da radi neki drugi posao

Слайд 26DRAM

DDR SDRAM je dvostruko brža od SDRAM memorije, zato što podatke

može da šalje i na uzlaznom i na silaznom delu signala. Danas imamo verzije DDR3 i DDR4 ove memorije

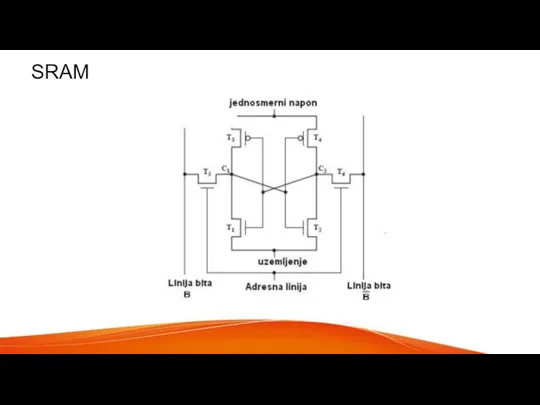

Слайд 28SRAM

Ćelije su bistabilne

Ne zahtevaju osvežavanje

Mnogo tranzistora => gustina pakovanja znatno manja od

DRAM memorije

Skupe

Слайд 29Postojane (poluprovodničke) memorije

Postojane memorije možemo podeliti u sledeće klase:

MASK ROM

memorije kod kojih se sadržaj unosi još u procesu proizvodnje,

PROM memorije kod kojih se sadržaj unosi naknadno,

EPROM memorije kod kojih se naknadno uneti sadržaj može i izbrisati i

NVRAM memorije koje se veći deo vremena ponašaju kao ROM, ali čiji se podaci mogu promeniti na zahtev

Слайд 30MASKROM

Sadržaj memorije definiše se u samom procesu proizvodnje

U finalnom delu proizvodnje,

tranzistori ove memorije se povezuju graviranjem metalne maske koja se naknadno nanosi

Ukoliko želimo logičku jedinicu, između adresne linije i linije podataka postavlja se dioda

Слайд 31PROM

Programmable ROM - korisnik može sam trajno da zapiše podatak (jednom)

Redno

sa diodom ugrađen topljivi osigurač

Programiranje podrazumeva da se na mestima logičke nule osigurač otopi

Слайд 32EPROM

Erasable PROM

Programiranje se vrši preko posebnog kontrolera, brisanje u komorama sa

ultraljubičastom svetlošču

EEPROM - electrically EPROM, brisanje se vrši električnim putem. Poseban tip EEPROM jeste flash memorija (dobila naziv po velikoj brzini upisa)

Слайд 33NVRAM

Non-volatile RAM, memorija sa nasumičnim pristupom i postojanim čuvanjem podataka

Izrađena najčešće u

CMOS tehnologiji

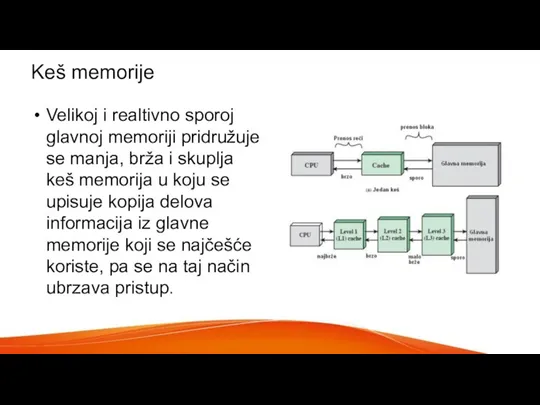

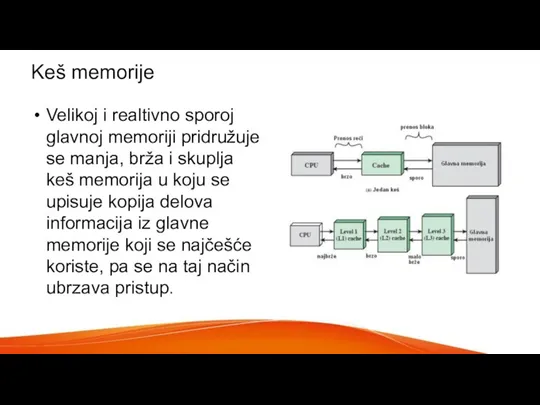

Слайд 34Keš memorije

Velikoj i realtivno sporoj glavnoj memoriji pridružuje se manja, brža i

skuplja keš memorija u koju se upisuje kopija delova informacija iz glavne memorije koji se najčešće koriste, pa se na taj način ubrzava pristup.

Слайд 35Keš

Zasniva se na principu lokalnosti (prostorne i vremenske)

Vremenska lokalnost - instrukcije koje

su skoro korišćene će verovatno biti ponovo korišćene

Prostorna lokalnost - instrukcije koje se nalaze blisko u memoriji će verovatno biti korišćene brzo jedna posle druge

Слайд 36Keš

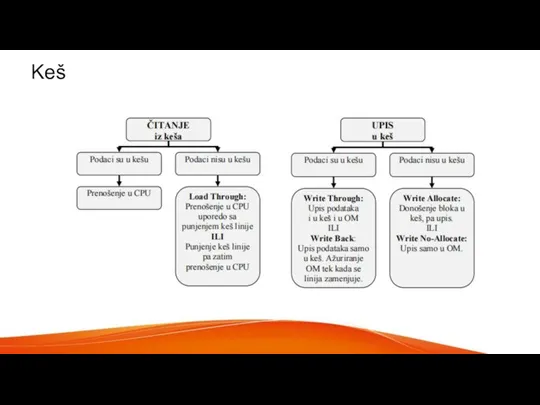

Procesor šalje upit za neki podatak upravljačkom sistemu memorije. Keš kontroler će

proveriti da li se taj podatak nalazi u okviru SRAM čipova (cache hit).

Možemo prvo tražiti u keš memoriji (look through cache), ili keš može nadgledati upit RAM memoriji i onda obezbediti podatak ako se nalazi kod njega (look aside cache)

Ukoliko podatak nije u kešu, to je cache miss.

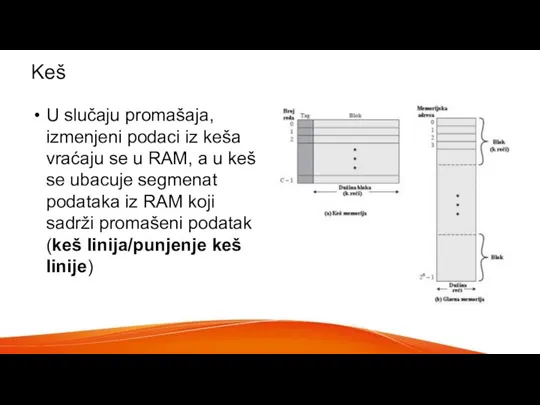

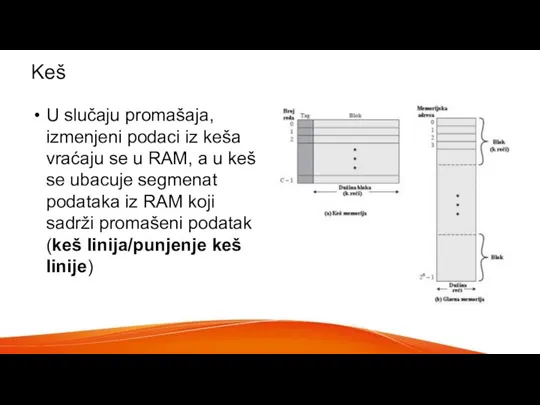

Слайд 37Keš

U slučaju promašaja, izmenjeni podaci iz keša vraćaju se u RAM, a

u keš se ubacuje segmenat podataka iz RAM koji sadrži promašeni podatak (keš linija/punjenje keš linije)

Слайд 38Keš

RAM se sastoji od reči, koje se organizuju u blokove od po

k reči

Keš se sastoji od redova, u svakom redu može biti upisan jedan blok

Tag, identifikator koji blok u memorije se nalazi u nekom redu (nema dovoljno redova za sve blokove)

Слайд 39Keš

Veza između redova u kešu i blokova u RAM data je funkcijom

mapiranja

Ukoliko je keš pun, neku liniju treba vratiti nazad u RAM i doneti nove podatke; ovo je određeno algoritmom zamene

Слайд 41Strategije za popunjavanje keša

Odabir funkcije preslikavanja

Mogu da se koriste tri tehnike:

direktno

preslikavanje,

asocijativno preslikavanje

set asocijativno preslikavanje.

Слайд 42Strategije za popunjavanje keša

Neka su pretpostavke sledeće: Dužina reči u memoriji je

1B. Memorija je veličine 128 bajtova, što znači da postoji 2^7 mogućih adresa. Samim tim, adresa je dužine 7 bitova. Neka je veličina svakog bloka u RAM memoriji 8B. To znači da postoji ukupno 16 blokova unutar RAM. Neka je ukupna veličina keša 32B. Svaki red(linija) u kešu odgovara jednom bloku, pa ukupno postoje 4 moguća reda.

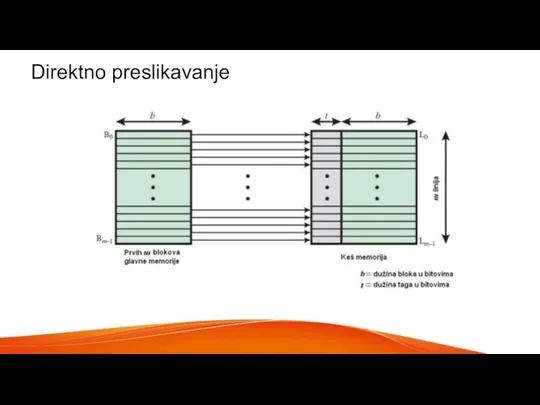

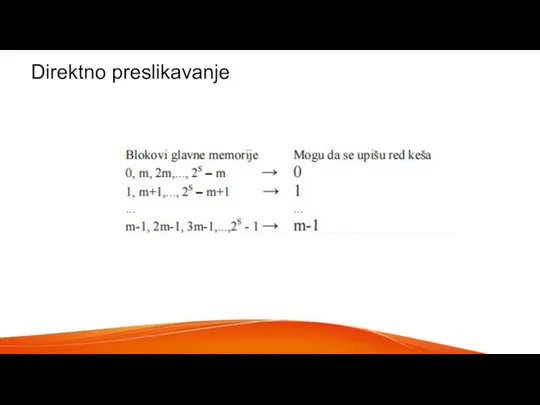

Слайд 44Direktno preslikavanje

Svaki blok u RAM se preslikava samo u jedan red keš

memorije. Funkcija preslikavanja u ovom slučaju je

i = j mod m gde je:

i = broj reda keša

j = broj bloka glavne mem.

m = broj redova u kešu.

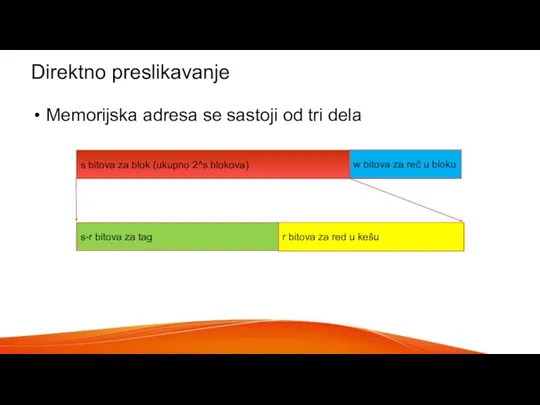

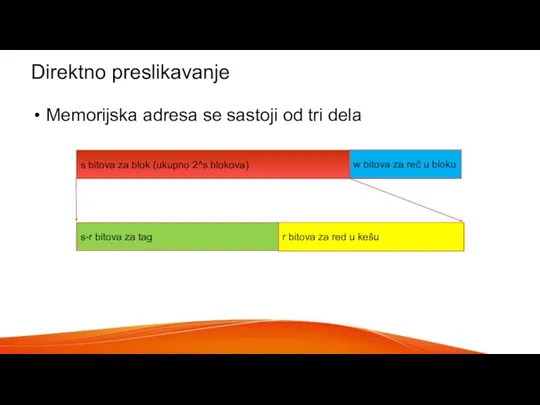

Слайд 45Direktno preslikavanje

Memorijska adresa se sastoji od tri dela

s bitova za blok (ukupno

2^s blokova)

w bitova za reč u bloku

s-r bitova za tag

r bitova za red u kešu

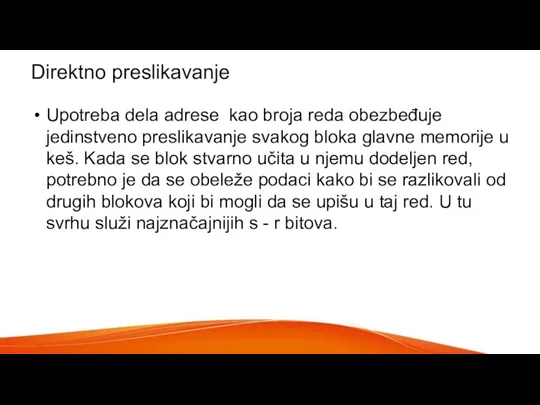

Слайд 46Direktno preslikavanje

Upotreba dela adrese kao broja reda obezbeđuje jedinstveno preslikavanje svakog bloka

glavne memorije u keš. Kada se blok stvarno učita u njemu dodeljen red, potrebno je da se obeleže podaci kako bi se razlikovali od drugih blokova koji bi mogli da se upišu u taj red. U tu svrhu služi najznačajnijih s - r bitova.

Слайд 48Asocijativno preslikavanje

Prevazilazi nedostatak direktnog preslikavanja, svaki blok može da se učita u

bilo koji red keša

Koristi asocijativnu memoriju (lokacija podatka definisana njegovim sadržajem, ne adresom)

Ovakve memorije nazivaju se i CAM (content addressible memory)

Слайд 49Set Asocijativno preslikavanje

Kompromis između direktnog i asocijatovnog preslikavanja

Keš memorija deli se na

skupove od po k elemenata

Preslikavanje na skupove direktno, preslikavanje u okviru samih skupova asocijativno

Слайд 50Politika upisivanja

Upisivanje se uvek vrši u memoriju, bez obzira da li je

došlo do pogotka keša (write through)

Upis u RAM loš aspekt, ali podaci su konzistentni između RAM i keš memorije (osim u slučaju multiprocesorskih sistema)

Alternativa je write back pristup, kada se podaci upisuju samo u keš. Upis u memoriju nije automatski. Podaci nekonzistentni, ali pristup brz.

Слайд 51Politika upisivanja

Ako drugi procesori ili komponente sistema imaju pristup glavnoj memoriji (npr.

DMA kontroler) u glavnoj memoriji može se promeniti podatak koji je u kešu neizmenjen. Stoga keš kontroler mora konstantno da nadgleda sve pristupe memoriji u cilju upisa, i markira odgovarajući sadržaj SRAM-a kao nekorektan (chache invalidation), ako se podatak u glavnoj memoriji menja.

Проект математический справочник _Наш город в числах_

Проект математический справочник _Наш город в числах_ Эта удивительная вода

Эта удивительная вода Служение подросткам в церкви и в мире

Служение подросткам в церкви и в мире Сервіси Web 2.0 Виконала учениця 11-Б Скрипець Марія Вчитель: Чабала Т.М.

Сервіси Web 2.0 Виконала учениця 11-Б Скрипець Марія Вчитель: Чабала Т.М. Особенности субъективных личностно-смысловых отношений у подростков с девиантным поведением

Особенности субъективных личностно-смысловых отношений у подростков с девиантным поведением Machine translation

Machine translation Разведение овец

Разведение овец Решения по уплотнению каналов в оптической среде передачи данных

Решения по уплотнению каналов в оптической среде передачи данных Основы вибродиагностики

Основы вибродиагностики Народный бюджет. Проведение уличного освещения в селе Арское

Народный бюджет. Проведение уличного освещения в селе Арское Оценка достижения планируемых результатов в начальной школе

Оценка достижения планируемых результатов в начальной школе Профилактика сердечно-сосудистых заболеваний

Профилактика сердечно-сосудистых заболеваний Электронная презентация Что я знаю о коррупции?

Электронная презентация Что я знаю о коррупции? Вершки и корешки

Вершки и корешки Декоративное цветоводство

Декоративное цветоводство Das Team, ohne das ich nicht leben kann! Spartakus

Das Team, ohne das ich nicht leben kann! Spartakus Поэма Сергея Александровича Есенина «Анна Снегина»

Поэма Сергея Александровича Есенина «Анна Снегина» Правилапротивопожарной безопасности

Правилапротивопожарной безопасности Занятость и безработица

Занятость и безработица Кафедра авиационной теплотехники и теплоэнергетики

Кафедра авиационной теплотехники и теплоэнергетики Презентация на тему Что такое дроби

Презентация на тему Что такое дроби  Проверочная работа по МХК 10 класс

Проверочная работа по МХК 10 класс Birds

Birds Презентация на тему Саграда Фамилия

Презентация на тему Саграда Фамилия Мой дом – моя крепость

Мой дом – моя крепость Федеральный закон О персональных данных

Федеральный закон О персональных данных Река Амур

Река Амур Власти Российской Федерации

Власти Российской Федерации