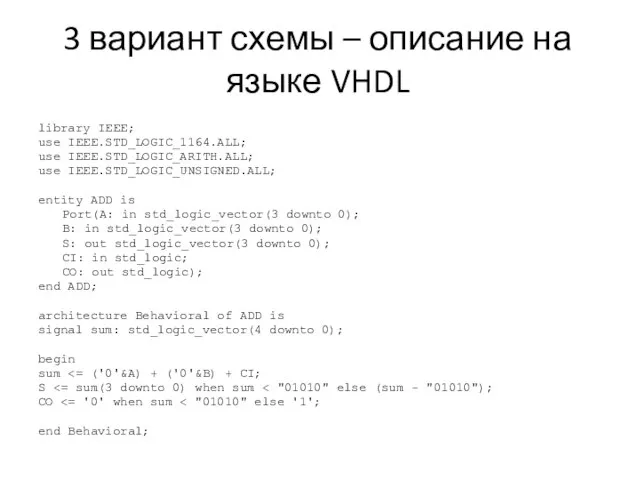

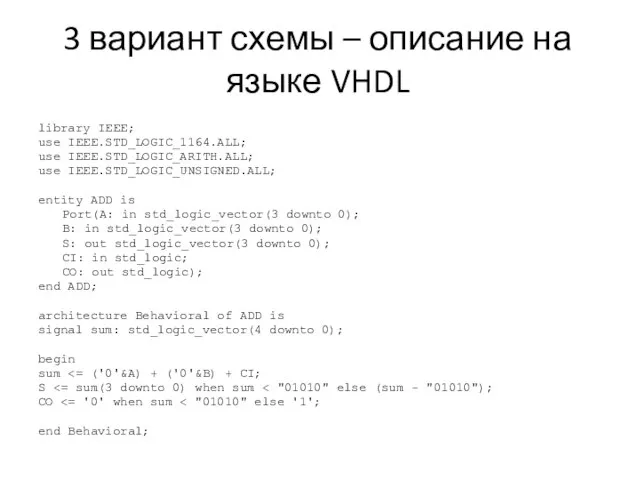

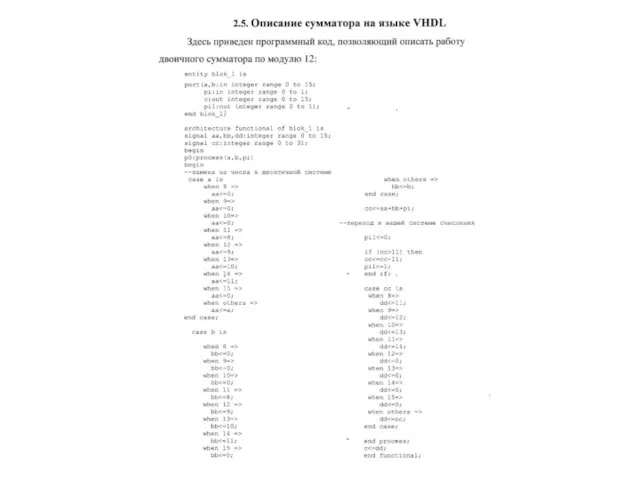

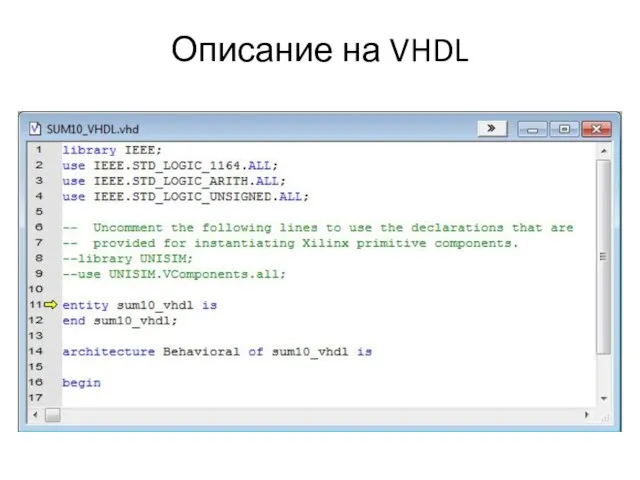

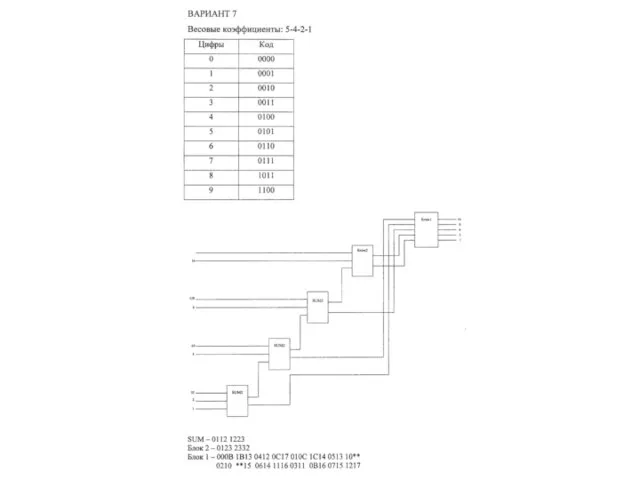

Слайд 113 вариант схемы – описание на языке VHDL

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity

ADD is

Port(A: in std_logic_vector(3 downto 0);

B: in std_logic_vector(3 downto 0);

S: out std_logic_vector(3 downto 0);

CI: in std_logic;

CO: out std_logic);

end ADD;

architecture Behavioral of ADD is

signal sum: std_logic_vector(4 downto 0);

begin

sum <= ('0'&A) + ('0'&B) + CI;

S <= sum(3 downto 0) when sum < "01010" else (sum - "01010");

CO <= '0' when sum < "01010" else '1';

end Behavioral;

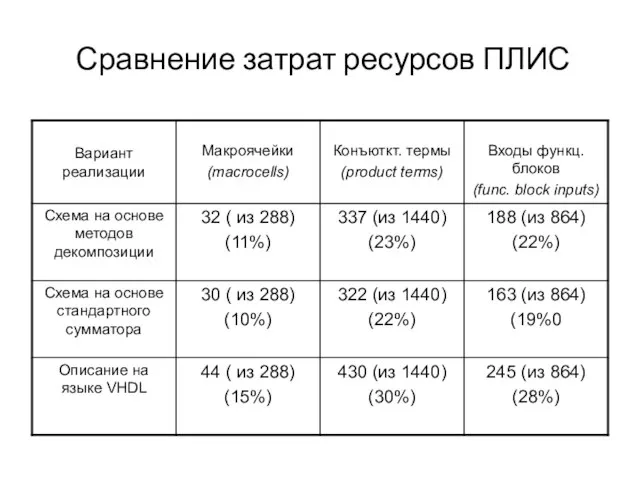

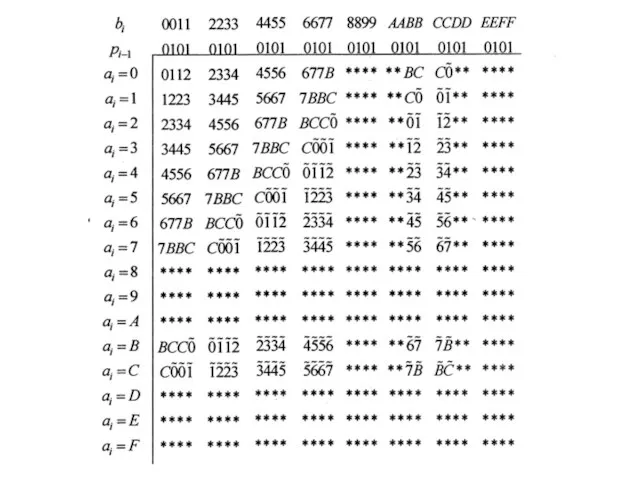

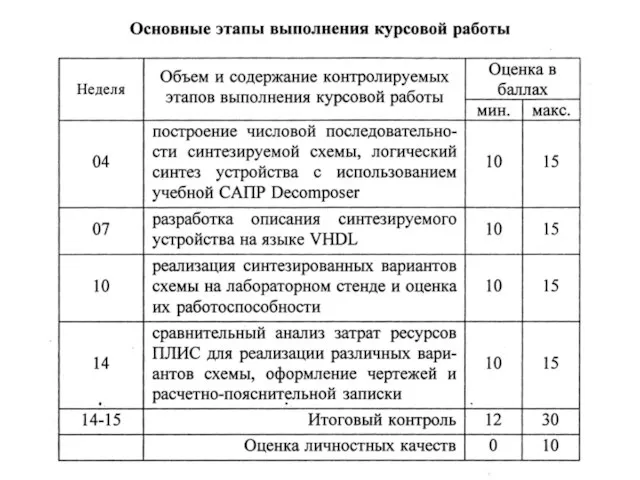

Слайд 14Можно получить несколько подобных таблиц:

для разных семейств ПЛИС:

- CPLD xc95288xl;

-

CPLD CoolRunner;

- FPGA Spartan3;

- для различных настроек

программы трассировки

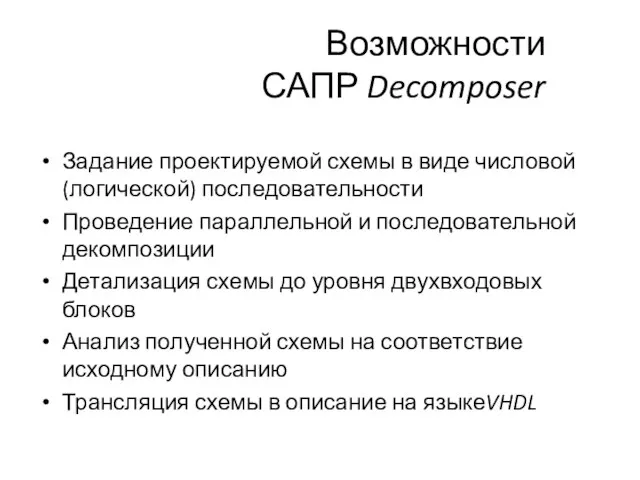

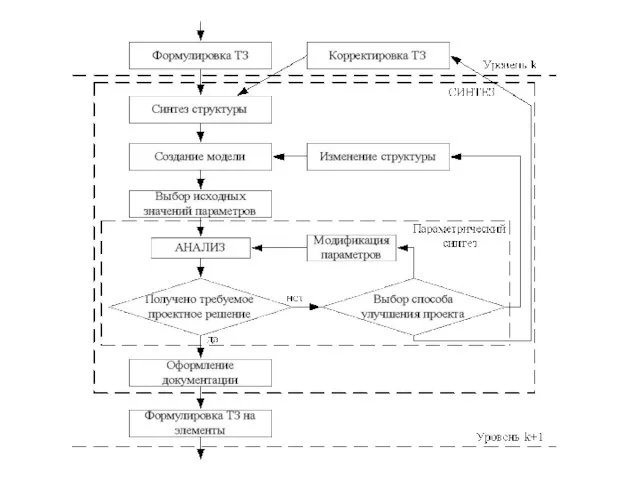

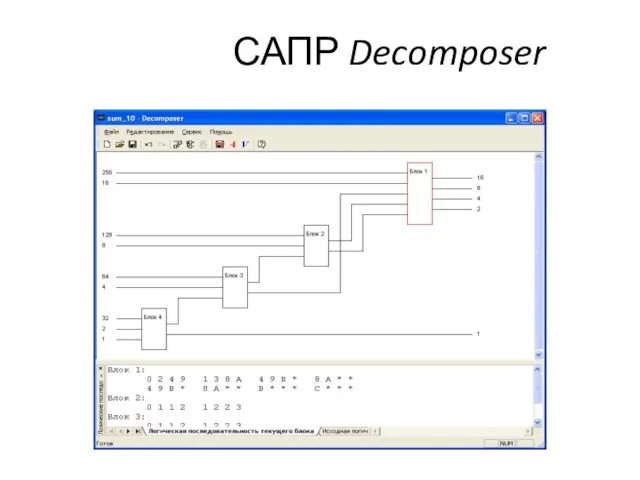

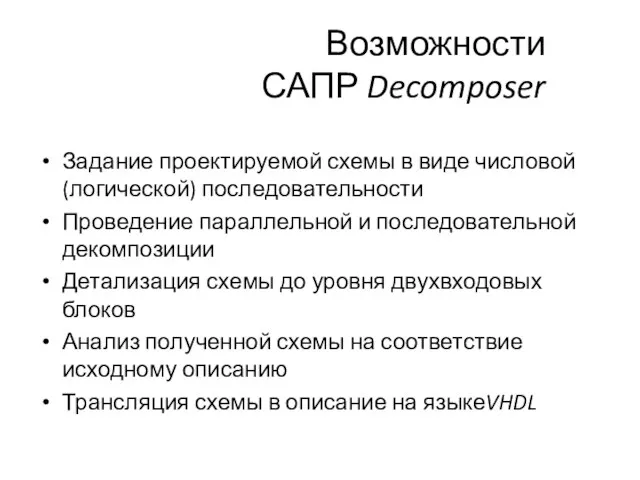

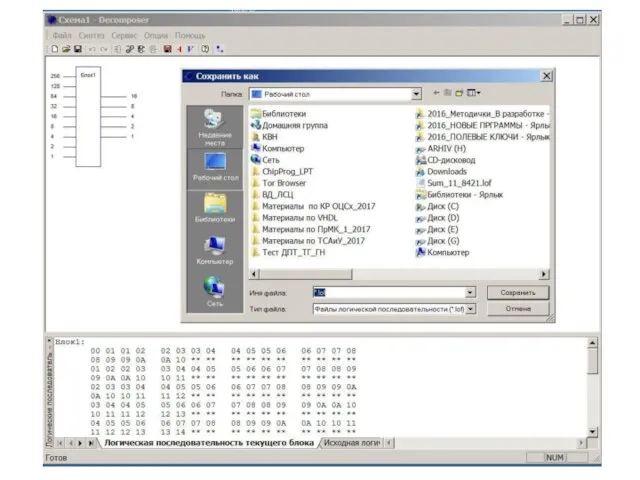

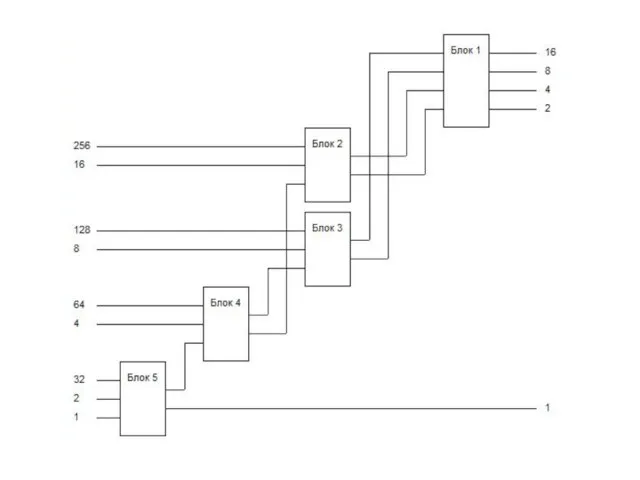

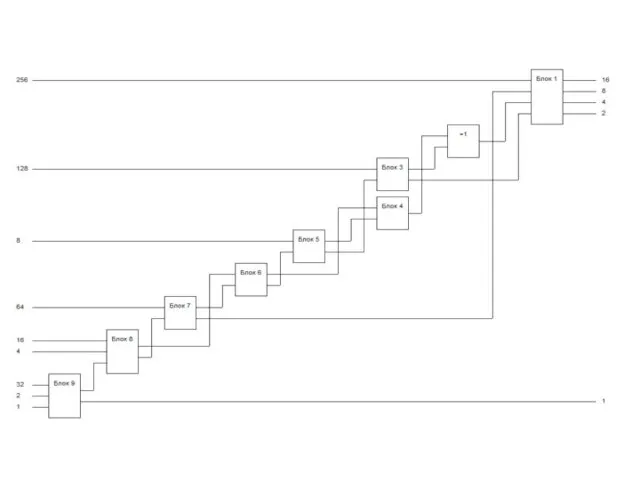

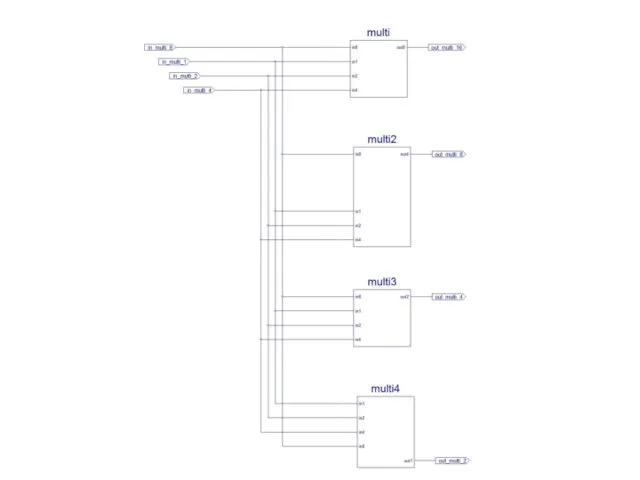

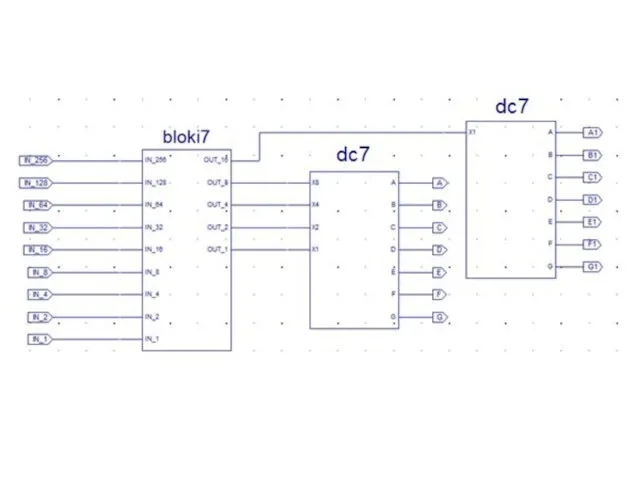

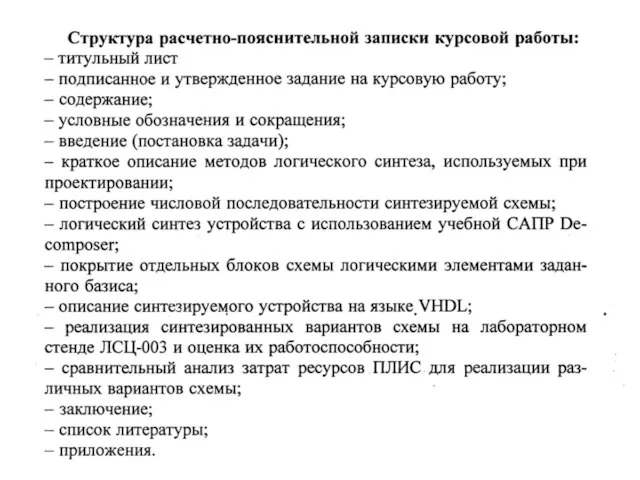

Слайд 16Возможности

САПР Decomposer

Задание проектируемой схемы в виде числовой (логической) последовательности

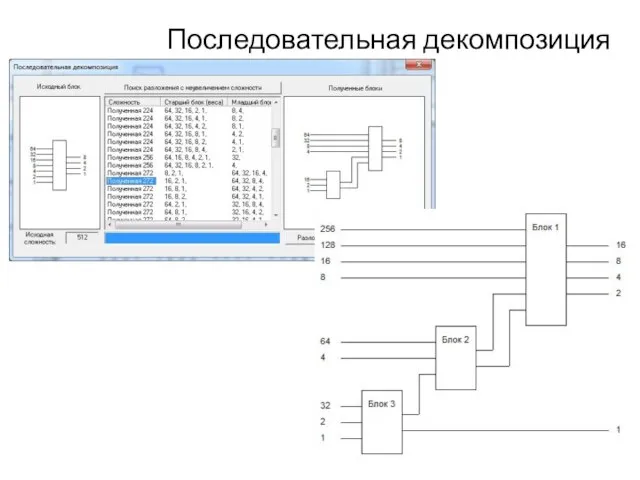

Проведение параллельной и последовательной

декомпозиции

Детализация схемы до уровня двухвходовых блоков

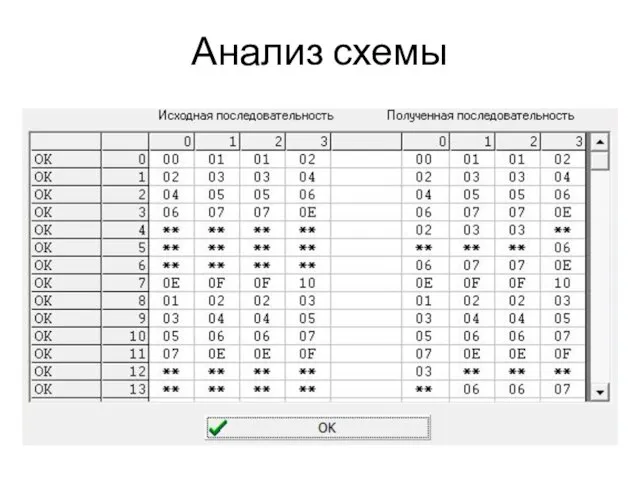

Анализ полученной схемы на соответствие исходному описанию

Трансляция схемы в описание на языкеVHDL

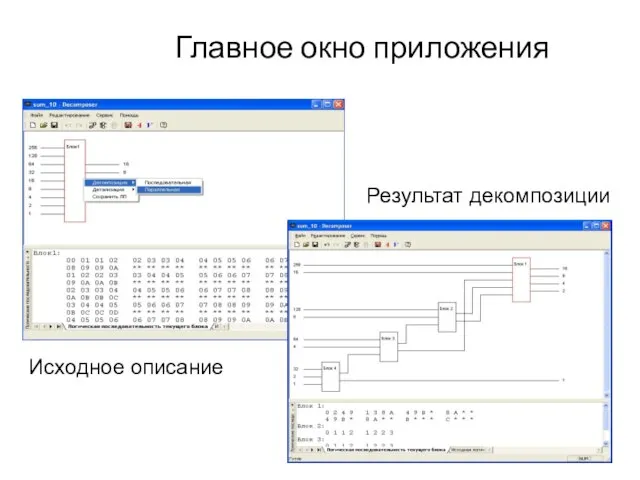

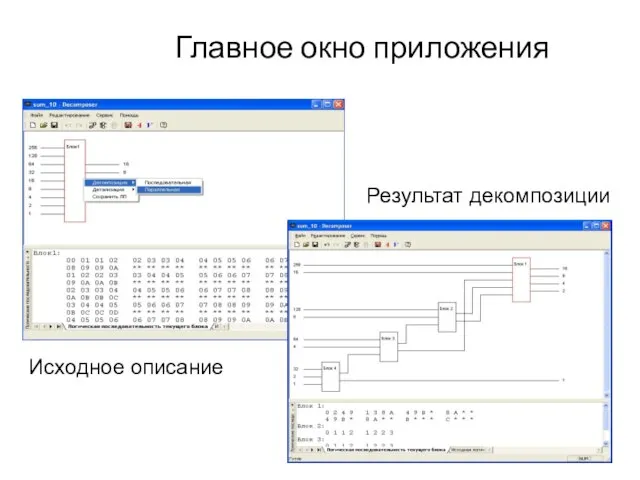

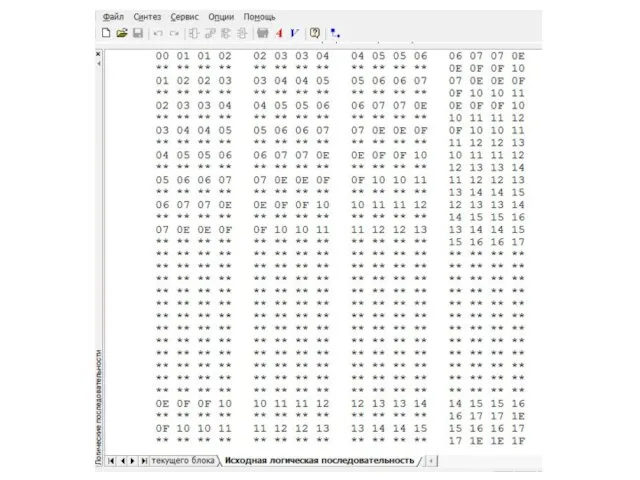

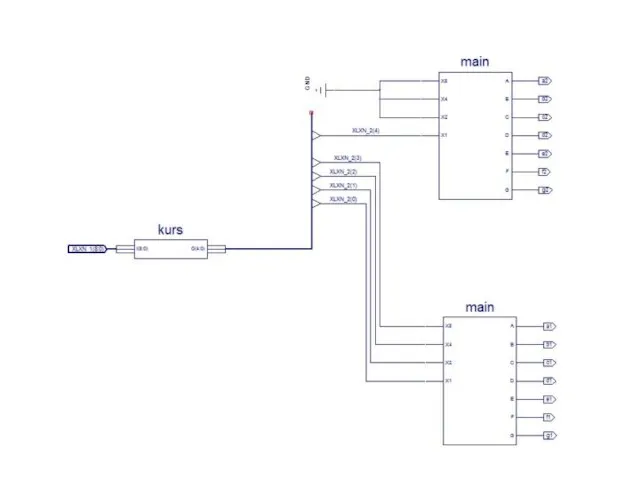

Слайд 17Главное окно приложения

Исходное описание

Результат декомпозиции

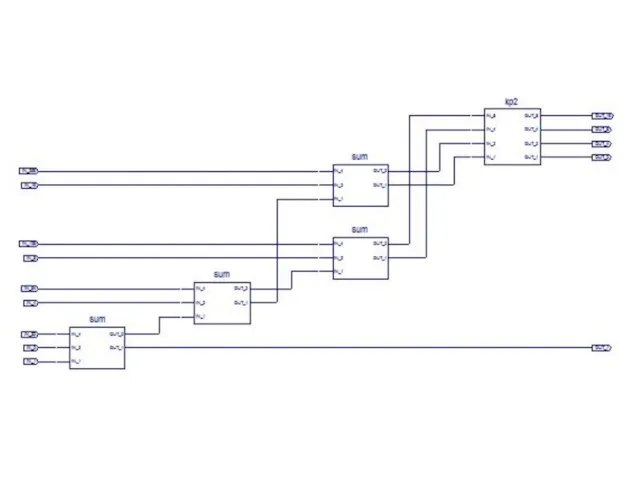

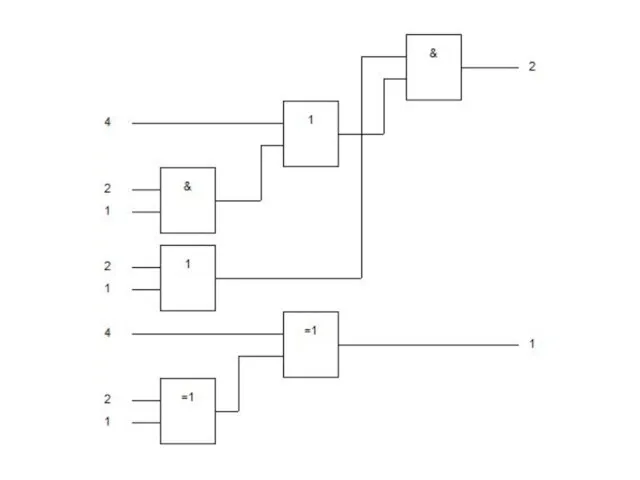

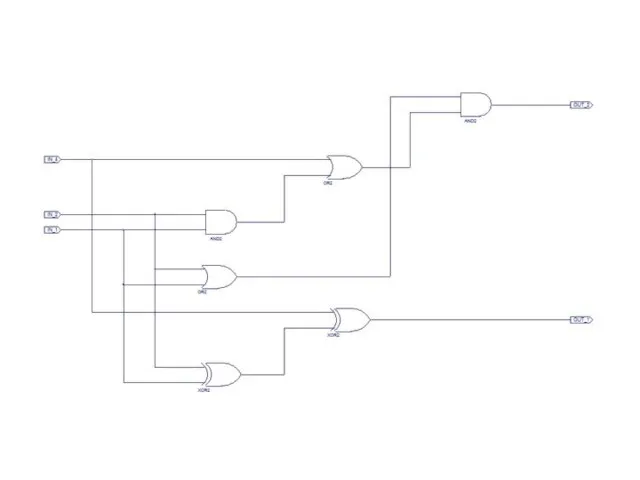

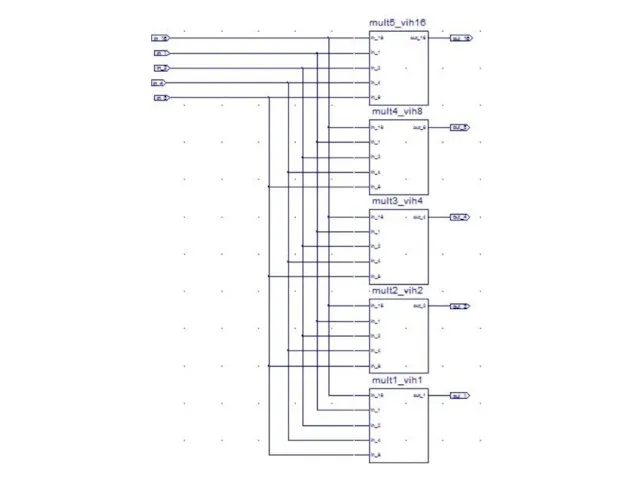

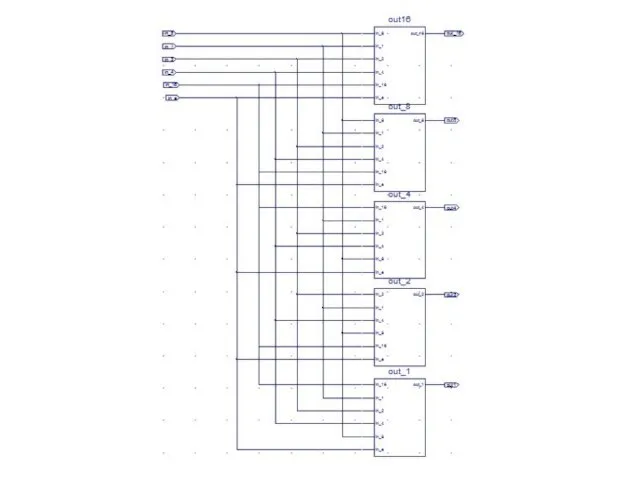

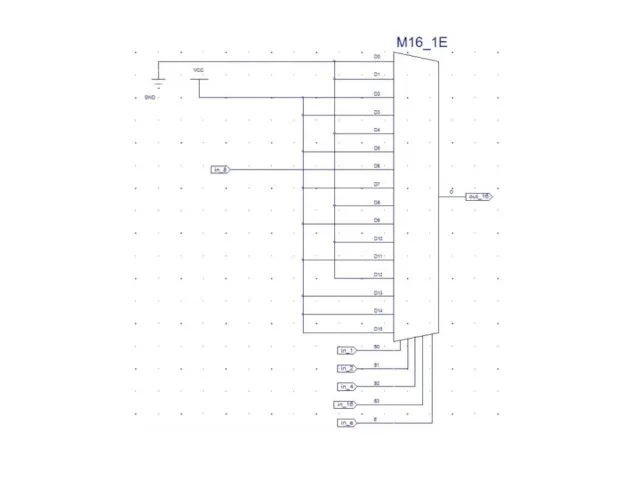

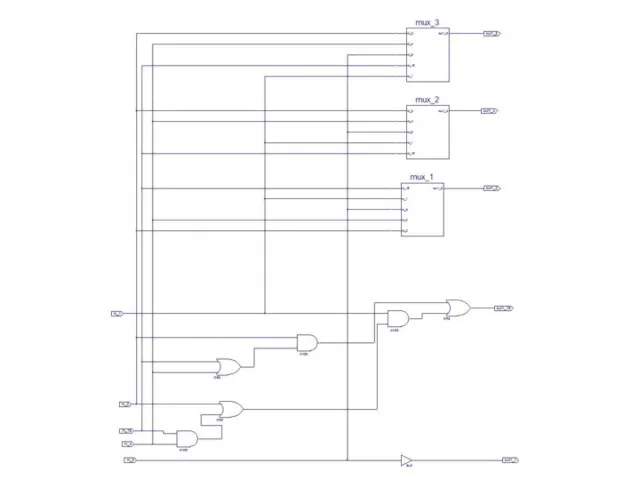

Слайд 28Детализация схемы и покрытие заданными логическими элементами

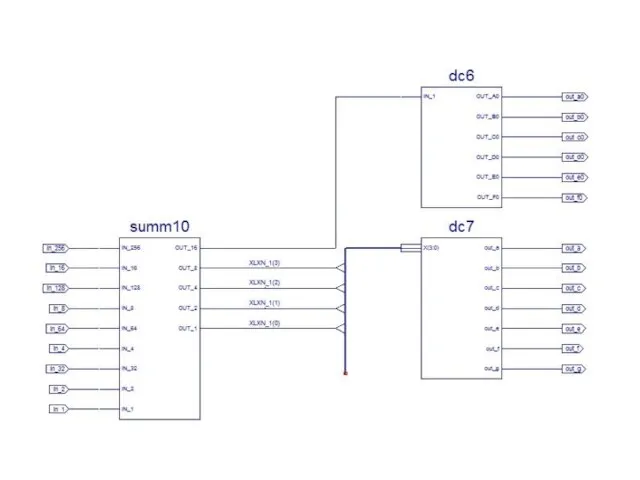

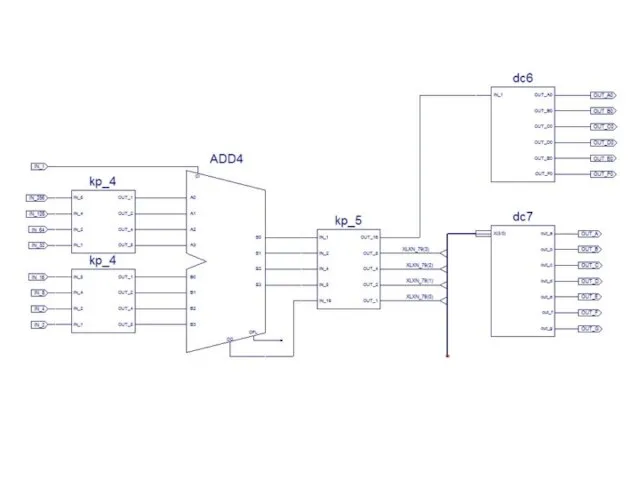

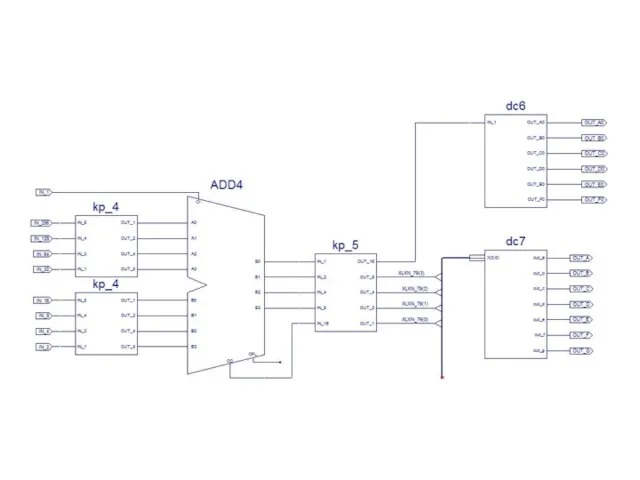

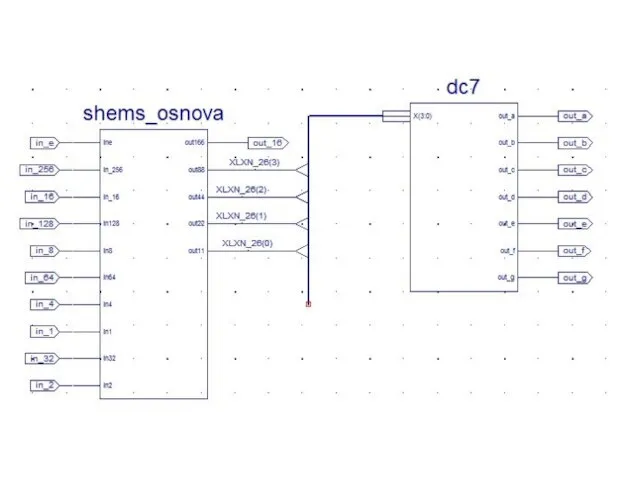

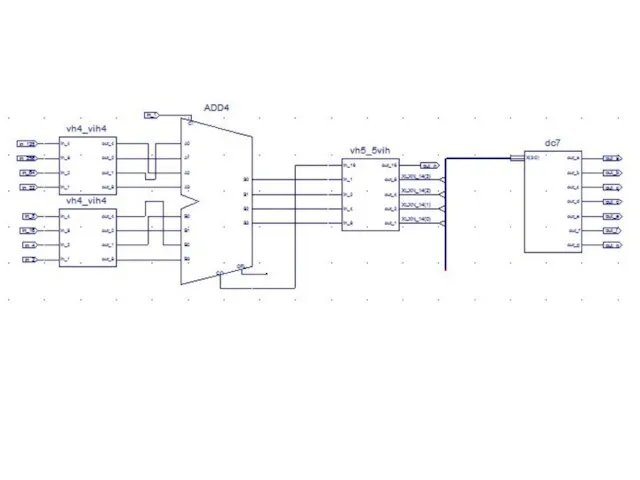

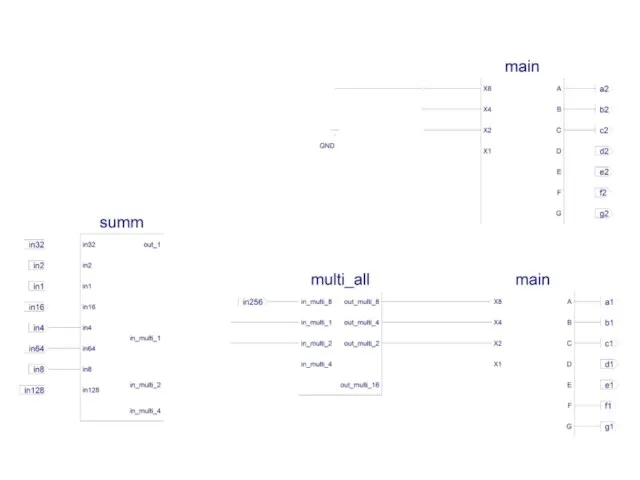

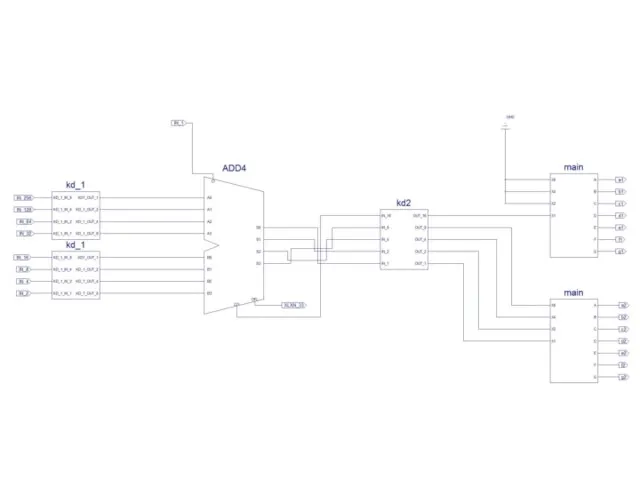

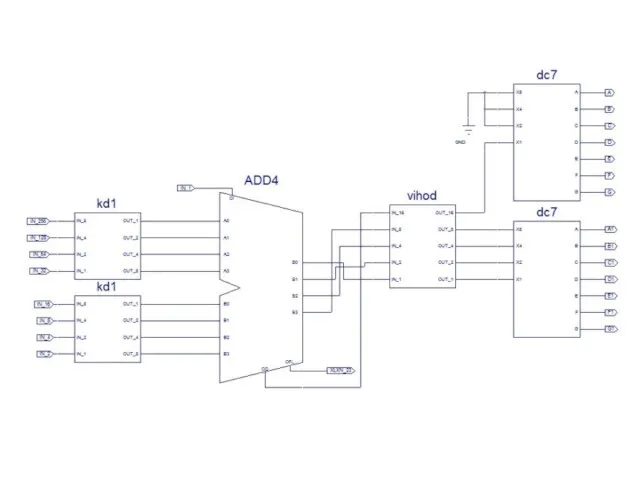

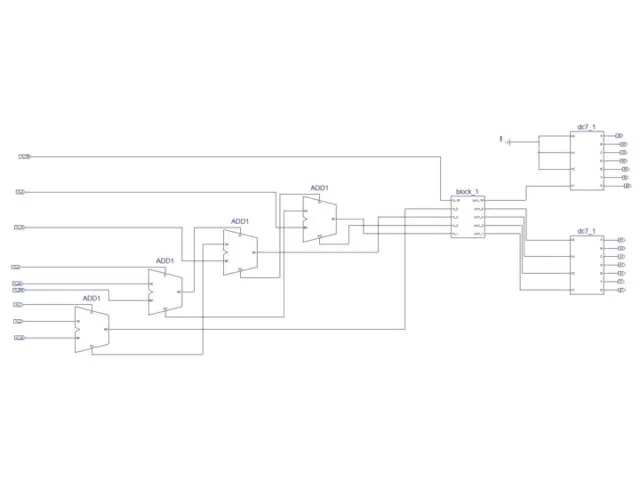

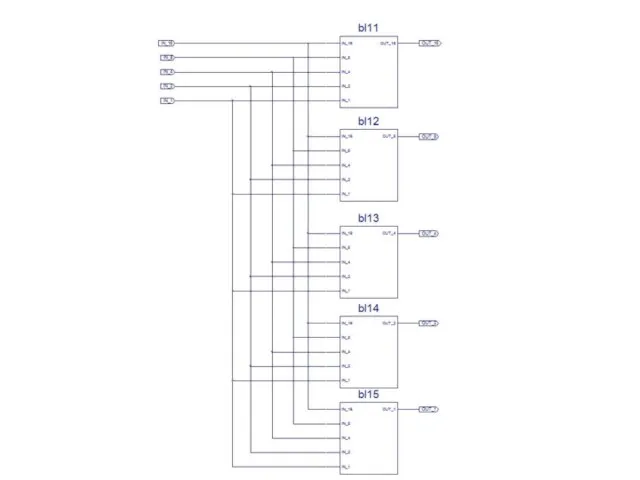

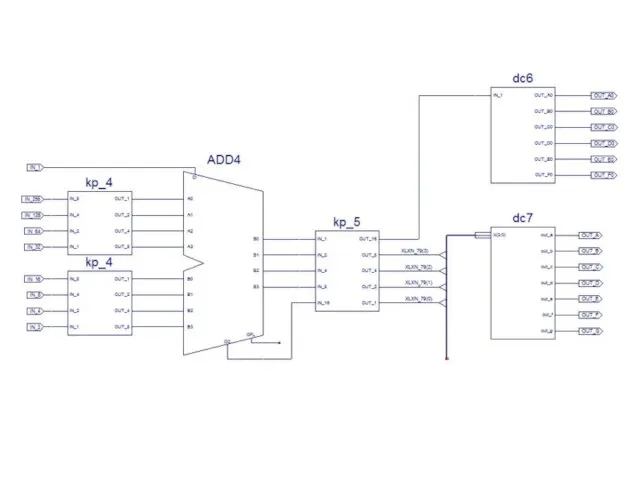

Слайд 312 вариант схемы:

на основе стандартного четырехразрядного сумматора и входных/выходных кодопреобразователей

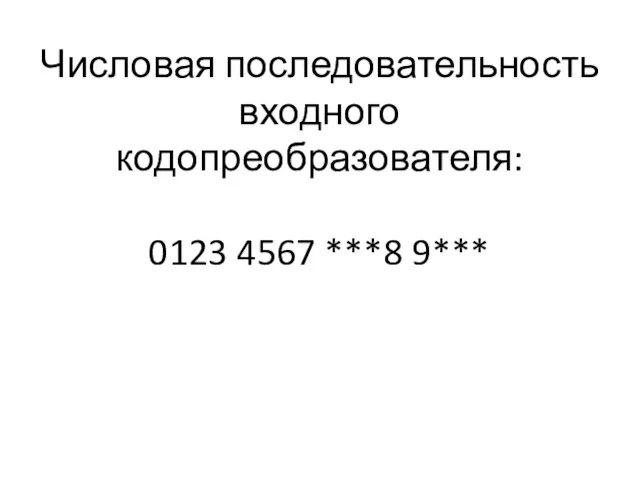

Слайд 32Числовая последовательность входного кодопреобразователя:

0123 4567 ***8 9***

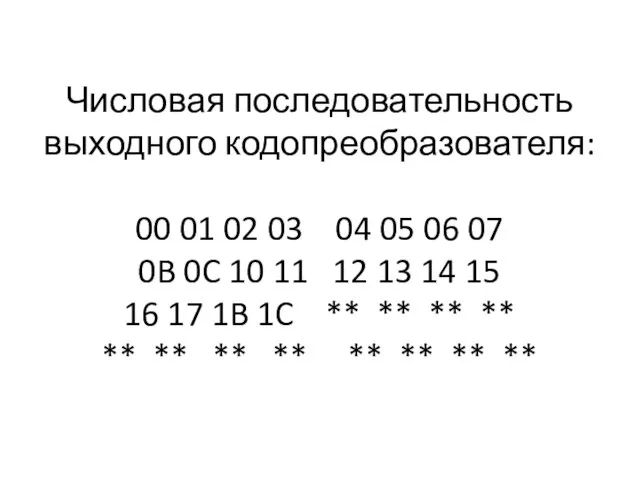

Слайд 33Числовая последовательность выходного кодопреобразователя:

00 01 02 03 04 05 06 07

0B 0C

10 11 12 13 14 15

16 17 1B 1C ** ** ** **

** ** ** ** ** ** ** **

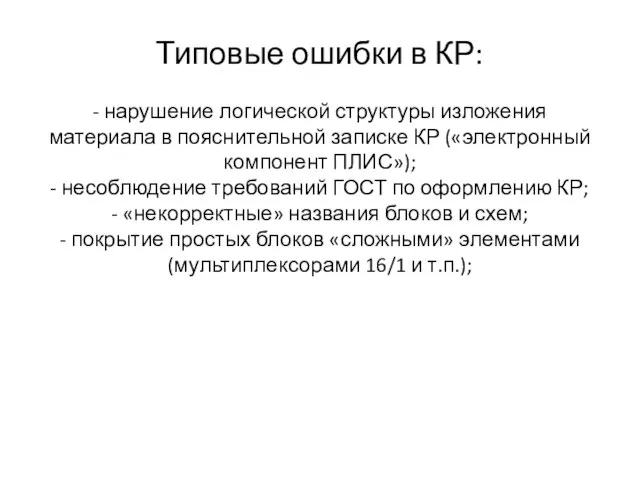

Слайд 36Типовые ошибки в КР:

- нарушение логической структуры изложения материала в пояснительной записке

КР («электронный компонент ПЛИС»);

- несоблюдение требований ГОСТ по оформлению КР;

- «некорректные» названия блоков и схем;

- покрытие простых блоков «сложными» элементами (мультиплексорами 16/1 и т.п.);

Инструкция для входа в вэбинарную комнату WebEx

Инструкция для входа в вэбинарную комнату WebEx Представление информации в двоичной системе мсчисления

Представление информации в двоичной системе мсчисления Как подать обращение через сайт ГИС ЖКХ

Как подать обращение через сайт ГИС ЖКХ Программирование на языке Паскаль. Часть II

Программирование на языке Паскаль. Часть II Кодирование символов

Кодирование символов Трехмерный анализ данных

Трехмерный анализ данных Информационная безопасность в компьютерных сетях Криптографическая система шифрования

Информационная безопасность в компьютерных сетях Криптографическая система шифрования Изучение графического редактора Paint.Net. 7 класс

Изучение графического редактора Paint.Net. 7 класс Технологии физического уровня (L1)

Технологии физического уровня (L1) Хеширование паролей. Лекция №6

Хеширование паролей. Лекция №6 Кладовка smm-щика

Кладовка smm-щика Язык разметки гипертекста HTML

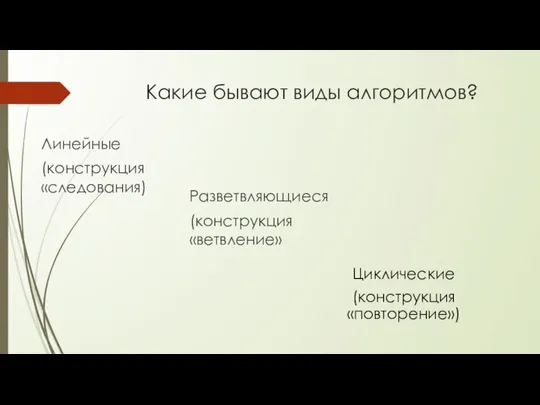

Язык разметки гипертекста HTML Виды алгоритмов

Виды алгоритмов The Fuehrer's Fate. Компьютерная игра

The Fuehrer's Fate. Компьютерная игра Формализация: Понятие формализации, основные формы формализации информации: формула, текст, таблица, граф, алгоритм. СРС

Формализация: Понятие формализации, основные формы формализации информации: формула, текст, таблица, граф, алгоритм. СРС Алгоритм и его свойства

Алгоритм и его свойства Работы Цыпляковой Н.А. в CorelDraw, Photoshop, AutoCAD & Marvelous

Работы Цыпляковой Н.А. в CorelDraw, Photoshop, AutoCAD & Marvelous Функциональное программирование

Функциональное программирование Отчет в рамках исполнения работ по государственному контракту на оказание услуг, выполнение работ

Отчет в рамках исполнения работ по государственному контракту на оказание услуг, выполнение работ Возможности электронных таблиц

Возможности электронных таблиц İntellektual sistemlər

İntellektual sistemlər Операционные системы для разработчиков программного обеспечения. (Лекция 2)

Операционные системы для разработчиков программного обеспечения. (Лекция 2) Основы построения системы управления базами данных MS ACCESS

Основы построения системы управления базами данных MS ACCESS Микроконтроллеры

Микроконтроллеры Там3

Там3 Электронный документооборот

Электронный документооборот E-Invoicing и PayByClick – удобный способ принимать оплату в интернете

E-Invoicing и PayByClick – удобный способ принимать оплату в интернете Структурное программирование

Структурное программирование