Слайд 2Александр Силантьев

Руководитель лаборатории ЦКП МИЭТ

Окончил МИЭТ в 2014 году

12 летний опыт инженерной

деятельности

Старший преподаватель института МПСУ МИЭТ.

Организатор первого в России инженерного хакатона по микроэлектронике и системам на кристалле.

С 2014 года организатор семинаров, школ и олимпиад по популяризации электроники среди студентов и школьников

Слайд 3Микросхемы малой степени интеграции

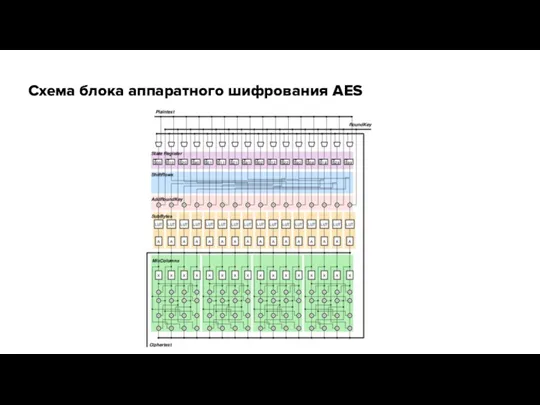

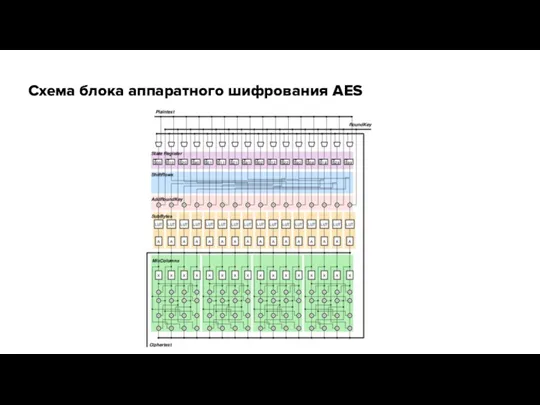

Слайд 6Схема блока аппаратного шифрования AES

Слайд 7Управление сложностью в микроэлектронике

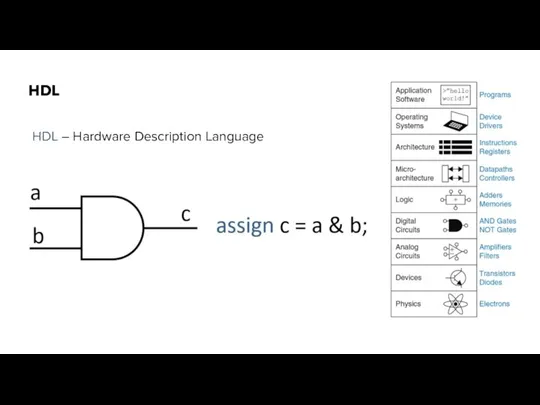

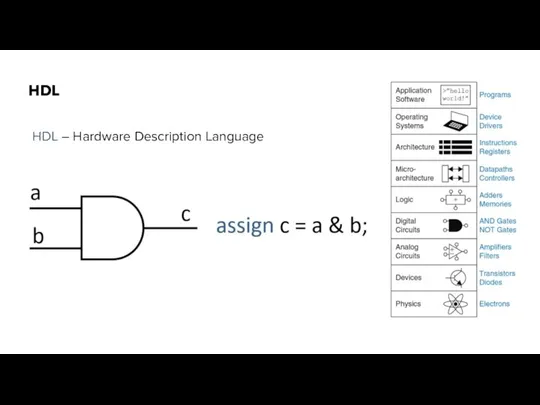

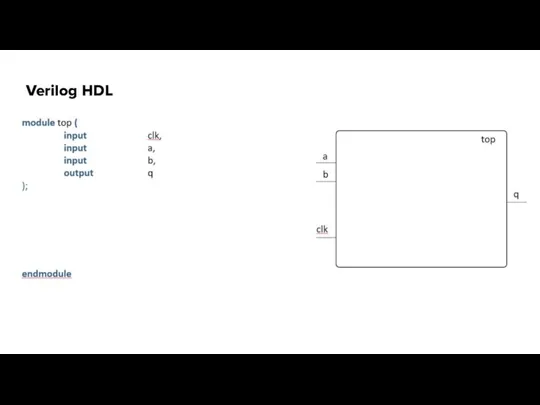

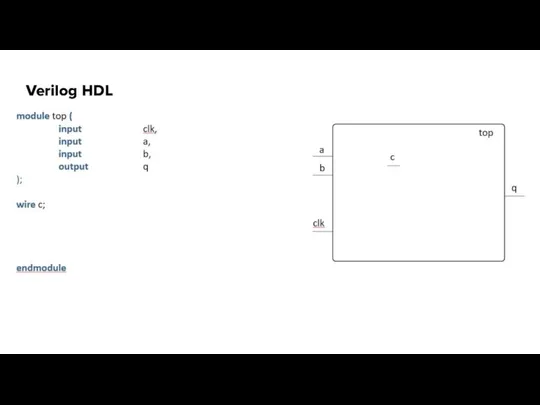

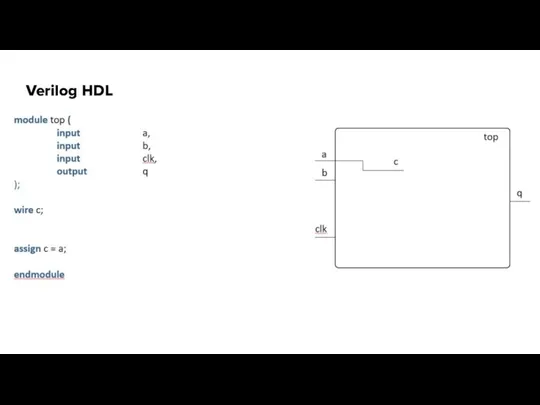

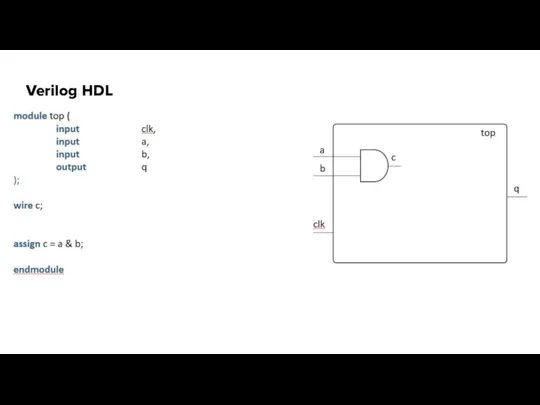

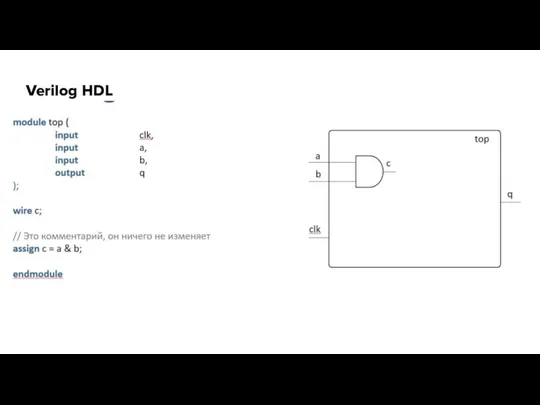

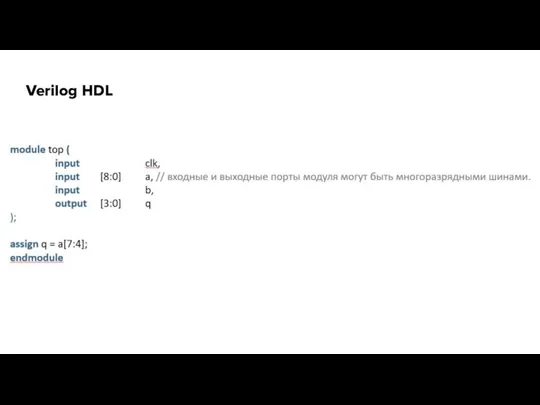

Слайд 8HDL

HDL – Hardware Description Language

Слайд 10Verilog HDL. История

Verilog был разработан компанией Gateway Design Automation в 1984 году

как фирменный язык для симуляции логических схем.

В 1989 году Gateway приобрела компания Cadence, и Verilog стал открытым стандартом в 1990 году под управлением сообщества Open Verilog International.

Язык стал стандартом IEEE в 1995 году.

В 2005 году язык был расширен для упорядочивания и лучшей поддержки моделирования и верификации систем.

Эти расширения были объединены в единый стандарт, который сейчас называется SystemVerilog(стандарт IEEE 1800-2009).

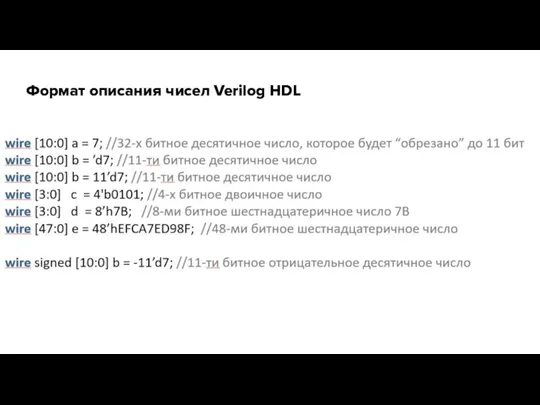

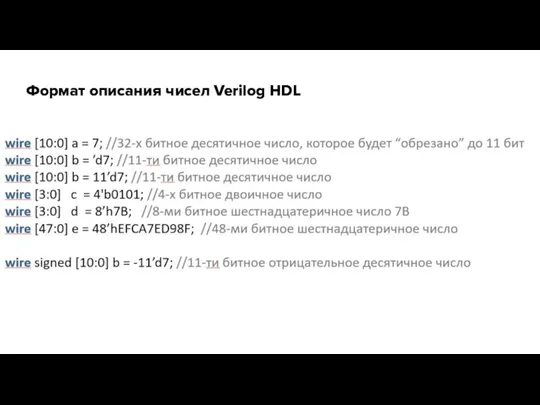

Слайд 28Формат описания чисел Verilog HDL

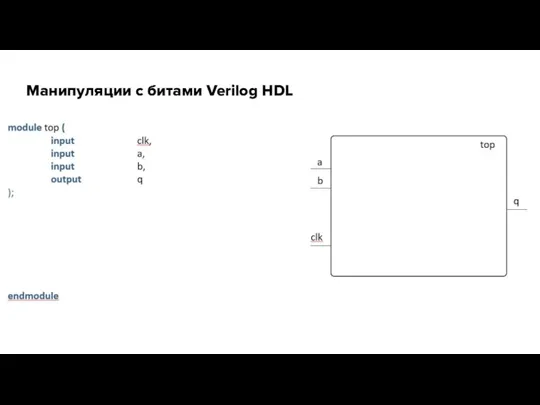

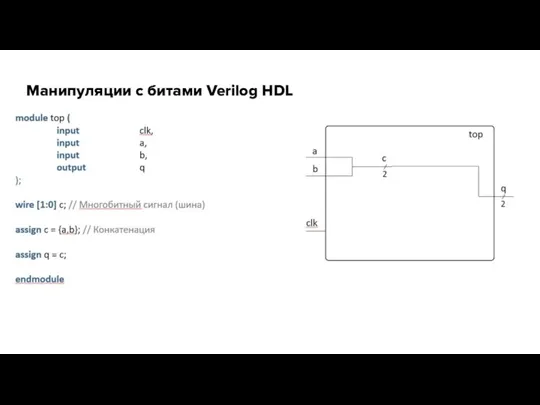

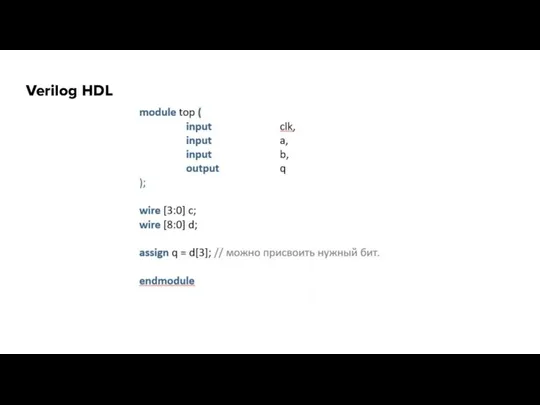

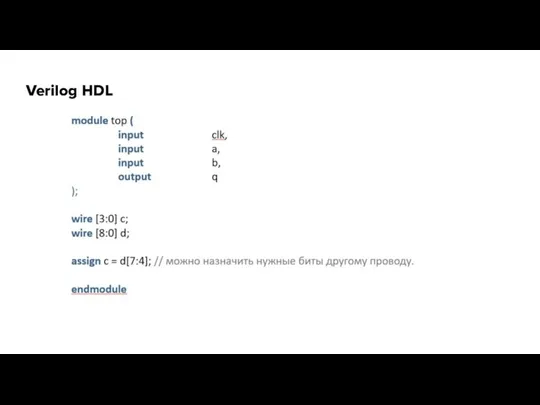

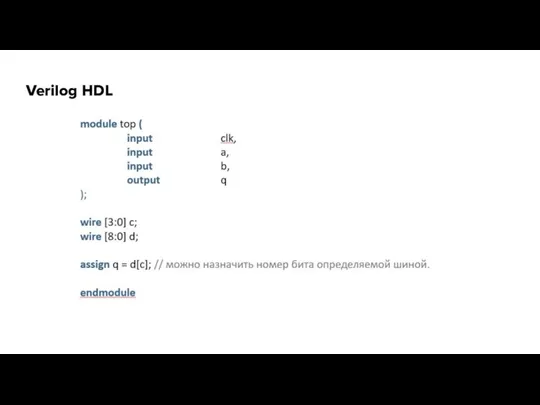

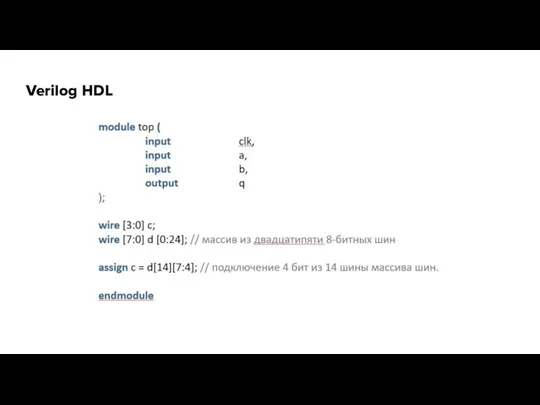

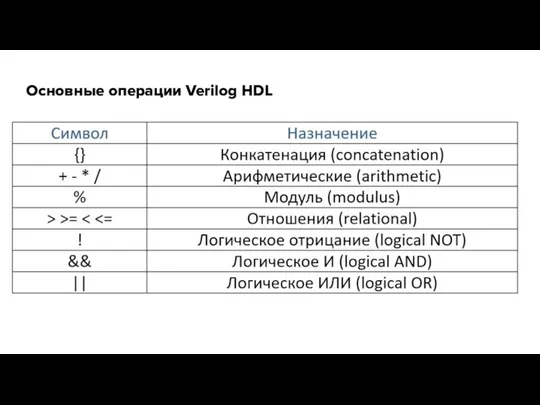

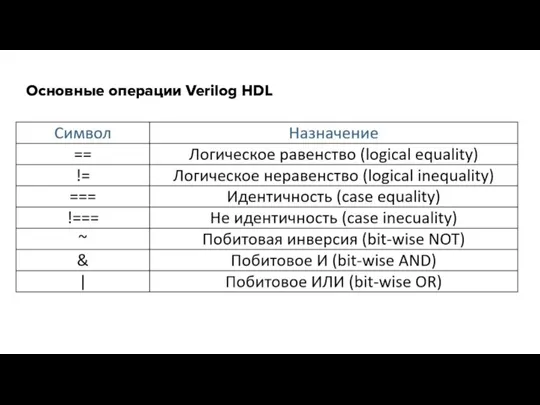

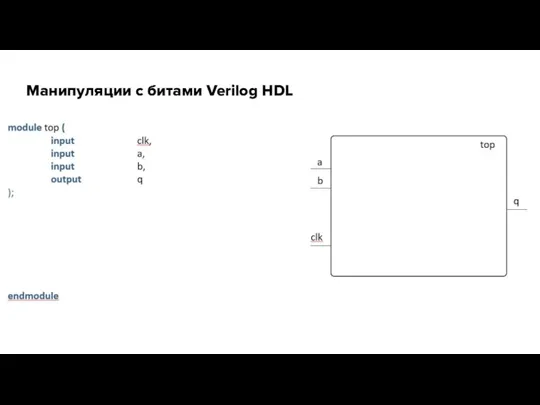

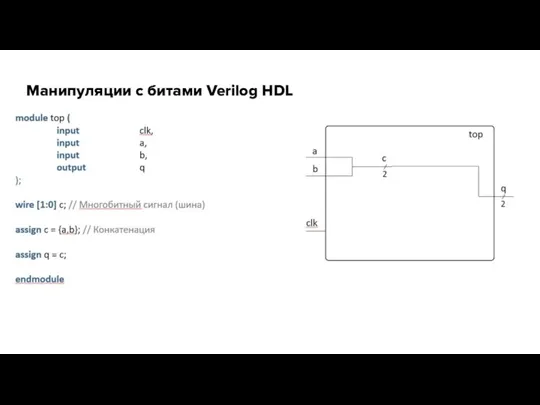

Слайд 32Манипуляции с битами Verilog HDL

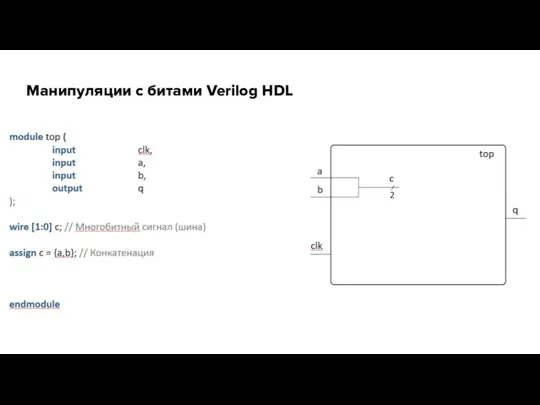

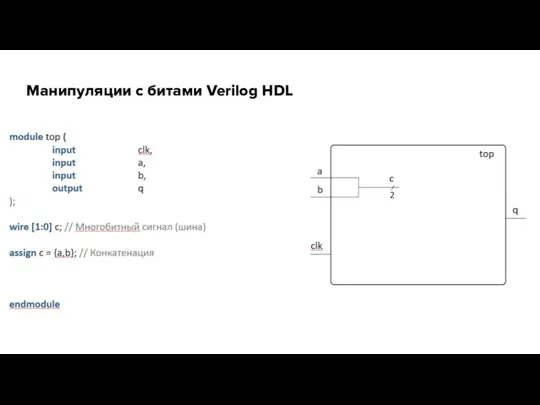

Слайд 33Манипуляции с битами Verilog HDL

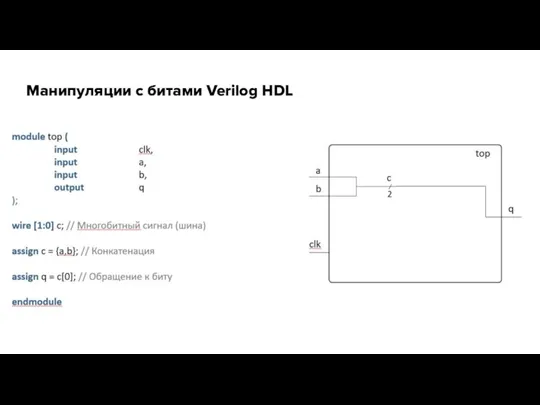

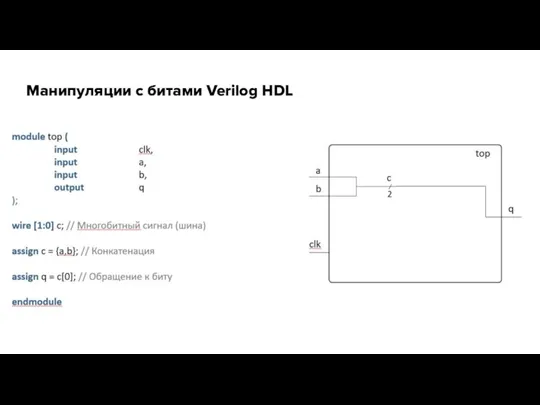

Слайд 34Манипуляции с битами Verilog HDL

Слайд 35Манипуляции с битами Verilog HDL

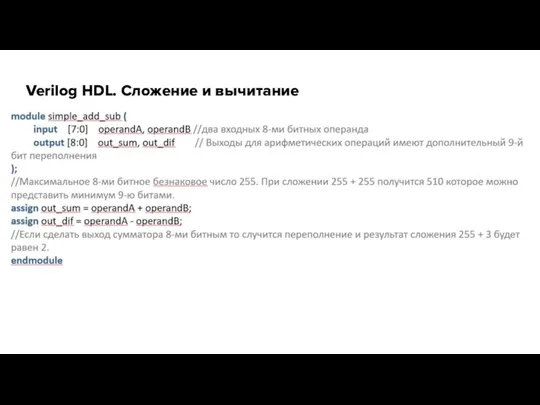

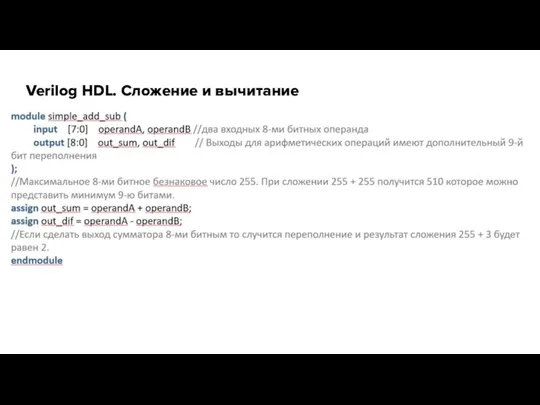

Слайд 36Verilog HDL. Сложение и вычитание

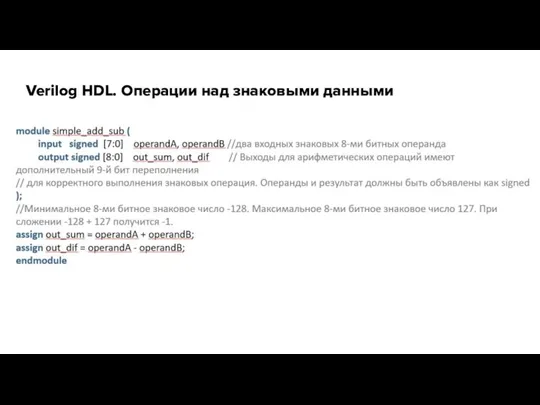

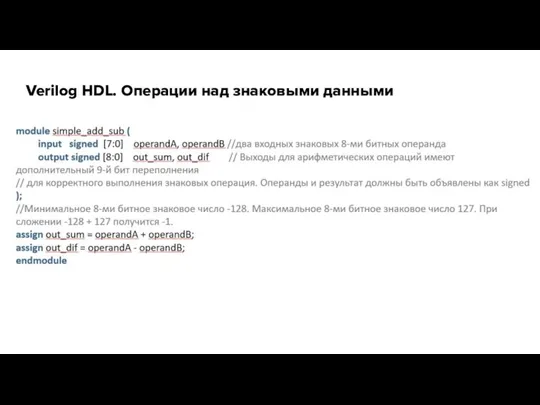

Слайд 37Verilog HDL. Операции над знаковыми данными

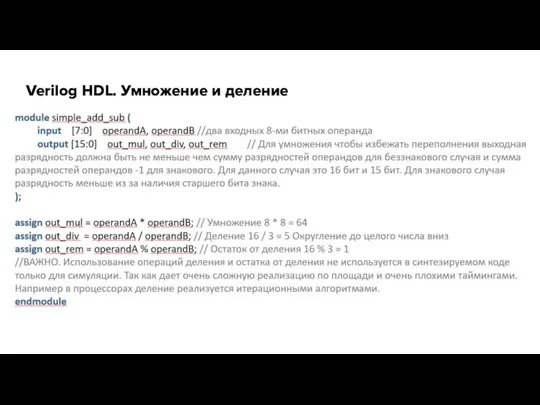

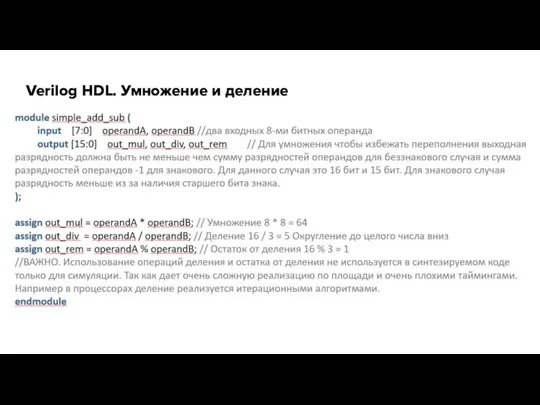

Слайд 38Verilog HDL. Умножение и деление

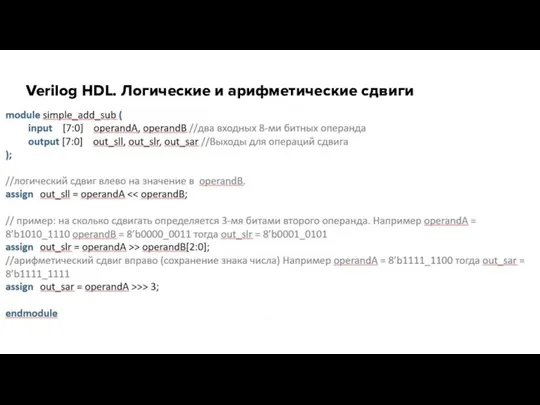

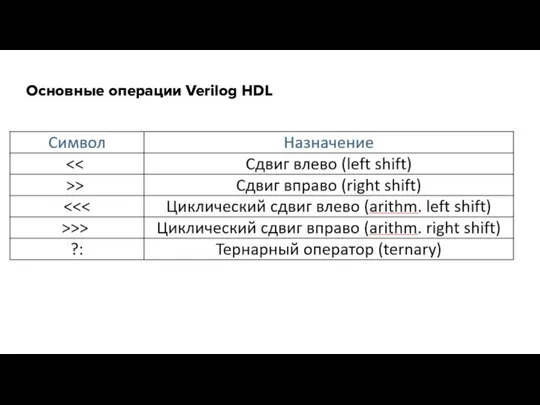

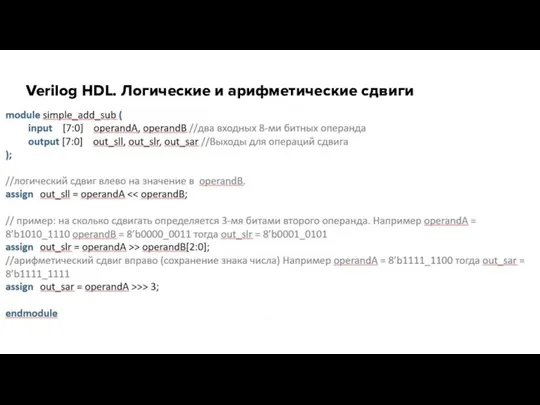

Слайд 39Verilog HDL. Логические и арифметические сдвиги

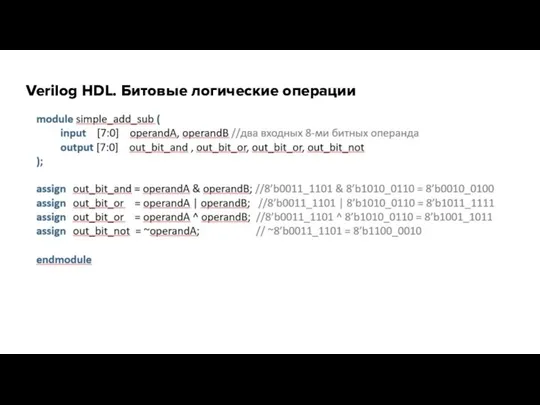

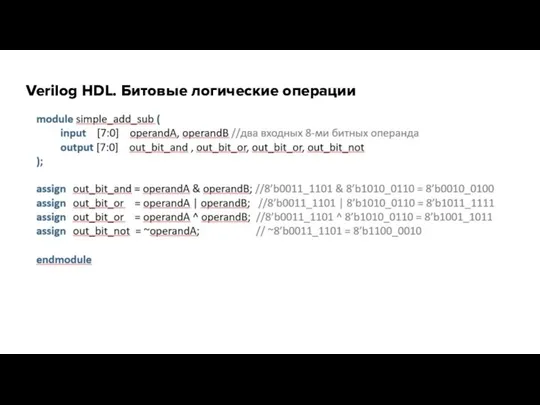

Слайд 40Verilog HDL. Битовые логические операции

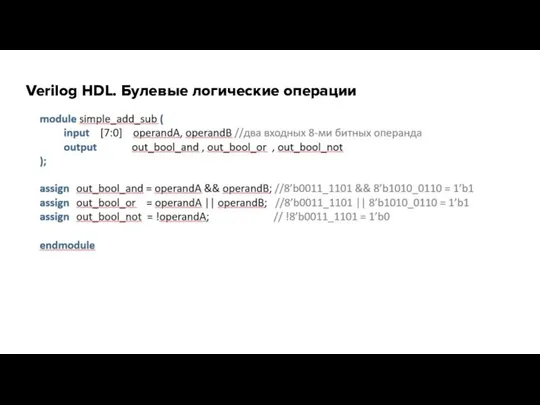

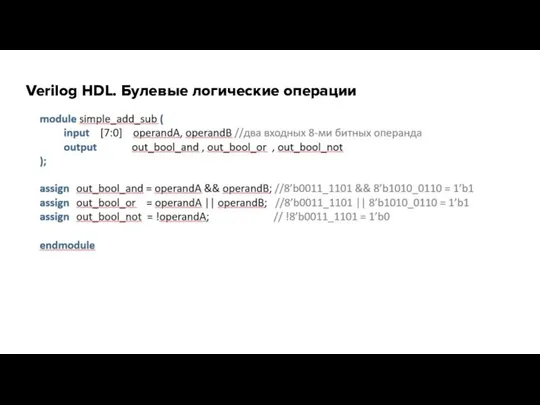

Слайд 41Verilog HDL. Булевые логические операции

Слайд 55Симуляция. Инструменты для задания

Бесплатный симулятор Icarus Verilog, который хотя и не поддерживает

весь SystemVerilog, но поддерживает Verilog 2005 с некоторыми элементами SystemVerilog, достаточных для решения наших задач.

GTKWave, программой для работы с временными диаграммами. Для первых десяти задач GTKWave нам не понадобится, но его стоит установить вместе с Icarus Verilog на будущее.

Слайд 56Icarus Verilog

Icarus Verilog – среда для поведенческого моделирования цифровых схем, описанных на

языке Verilog;

Icarus Verilog – свободное (открытое) и кроссплатформенное ПО;

Icarus Verilog – инструмент командной строки (не имеет графического интерфейса пользователя).

Слайд 57Icarus Verilog. Установка

Под Linux Icarus Verilog и GTKWave ставится "sudo apt-get install

verilog gtkwave".

Версия Icarus Verilog и GTKWave для Windows здесь.

Важно! При установке выставить флаг о добавлении Icarus в path Windows.

Если у вас под Windows что-то не работает, проверьте, какие директории стоят у вас в path.

Установка в консоли с помощью программы brew: brew install icarus-verilog.

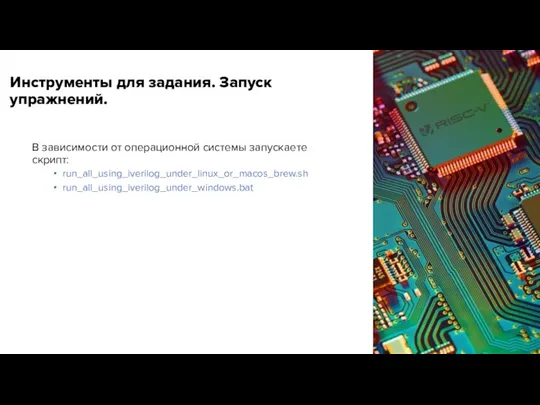

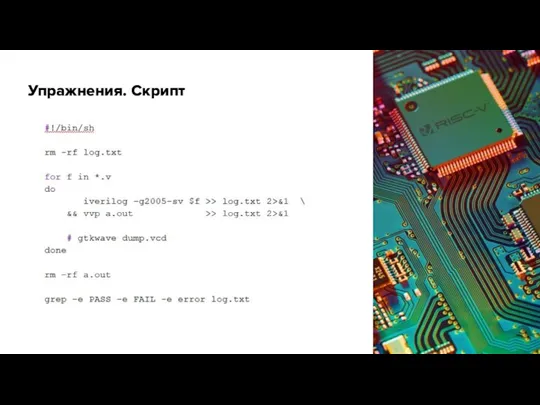

Слайд 58Инструменты для задания. Запуск упражнений.

В зависимости от операционной системы запускаете скрипт:

run_all_using_iverilog_under_linux_or_macos_brew.sh

run_all_using_iverilog_under_windows.bat

Слайд 60Среда тестирования

Среда тестирования (testbench) – это модуль на HDL, который используется для

тестирования другого модуля, называемого тестируемое устройство (device under test, DUT). (Некоторые программы разработки называют тестируемый модуль unit under test, UUT.)

Среда тестирования содержит операторы для генерации значений, подаваемых на входы DUT и, в идеале, также и для проверки, что на выходе получаются правильные значения.

Наборы входных и желаемых выходных значений называются тестовыми векторами.

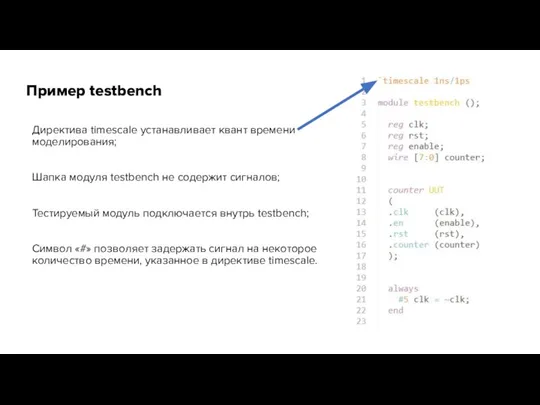

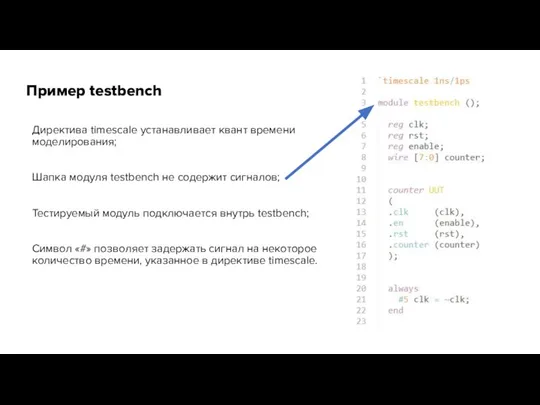

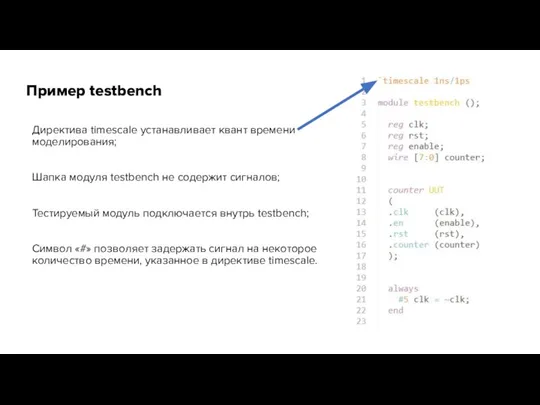

Слайд 61Пример testbench

Директива timescale устанавливает квант времени моделирования;

Шапка модуля testbench не содержит сигналов;

Тестируемый

модуль подключается внутрь testbench;

Символ «#» позволяет задержать сигнал на некоторое количество времени, указанное в директиве timescale.

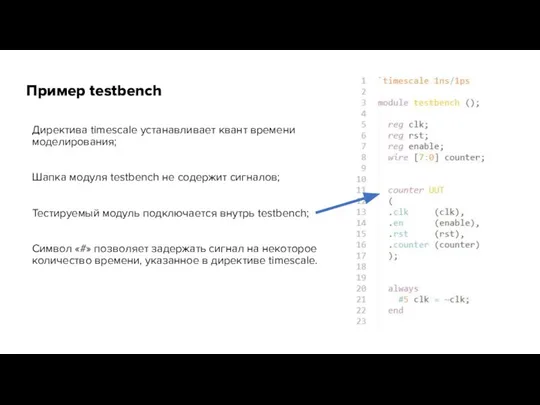

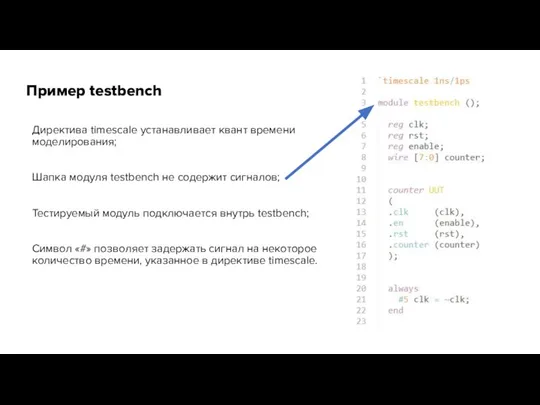

Слайд 62Пример testbench

Директива timescale устанавливает квант времени моделирования;

Шапка модуля testbench не содержит сигналов;

Тестируемый

модуль подключается внутрь testbench;

Символ «#» позволяет задержать сигнал на некоторое количество времени, указанное в директиве timescale.

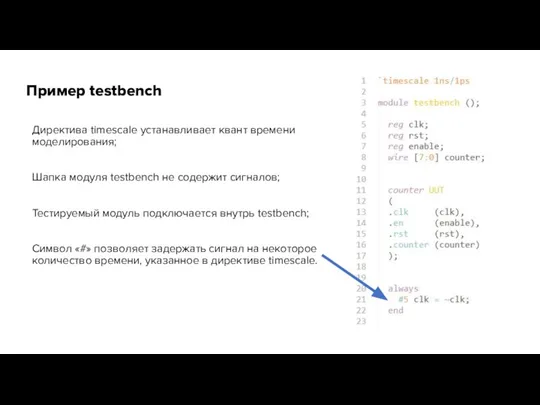

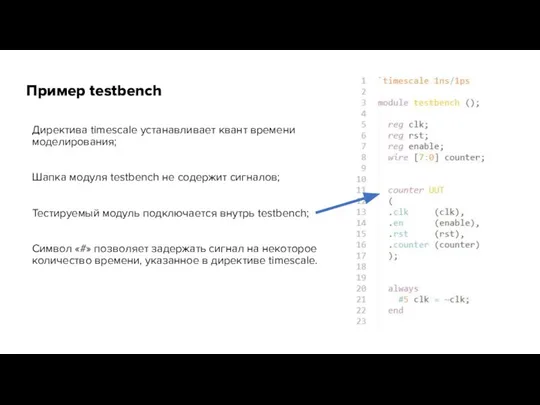

Слайд 63Пример testbench

Директива timescale устанавливает квант времени моделирования;

Шапка модуля testbench не содержит сигналов;

Тестируемый

модуль подключается внутрь testbench;

Символ «#» позволяет задержать сигнал на некоторое количество времени, указанное в директиве timescale.

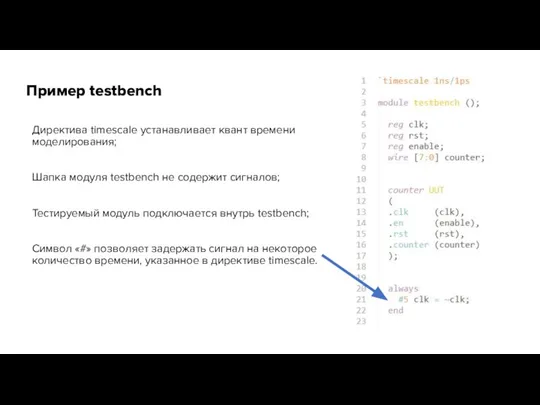

Слайд 64Пример testbench

Директива timescale устанавливает квант времени моделирования;

Шапка модуля testbench не содержит сигналов;

Тестируемый

модуль подключается внутрь testbench;

Символ «#» позволяет задержать сигнал на некоторое количество времени, указанное в директиве timescale.

Слайд 65Пример testbench

Директива timescale устанавливает квант времени моделирования;

Шапка модуля testbench не содержит сигналов;

Тестируемый

модуль подключается внутрь testbench;

Символ «#» позволяет задержать сигнал на некоторое количество времени, указанное в директиве timescale.

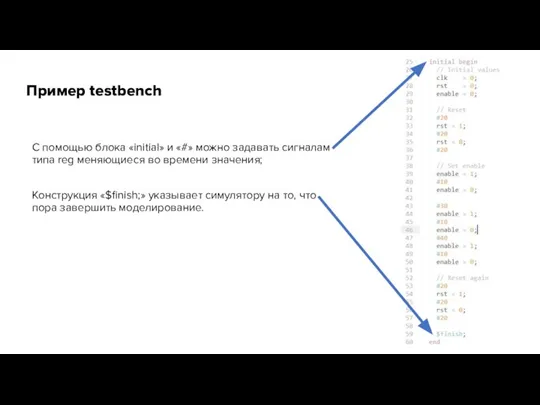

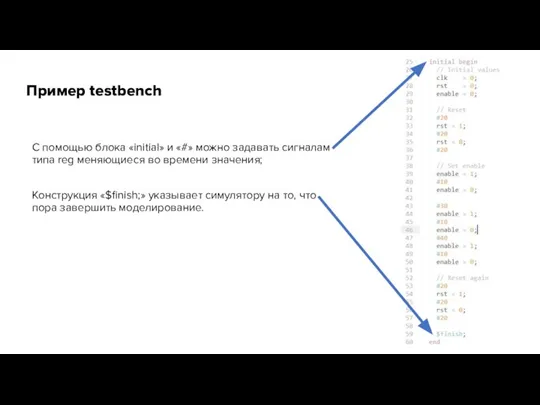

Слайд 66Пример testbench

С помощью блока «initial» и «#» можно задавать сигналам типа reg

меняющиеся во времени значения;

Конструкция «$finish;» указывает симулятору на то, что пора завершить моделирование.

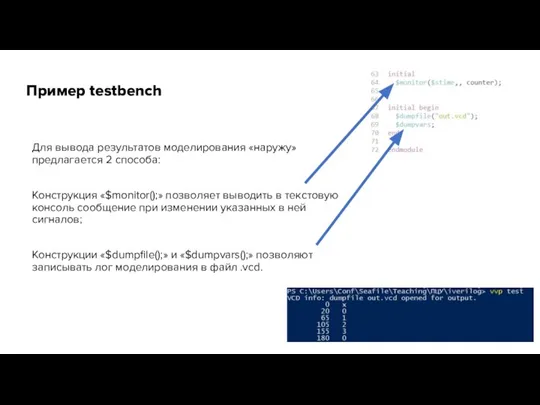

Слайд 67Пример testbench

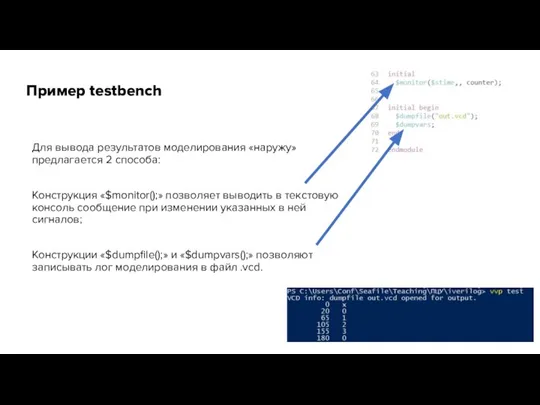

Для вывода результатов моделирования «наружу» предлагается 2 способа:

Конструкция «$monitor();» позволяет выводить

в текстовую консоль сообщение при изменении указанных в ней сигналов;

Конструкции «$dumpfile();» и «$dumpvars();» позволяют записывать лог моделирования в файл .vcd.

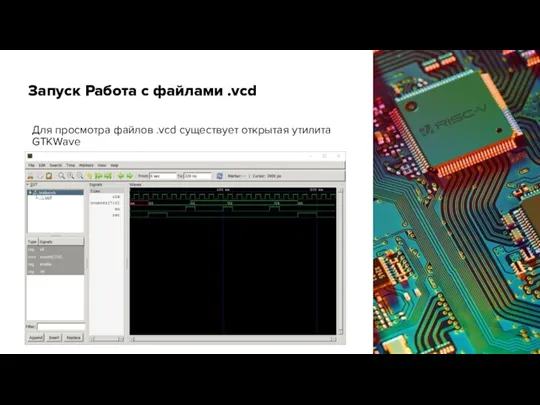

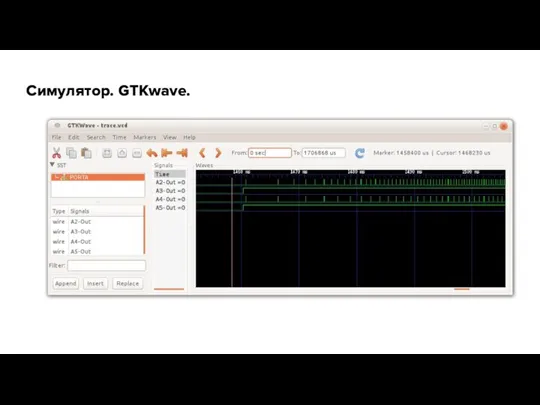

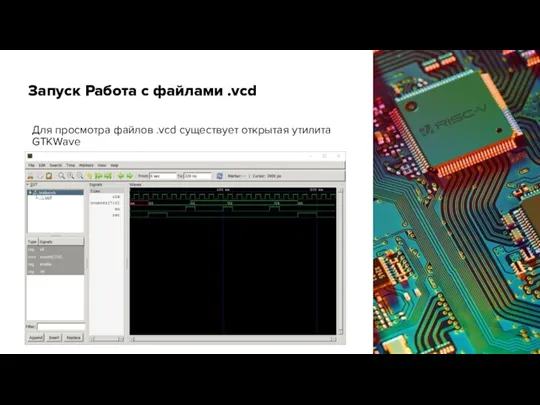

Слайд 68Запуск Работа с файлами .vcd

Для просмотра файлов .vcd существует открытая утилита GTKWave

Презентация к конспектуОткрытого комплексного занятияво второй младшей группеМДОУ детского сада №12 «Золотой Петушок»города

Презентация к конспектуОткрытого комплексного занятияво второй младшей группеМДОУ детского сада №12 «Золотой Петушок»города  Терраформирование

Терраформирование Своеобразие баллады ХХ века

Своеобразие баллады ХХ века Звіт про виховну роботу на кафедрі іноземних мов

Звіт про виховну роботу на кафедрі іноземних мов ИНФОРМАЦИОННОЕ ПРОСТРАНСТВО образовательного учреждения

ИНФОРМАЦИОННОЕ ПРОСТРАНСТВО образовательного учреждения Как формировать и развивать универсальные учебные действия у учащихся?

Как формировать и развивать универсальные учебные действия у учащихся? Устройства ввода графической информации

Устройства ввода графической информации 20140930_geo

20140930_geo «Веселый счет» С.Я. Маршак

«Веселый счет» С.Я. Маршак Метод проектов в начальной

Метод проектов в начальной Коммерческое предложение для toyota-shygys.kz

Коммерческое предложение для toyota-shygys.kz Интегрированный On-line конкурс рисунков и творческих работ, к Международному Дню 8-е Марта

Интегрированный On-line конкурс рисунков и творческих работ, к Международному Дню 8-е Марта Краны пролётного типа

Краны пролётного типа Древнерусское государство и общество

Древнерусское государство и общество Святитель Иов – первый Патриарх России

Святитель Иов – первый Патриарх России Экскурсия, выставка, Вернисаж

Экскурсия, выставка, Вернисаж Электронные тахеометры Leica TPS 1200+

Электронные тахеометры Leica TPS 1200+ ИНФОРМАТИКА

ИНФОРМАТИКА Презентация на тему Первобытное общество (10 класс)

Презентация на тему Первобытное общество (10 класс) Муниципального бюджетного общеобразовательного учреждения Политотдельской средней общеобразовательной школы Матвеево-Курганс

Муниципального бюджетного общеобразовательного учреждения Политотдельской средней общеобразовательной школы Матвеево-Курганс Презентация на тему Случайные события

Презентация на тему Случайные события  ИНФОРМАЦИЯ. ИНФОРМАТИКА.ИНФОРМАТИЗАЦИЯ.

ИНФОРМАЦИЯ. ИНФОРМАТИКА.ИНФОРМАТИЗАЦИЯ. ТАКАЯ ЖИЗНЬ ОПРЕДЕЛЯЕТСЯ БУДУЩИМ,

ТАКАЯ ЖИЗНЬ ОПРЕДЕЛЯЕТСЯ БУДУЩИМ, Роль технологии в современном мире

Роль технологии в современном мире Презентация к уроку по обществознанию _Правонаруше

Презентация к уроку по обществознанию _Правонаруше Псориаз

Псориаз МОУ «Богоявленская СОШ» Презентация к уроку русского языка в 6 классе Тема: « Правописание Н и НН в прилагательн

МОУ «Богоявленская СОШ» Презентация к уроку русского языка в 6 классе Тема: « Правописание Н и НН в прилагательн Горный поход. Приэльбрусье

Горный поход. Приэльбрусье