Слайд 2Правила:

1. любой алгоритм можно помещать в любой алгоблок

2. один и тот же

алгоритм можно помещать в разные алгоблоки, т.е. использовать многократно

Слайд 3Конфигурирование

В процессе конфигурирования для каждого входа каждого алгоблока задается источник сигнала. Каждый

вход алгоблока может находиться в одном из двух состояний:

1) связанном

2) свободном

Слайд 4Вход считается связанным, если он соединен с входами какого-либо алгоблока, в противном

случае вход считается свободным. Сигналы на свободных входах могут устанавливаться в виде:

1) констант

2) коэффициентов

Слайд 5Отличие между константами и коэффициентами заключается в возможности их изменения: константы могут

устанавливать и изменять только в режиме программирования; коэффициенты – как в режиме программирования, так и в процессе работы не выключая контроллер из контура управления.

Слайд 6Т.е. задача конфигурирования сводится к след.

3-х операциям:

1. определяется, должен ли каждый

вход алгоблока быть связанным или свободным.

2. Для связанных входов задается номер алгоблока и номер его выхода, с которым данный вход должен быть связан; для свободных входов задается, является ли сигнал на данном входе константой или коэффициентом.

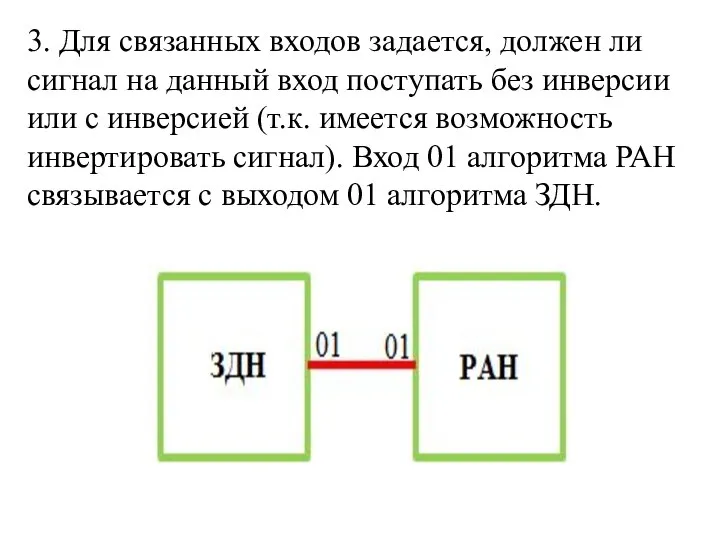

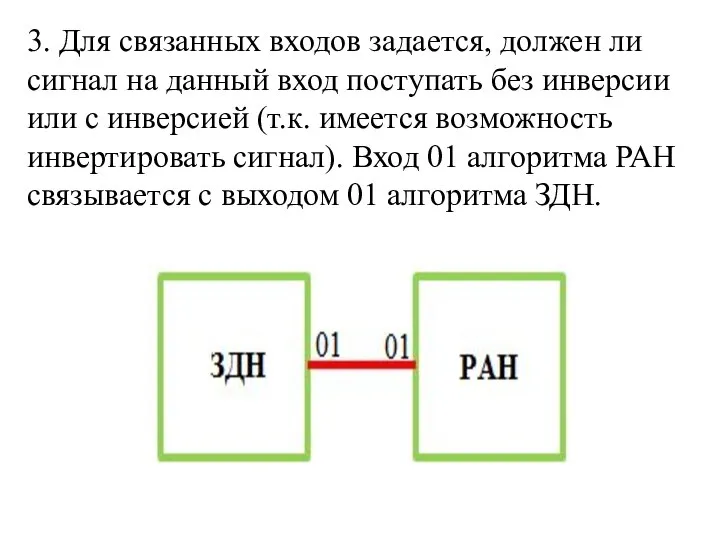

Слайд 73. Для связанных входов задается, должен ли сигнал на данный вход поступать

без инверсии или с инверсией (т.к. имеется возможность инвертировать сигнал). Вход 01 алгоритма РАН связывается с выходом 01 алгоритма ЗДН.

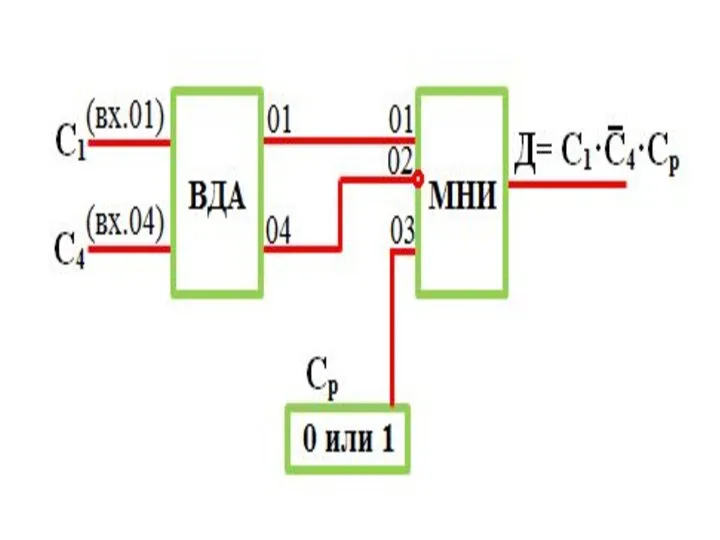

Слайд 8Для подключения к дискретным входам контроллера используется алгоритм ВДА (ввод дискретных сигналов

гр. А). Входы 01 и 02 алгоритма И (МНП) соединяются с выходами 01 и 04 алгоритма ВДА, а вход 03 МНИ оставляется свободным, причем на нем задается сигнал в виде коэффициента. Сигнал на входе 02 алгоритма МНИ инвертируется.

Слайд 10Аналоговые сигналы формируются на выходе таких алгоритмов как регуляторы, сумматоры, задатчики, интеграторы

и т.д. Несмотря на то, что на аналоговых входах и выходах контроллера сигнал меняется в диапазоне 0…100% на входе алгоблоков аналоговый сигнал может изменяться в более широком диапазоне 0…-199.9 до +199.9%.

Слайд 11Это позволяет например, складывать два числа, каждое из которых равно 90% и

на выходе сумматора получать правильный результат. Если результат каких-либо вычислений оказывается больше 199.9 или меньше -199.9, то сигнал на выходе алгоблока ограничивается значениями соответственно 199,9 % или -199,%.

Слайд 12Обратный счет и безударность

При решении задач автоматического регулирования возникает необходимость включать, выключать

или переключать контур регулирования безударно. Для безударного переключения в составе контура должны находиться алгоритмы, способные отслеживать требуемые сигналы. Такое отслеживание, обеспечивающее безударность, называется балансировкой.

Слайд 13В контроллере можно реализовать два вида балансировки – статическую и динамическую. При

статической балансировке отслеживаемый сигнал запоминается, при динамической балансировке после того, как контур выключается, отслеживаемый сигнал плавно уменьшается (по модулю) до нуля.

Слайд 14Вид балансировки зависит от используемых алгоритмов. Так интегратор выключает статическую балансировку, алгоритм

задания – любую из двух балансировок.

Сигнал, который необходимо отслеживать для обеспечения безударности, рассчитывается автоматически. Для такого расчёта используется процедура обратного счета, которая заключается в следующем:

Слайд 15Если цепочка алгоритмов, содержащая алгоритмы (т.е. алгоритмы, способные отслеживать и запоминать начальные

условия) отключена и сигнал на выходе Yо формируется каким-либо другим алгоритмом, все отключенные алгоритмы определяют, какой сигнал обратного счета Xос им нужно подать на свой вход, чтобы на выходе последнего алгоритма в отключенной цепочке после её включения сигнал был равен Yо.

Слайд 16Следящий алгоритм отслеживает сигнал Xос, рассчитанный алгоритм, включенным после следящего алгоритма. В

результате включение отключенной цепочки произойдет безударно.

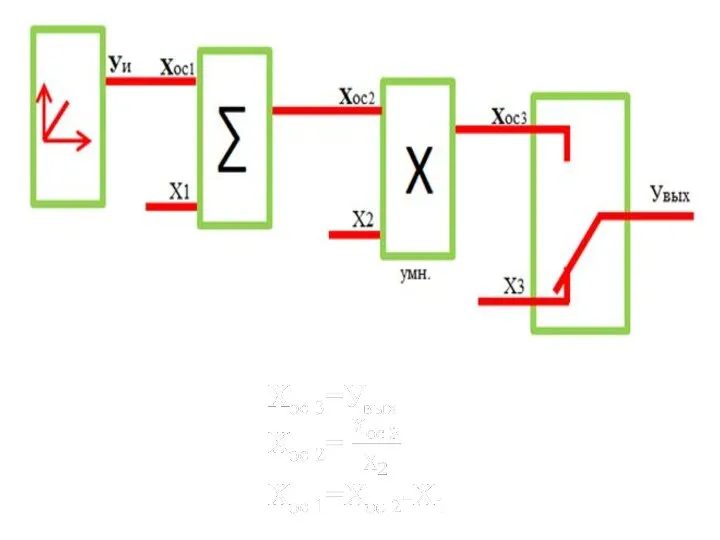

На рис. если цепочка алгоритмов отключается, каждый алгоритм переходит в режим обратного отсчета, в результате которого интегратор «заряжается» до величины Yи=(Yвых/X2)-X1. Очевидно, что когда отключенная цепь включается, начальное значение сигнала на выходе будет равно сигналу, предшествовавшему включению.

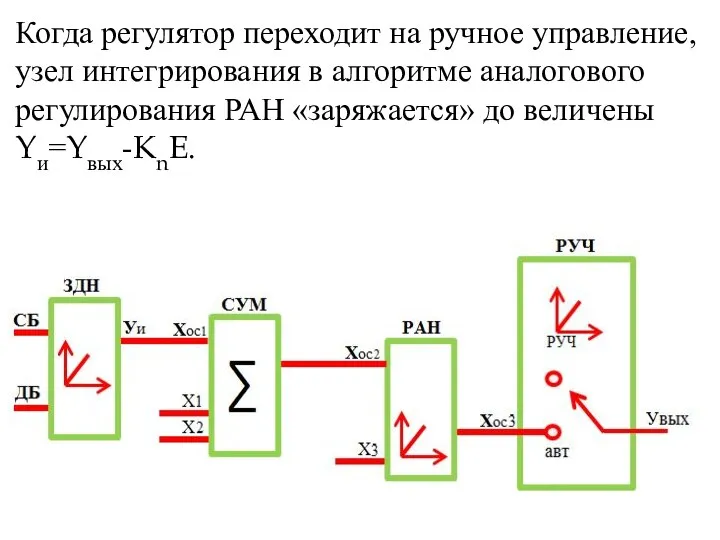

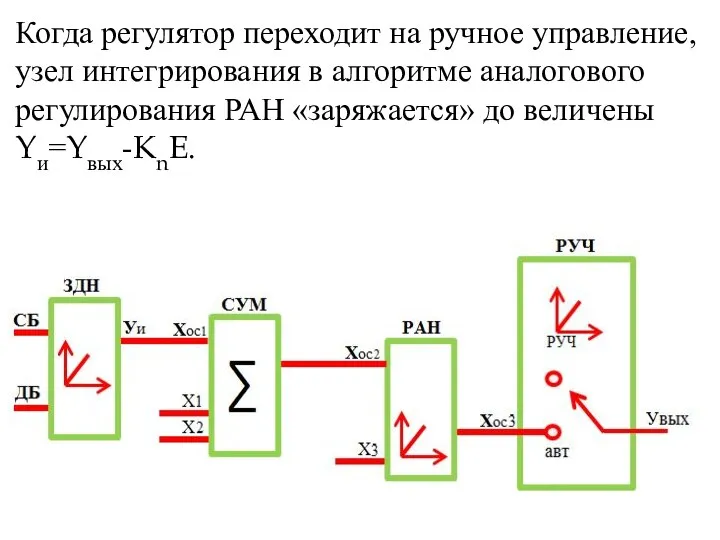

Слайд 18Когда регулятор переходит на ручное управление, узел интегрирования в алгоритме аналогового регулирования

РАН «заряжается» до величены Yи=Yвых-KnE.

Слайд 19Если в задатчике ЗДН балансировка отсутствует (СБ=ДБ=0), то переход на режим автоматического

управления произойдет безударно, при этом П и Д – части начального сигнала рассогласования = 0 (т.е. в первый момент после включения алгоритм РАН работает как И-регулятор).

Слайд 20Если же в алгоритме ЗДН включена статическая и динамическая балансировка, то в

ручном режиме не только «заряжается» интегральная ячейка алгоритма регулирования, но и узел задания «заряжается» до значения Yздн=X3-(X1+X2), интегрирование прекращается при отслеживании; а при включении интегрирование продолжается Е=0.

Слайд 21В этом случае после перехода на автоматический режим в первый момент установится

нулевое значение рассогласования. При статической балансировке (СБ=1) запомненное значение Уздн сохранится, при динамической балансировке (ДБ=1) сигнал Уздн начинает изменяться с пост. настраиваемой скоростью, пока не вернется к исходному (ранее установленному) значению.

Слайд 22Условия безударности

1. Если в отключенной цепи имеется алгоритм из группы следящих алгоритмов,

который в состоянии отслеживать сигнал обратного счета, необходимый для безударности, включение цепи происходит безударно.

Слайд 23К группе следящих относятся алгоритмы:

- аналоговые рег. РАН

- имп. РИН

- интегр. ИНТ

-

динамической балансировки ДИБ

- задания ЗДН, если у него включена СБ или ДБ

- ручного управления РУН, если он работает в ручном режиме.

Слайд 24Если на вход С поступает дискретный сигнал С=1, переключатель отключает интегратор, при

этом на входе Х1 переключателя формируется команда отключения вместе со значением начальных условий X1=Y2. Интегратор переходит в режим отключения, при этом интегрирование входного сигнала Х прекращается, а интегральная ячейка отслеживает сигнал Y1 т.е. Yи=Y1. В результате начальные условия для интегратора Y0=Y2=X2 и включение интегратора произойдет безударно.

IT Школа Samsung. Производственная гимнастика!

IT Школа Samsung. Производственная гимнастика! Разработка информационной панели (dashboard) ключевых показателей деятельности органов исполнительной власти субъекта РФ

Разработка информационной панели (dashboard) ключевых показателей деятельности органов исполнительной власти субъекта РФ Художники. База данных

Художники. База данных Платёжная система PayPal. История моей профессии

Платёжная система PayPal. История моей профессии Особенности алгоритма CDA в акциях

Особенности алгоритма CDA в акциях СМИ моей мечты

СМИ моей мечты История развития русских шрифтов

История развития русских шрифтов Безопасность личного пространства (соцсети)

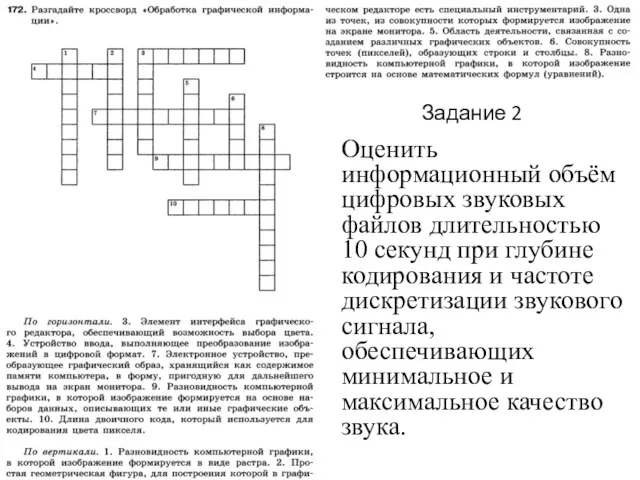

Безопасность личного пространства (соцсети) Кроссворд. Обработка графической информации

Кроссворд. Обработка графической информации Введение в информатику

Введение в информатику Обработка текстовой информации. Текстовый редактор

Обработка текстовой информации. Текстовый редактор Презентация отдела E-commerce

Презентация отдела E-commerce Электронные брошюры Навигатор для абитуриентов

Электронные брошюры Навигатор для абитуриентов Создание графических изображений

Создание графических изображений Captcha и recaptcha

Captcha и recaptcha Как воспользоваться электронной книгой. 1 - Виды форматов электронных книг 2- Программы для чтения электронных книг 3- Как скача

Как воспользоваться электронной книгой. 1 - Виды форматов электронных книг 2- Программы для чтения электронных книг 3- Как скача Вытынанки – увлекательное рукоделие

Вытынанки – увлекательное рукоделие Стратегия развития информационного общества

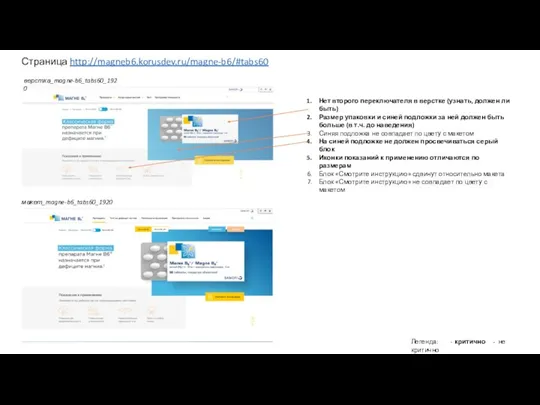

Стратегия развития информационного общества Расхождение верстки

Расхождение верстки Схема технологии обеспечения электронным талоном на проезд (ЭТ ФСС)

Схема технологии обеспечения электронным талоном на проезд (ЭТ ФСС) Создание web-сайта буктрейлеров литературы, рекомендованной лицеистам для чтения летом для школьной библиотеки

Создание web-сайта буктрейлеров литературы, рекомендованной лицеистам для чтения летом для школьной библиотеки экстремальное программирование

экстремальное программирование Работа с памятью

Работа с памятью 02_Методологии_разработки_ПО_Agile,_Waterfall,_и_другие

02_Методологии_разработки_ПО_Agile,_Waterfall,_и_другие Арбитраж. День 4

Арбитраж. День 4 Сборник Adobe Photoshop CS5 для начинающих

Сборник Adobe Photoshop CS5 для начинающих Сату сабағы

Сату сабағы Бизнес-информатика

Бизнес-информатика